1.引言

時序分析,也許是SI 分析中難度最大的一部分。我懷著滿腔的期許給Cadence 的資深工程師發了一封e-mail,希望能夠得到一份時序分析的案例,但是希望化作了泡影。資深工程師告訴我,他們還沒有能夠編寫一個具體的案例。於是,我不得不將我的期許轉化為自己研究並編寫一個具體的案例,與廣大PCB 工程師共享,令大彼天下PCB 寒士俱歡顏。既然有了共產主義的期許,自然就有了奮鬥的信念。

如果你覺得好,請你頂一下;如果你覺得爛,請你頂起來罵一下。

2.從什麼是時序電路談起

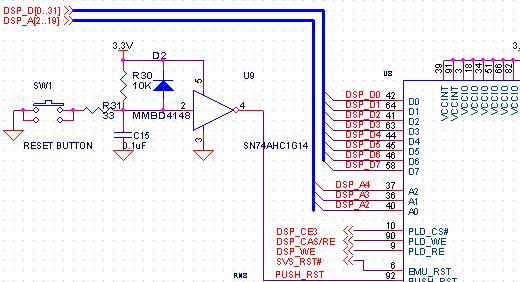

我的導師,一位誨人不倦的人類偉大靈魂工程師,當我將CPLD 連在了CPU 的數據、地址、讀寫和片選信號上,並企圖在CPLD 中自定義幾個寄存器使得這幾個寄存器相對於CPU 就好似非同步訪問的存儲空間時(如圖1),他迷惘了。他認為我應該將CPU 的時鐘輸出到CPLD,不然就無法做到非同步訪問CPLD 的時序。

圖1 CPLD 做非同步訪問存儲器

原來這個世界從第一天起就將時序電路定義錯了,它們定義為

y=f(x1,x2,…,xn,t1,t2,…,tn)

即函數值y 不僅與輸入有關,還與時鐘觸發條件有關,正是因為時鐘,才叫時序電路。

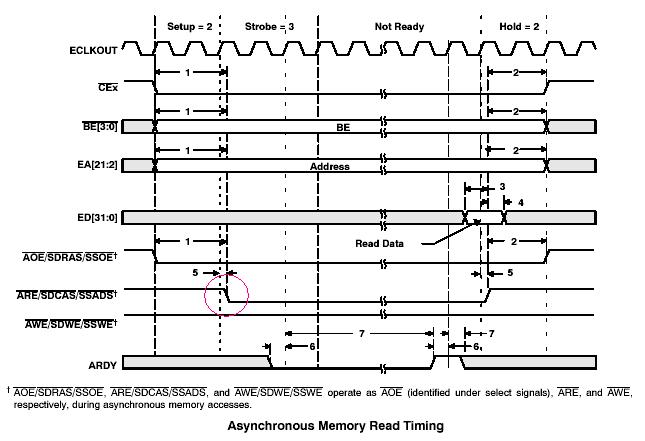

我要將這世界顛倒的黑都糾白了。為什麼只有時鐘能作觸發條件,做觸發條件的不一定只是時鐘。圖2 是TMS320C6713 這一DSP 的非同步存儲器讀定時。很顯然,在CPLD 中觸發其將寄存器中數據放入匯流排的觸發條件是讀信號(圖中畫紅線處觸發)。這個讀信號就成為二者之間的握手信號,在DSP 寫CPLD 的時候握手信號則是寫信號了。用CPLD 實現這個非同步存儲器的VHDL 程序如下:

re 定義為讀信號輸入,wr 定義為寫信號輸入,D_REG 定義為數據寄存器,data 是雙向的數據匯流排

process(re)

BEGIN

if(cs='0' and re=’0’) then

data<=D_ REG;

end if;

…

END PROCESS;

process(wr)

BEGIN

if(cs='0' and wr=’0’) then

D_REG <= data;

end if;

…

END PROCESS;

圖2 TMS320C6713 的非同步存儲器讀定時

當然在上例中如果將DSP 的時鐘輸入接入CPLD,則可以更好的完成這個電路時序之間的匹配。如果不接入,也同樣能通過編程改變DSP 的setup 和strobe 所佔用的時鐘周期數量來實現。

請記住:時鐘本質上只是一個觸發條件!跟其它的觸發條件沒有什麼兩樣!

在CPU 訪問SDRAM 時,握手信號即是時鐘。於是乎,用Cadence 來做定時分析就分為兩類:

1) 時鐘握手信號??同步

2) 其它握手信號??非同步

----------------------------------------------------------------------------------------------------------------------

請注意:此部分我的“時序電路”定義不嚴格,列位看觀能明白我所言“觸發”和“握手”之意既可。我仍然贊成我的導師將時鐘接入CPLD。

3. 同步時序分析

列位看觀,這個具體的案例將舉的例子還是TMS320C6713,它將要訪問MT48LC4M32B2這樣一個SDRAM。首先介紹SDRAM的幾個概念:

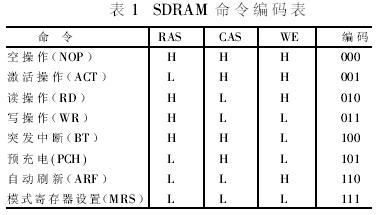

SDRAM的所有輸入和輸出都與系統時鐘上升沿同步,並且由輸入信號RAS、CAS、WE組合產生SDRAM控制命令,其基本的控制命令如表1所示。關於SDRAM 的操作有很多,如兩個BANK的乒乓讀寫方式、突髮式讀寫時的中斷操作、低能耗方式的進入等等,我們可以在MT48LC4M32B2數據手冊中看到各種操作時的時序圖。

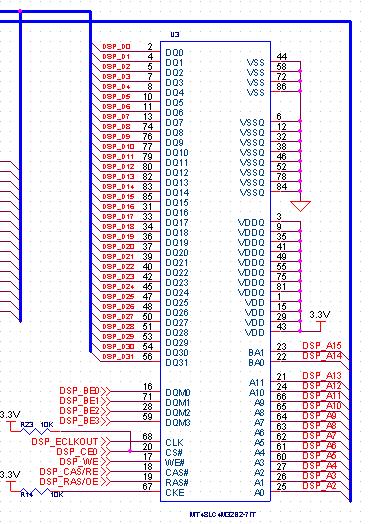

MT48LC4M32B2分為四個BANK,地址線的最高兩位即為BANK的片選。其行地址為A0-A11,列地址為A0-A7,數據匯流排寬為32bit,需要在64ms內刷新4,096行。MT48LC4M32B2與TMS320C6713的連接如圖,圖中的CKE為SDRAM的時鐘使能,被PULLUP。

(列位看觀,今天談到這裡先。)

連載待續 版權所有

--------------------------------------------------------------------------------------

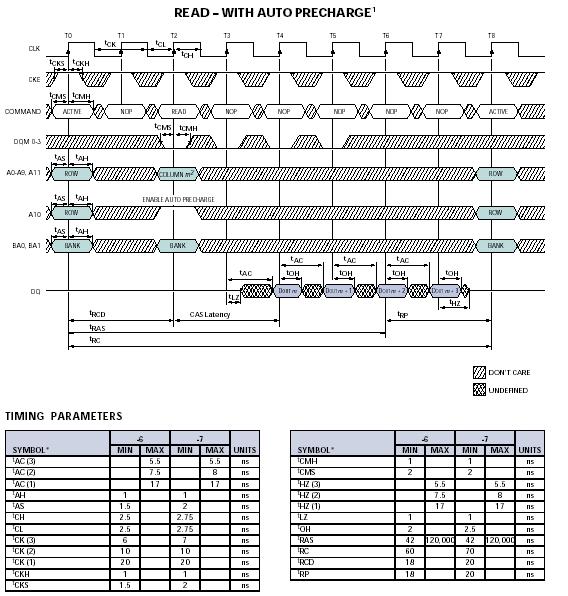

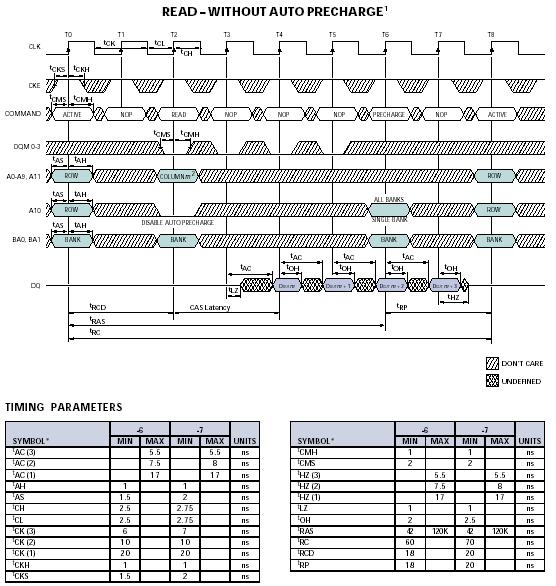

①圖4和圖5分別是自動預充電和無自動預充電時讀SDRAM的時序,可以看出A10的不同。

圖3 TMS320C6713與SDRAM

圖4 自動預充電讀時序

圖5 無自動預充電讀時序

[admin via 研發互助社區 ] Cadence 高速PCB的時序分析(1)已經有2499次圍觀

http://cocdig.com/docs/show-post-44233.html