PART 1:

1. 軟體 14.1版本較 13.6版本功能提升了,bug也減少了,但是還是存在一些 bug,功能方面還有待進一步完善。

(Cadence在每個季度都會發布軟體補丁程序QSR,用戶可以在Sourcelink網站註冊並預定QSR光碟,您會在一周內直接收到該光碟;在這期間,Cadence還會根據實際情況,不斷發布最新的臨時升級、補丁程序,Cadence當地的技術支持人員會主動、儘快地為用戶進行安裝。在功能方面,Cadence在世界各地擁有強大的研發隊伍,以向客戶提供更多、更好的功能。PSD14.2版本很快將交付用戶,功能更強的PSD15.0不久也將發布。)

2. cadence 公司目前在華東地區現只有 1名技術支持,在現場技術支持方面有待加強力量。

(Cadence今年在中國正式註冊成立了全資公司,服務隊伍也從去年的30人增加到近90人,並在上海、北京成立了High Speed Technical Centre等部門,在各地包括華東地區都增加了技術支持,因此我們相信,在新的一年裡,我們的客戶會得到更多更方便的支持)

3. 隨著 cadence 軟體在公司的日益推廣使用,我們希望能加強軟體使用方面的培訓力度。

(感謝貴公司對Cadence公司的支持!如果貴公司有軟體培訓方面的需求,可直接和當地的客戶經理聯繫。)

PART 2:

CADENCE BUG 主要有:

1. 在CONCEPT HDL 中移動器件,會出現器件庫可以被分拆。

(這個問題是14.0中出現的BUG,14.1版已解決此問題。請各位升級)

2. 從CONCEPT HDL 打包時經常在沒有報出錯誤的情況下,不能打包成功.

(Concept HDL打包不成功時一定會報錯。這種情況可能是因為路徑錯誤,請仔細檢查)

3. 從CONCEPT HDL 打包到ALLEGRO更新PCB時不能打包成功. 但往空的PCB打包時能成功, ECO常有問題.

(在個別情況下,會出現這種情況,出錯信息為“Net name already exists”。今年2月份的補丁盤已包含此補丁程序,請用戶聯繫Cadence工程師進行升級或到下面地址下載補丁程序、安裝:

ftp://ftp.cadence.com/patches/PSD141/allegro/algroF2B14.10-s018wint.exe

ftp://ftp.cadence.com/patches/PSD141/allegro/algroBase14.10-s056wint.exe )

4. CCT 中有時不能單獨對電源、地 FANOUT。

(是否沒有指定Power Nets選項?如果指定了還有此問題,用戶最好能提供一個可以重複出現此問題的例子,以便查找原因)

5. BOARDQUEST 對網路拓撲的提取常常不能成功。 不如以前的版本靈活、方便,在模型有“問題”時,可以用預設模型。

(Boardquest 為Cadence較早版本。用戶最好能提供一個可以重複出現此問題的例子,以便查找原因)

6. ALLEGRO 中大面積布銅時,有時會出現在對銅皮分配了網路的情況下,布出死銅(銅皮不與任何網路相連,無花盤). 大面積布銅時,經常出現不應該有的裂縫,布銅的效果不是最優的。

(用戶最好能提供一個可以重複出現此問題的例子,以便查找原因)

7. ALLEGRO 中程序自動、無告警退出, 致使設計丟失的現象,發生的頻率比以前的版本高。

(出現這種情況,主要是操作系統方面的原因,ALLEGRO要求在英文NT或WINDOWS 2000下使用.在中文WINDOWS 2000下,出錯概略提高許多。事實上,設計人員應充分使用Allegro的Autosave功能,以避免各種情況下引起的數據丟失)

8. ALLEGRO出光繪時,常報出根本不存在的錯誤而不能輸出光繪文件。

(根據經驗,此類問題一般是TOP,BOTTOM層光繪有問題。最好能提供一個可以重複出現此問題的例子及系統給出的錯誤信息,以便查找原因。)

9. ALLEGRO 的功能還有改善的空間。 如: 修線時,自動採用原線寬; 替換功能、推擠功能、加測試點功能可以做得更加友好,等等。

(即將發布的14.2版本對這些大部分問題做了很多改進。下面列出14.2版的一些主要改進:

Save Design to 14.0

Database Write Locks

View Schemes

DBdoctor

Plane Rat

Place Manual UI Auto-Hide

Direct Select of Alternate Symbol

Quickplace Options

Via Shoving

Dynamic Slide Phase II

Vertex Dynamic Bubble Options

Smart Start on Line Width

Highlight All Pins on Net During add connect

Cadence Design Systems, Inc

Net Name Added to Control Panel

Purge Vias

EXTRACT Name Change

Graphical Enhancements During Dynamics

Text Printing/Stick

Append to File Option Added to Reports

SPECCTRA-Like Zoom

Viewer Plus Enhancements

New Board Wizard

CPM and CDS_SITE Support

Scald EOL

IPC356 and Allegro-to-DXF Performance Improvement

TestPrep PCR Fixes

New Features in Allegro Studio (PCB)

Miscellaneous Category)

10. 生成料單時,有PPT 表的元器件的 Part Name 在料單中出現兩次。

(14.1版已解決此問題)

PART 3:

我們在使用CADENCE的過程中遇到的問題基本歸結為:

1 無論哪個版本都經常出現自動退出,提示為非法操作,然後不能存檔,自動退出。(ALLEGRO)

(參考PART2問題7的答案。提示:Allegro在異常退出時,會在當前設計目錄下產生一個後綴為sav的文件。用Allegro打開該文件,另存為brd文件即可)

2 版本13.6中出現過生成的GERBER文件在避讓不能的SHAPE時,出現半圓,即不能完全避讓。還出現過個別完全不避讓的狀況 。

(題目意思不太清楚。請使用最新版本測試)

3 版本14.1很多機器不能正常安裝。

(請參考軟體安裝手冊,並注意安裝過程中系統給出的提示。一般出現這種問題都是操作系統問題或放火牆、防病毒軟體引起)

4 在添加IBIS模型時,MPC8260總是不能自動加上去,已經和工程師聯繫過多次。

(可能是因為該IBIS模型不是標準格式,請使用器件商提供的標準模型)

PART 4:

1在ALLEGRO中,編輯焊盤時,經常會出現“執行程序錯誤”而退出程序,且沒有備份文件,導致之前的工作白費。

(此問題14.1已經解決,而且同樣與操作系統有關)

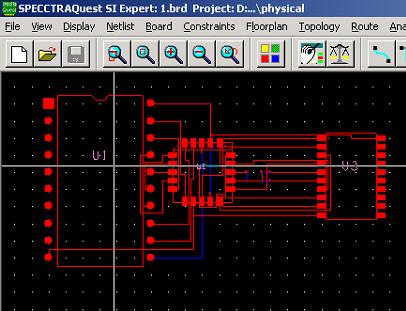

2 在從自動布線器(SPECCTRA)建軍回到ALLEGRO后,輸出表層的線、孔就與器件成為一個整體,移動器件時,線、孔就附在上面一起移動。

(實際上,這個功能是Cadence應大多數用戶要求而添加上的,主要是為了方便移動器件的時候 fanout 后的引腿和 via 能跟著一起移動。如果你實在不願意這麼做,可以執行下面這個Skill程序解決,以後版本將會有選項供用戶選擇:

; The following Skill routine will remove invisible

; properties from CLINES and VIAS.

; The intent of this Skill program is to provide

; users with the ability of deleting the invisible

; properties that SPECCTRA/SPIF puts on. This will allow the moving

; of symbols without the attached clines/vias once the

; design is returned from SPECCTRA if the fanouts were originally

; put in during an Allegro session.

;

; To install: Copy del_cline_prop.il to any directory defined

; within your setSkillPath in your

; allegro.ilinit. Add a "load("del_cline_prop.il")"

; statement to your allegro.ilinit.

;

; To execute: Within the Allegro editor type "dprop" or

; "del cline props". This routine should

; only take seconds to complete.

;

; Deficiencies: This routine does not allow for Window or

; Group selection.

;

; WARRANTIES: NONE. THIS PROGRAM WAS WRITTEN AS "SHAREWARE" AND IS AVAILABLE AS IS

; AND MAY NOT WORK AS ADVERTISED IN ALL ENVIRONMENTS. THERE IS NO

; SUPPORT FOR THIS PROGRAM.

;

; Delete invisible cline/via properties.

;

axlCmdRegister( "dprop" 'delete_cline_prop)

axlCmdRegister( "del cline props" 'delete_cline_prop)

(defun delete_cline_prop ()

;; Set the Find Filter to Select only clines

(axlSetFindFilter ?enabled (list "CLINES" "VIAS")

?onButtons (list "CLINES" "VIAS"))

;; Select all clines

(axlClearSelSet)

(axlAddSelectAll) ;select all clines and vias

(setq clineSet (axlGetSelSet))

(axlDBDeleteProp clineSet "SYMBOL_ETCH") ;Remove the property

(axlClearSelSet) ;unselect everything

)

3 建原理圖軟體中,圖形編輯和SYMBOLS中的設置不一致,SYMBOLS中的任何設置變動都會使圖形的編輯無效。

(問題表達不太清楚,請直接聯繫支持工程師)

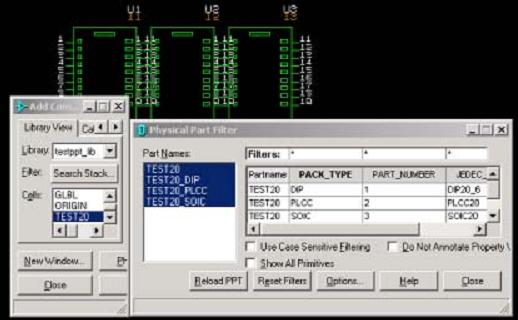

4 建庫中,在一個器件對應三個或以上的封裝時,PACKAGE中所建的三個封裝在SYMBOLS中並沒有全部出現以供SYMBOLS圖形選擇。

(不會有這樣的問題。問題有些含糊:建庫時,在 Part developer 中,對symbol 的設定本來就沒有 package 的圖形選擇;如果是在原理圖裡添加 Symbol遇到這個問題,如果要選擇封裝形式,需要用 Physical 方式,請確認操作是否正確,下面就是多個封裝同時顯示的例子:)

5 原理圖建庫的PART-TABLE表的屬性中COMP-NAME的值與CELL名相同時,不能夠封裝,封裝時出錯。

(請提供該元件的庫,以便於我們查找原因)

6 原理圖庫建庫屬性中,PART-NUMBER 的值不能 NULL,否則向 SPECCTRA 轉換時出錯。

(的確如此,PART_NUMBER的值不能為空,解決辦法:要麼刪除PART_NUMBER屬性,要麼把值加上)

7 在 ALLEGRO 中滑鼠顯示為無窮大是可以的。但在 SIGNOISE 的界面下,設為無窮大時就顯示不出來了。

(14.1 版本已解決此問題。對早期版本可以在命令行執行 :set pcb_cursor=infinite 即可;另外,Specctraquest 沒有提供象 Allegro 一樣的User Reference 功能,可以在命令行執行 enved 調用該功能界面,然後進行設置)

PART 5:

1.用貼片焊盤(type=single)做成的package,用tools\padstack\modify design padstack...編輯,發現type變成了blind/buried。為什麼會這樣?

(這是軟體顯示上的小漏洞,但是絲毫不影響使用,焊盤還是事實上的single)

2.修改過焊盤后以同名保存(替換了原來的焊盤),但是用tools\padstack\modify design padstack...檢查用該焊盤做的package,發現仍舊是老焊盤,而事實上任何目錄中老焊盤都不存在了。既然allegro是要到pad_path中調用焊盤的,為什麼會出現這種情況?

(修改完焊盤之後, 需要update pad才能更新,因為Allegro是把相關的數據都納入到brd文件集中管理的)

3.打開padstack editor就會出現這樣的提示:pad_designer:Can't open journal file。於是新做的焊盤無法保存,提示:failed to open file '#T001632.tmp'。

(請檢查系統環境變數設置是否正確;另外所有路徑都不能使用漢字)

4.AELLGRO中竟然無UNDO、REDO這種常用FUNC,讓人非常費解!!!

(15.0版本將增加Undo、Redo功能)

[admin via 研發互助社區 ] Cadence 用戶問題解答已經有8909次圍觀

http://cocdig.com/docs/show-post-44413.html