由於系統時鐘頻率和上升時間的增長,信號完整性設計變得越來越重要。不幸的是,絕大多數數字電路設計者並沒意識到信號完整性問題的重要性,或者是直到設計的最後階段才初步認識到。

本篇介紹了高速數字硬體電路設計中信號完整性在通常設計的影響。這包括特徵阻抗控制、終端匹配、電源和地平面、信號布線和串擾等問題。掌握這些知識,對一個數字電路設計者而言,可以在電路設計的早期,就注意到潛在可能的信號完整性問題,還可以幫助設計則在設計中盡量避免信號完整性對設計性能的影響。

儘管,信號完整性一直以來都是硬體工程師必備的設計經驗中的一項,但是在數字電路設計中長期被忽略。在低速邏輯電路設計時代,由於信號完整性相關的問題很少出現,因此對信號完整性的考慮本認為是浪費效率。然而近幾年隨著時鐘率和上升時間的增長,信號完整性分析的必要性和設計也在增長。不幸的是,大多數設計者並沒有注意到,而仍然在設計中很少去考慮信號完整性的問題。

現代數字電路可以高達 GHz 頻率並且上升時間在50ps 以內。在這樣的速率下,在PCB設計走線上的疏忽即使是一個英尺,而由此造成的電壓、時延和介面問題將不僅僅局限在這一根線上,還將會影響的全板及相鄰的板。

這個問題在混合電路中尤為嚴重。例如,考慮到在一個系統中有高性能的ADC 到數字化接收模擬信號。散布在ADC 器件的數字輸出埠上的能量可能很容易就達到130dB(10,000,000,000,000 倍)比模擬輸入埠。在ADC 數字埠上的任何雜訊。設計中的信號完整性並不是什麼神秘莫測的過程。對於在設計的早期意識到可能潛在的問題是很關鍵的,同時可以有效避免由此在後期造成的問題。本篇討論了一些關鍵的信號完整性挑戰及處理他們的方法。

確保信號完整性:

1、隔離

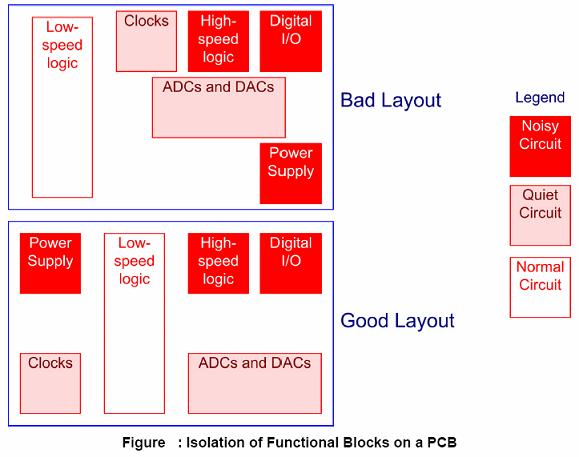

一塊PCB板上的元器件有各種各樣的邊值(edge rates)和各種雜訊差異。對改善SI最直接的方式就是依據器件的邊值和靈敏度,通過PCB板上元器件的物理隔離來實現。下圖是一個實例。在例子中,供電電源、數字I/O埠和高速邏輯這些對時鐘和

數據轉換電路的高危險電路將被特別考慮。第一個布局中放置時鐘和數據轉換器在相鄰於雜訊器件的附近。雜訊將會耦合到敏感電路及降低他們的性能。第二個布局做了有效的電路隔離將有利於系統設計的信號完整性。

2、阻抗、反射及終端匹配

阻抗控制和終端匹配是高速電路設計中的基本問題。通常每個電路設計中射頻電路均被認為是最重要的部分,然而一些比射頻更高頻率的數字電路設計反而忽視了阻抗和終端匹配。

由於阻抗失配產生的幾種對數字電路致命的影響,參見下圖:

a.數字信號將會在接收設備輸入端和發射設備的輸出端間造成反射。反射信號被彈回並且沿著線的兩端傳播直到最後被完全吸收。

b.反射信號造成信號在通過傳輸線的響鈴效應,響鈴將影響電壓和信號時延和信號的完全惡化。

c.失配信號路徑可能導致信號對環境的輻射。

由阻抗不匹配引起的問題可以通過終端電阻降到最小。終端電阻通常是在靠近接收端的信號線上放置一到兩個分立器件,簡單的做法就是串接小的電阻。

終端電阻限制了信號上升時間及吸收了部分反射的能量。值得注意的是利用阻抗匹配並不能完全消除破壞性因素。然而認真的選用合適的器件,終端阻抗可以很有效的控制信號的完整性。

並不是所有的信號線都需要阻抗控制,在一些諸如緊湊型 PCI 規格要求中的特徵阻抗和終端阻抗特性。

對於別的沒有阻抗控制規範要求的其他標準以及設計者並沒有特意關注的。最終的標準可能發生變化從一個應用到另一個應用中。因此需要考慮信號線的長度(相關與延遲Td)以及信號上升時間(Tr)。通用的對阻抗控制規則是Td(延遲)應大於Tr 的1/6。

3、內電層及內電層分割

在電流環路設計中會被數字電路設計者忽視的因素,包括對單端信號在兩個門電路間傳送的考慮(如下圖)。從門A 流向門B 的電流環路,然後再從地平面返回到門A。

上圖中將會出現兩個潛在的問題:

a、A 和B 兩點間地平面需要被連接通過一個低阻抗的通路

如果地平面間連接了較大的阻抗,在地平面引腳間將會出現電壓倒灌。這就必將會導致所有器件的信號幅值的失真並且疊加輸入雜訊。

b、電流迴流環的面積應儘可能的小

環路好比天線。通常說話,一種更大環路面積將會增大了環路輻射和傳導的機會。每一個電路設計者都希望迴流電流都可直接沿著信號線,這樣就最小的環路面積。

用大面積接地可以同時解決以上兩個問題。大面積接地可以提供所有接地點間小的阻抗,同時允許返回電流盡量直接沿著信號線返回。

在 PCB 設計者中一個常見的錯誤是在地電層上打過孔和開槽。下圖顯示了當一條信號線在一個開過槽的地電層上的電流流向。迴路電流將被迫繞過開槽,這就必然會產生一個大的環流迴路。

通常而言,在地電源平面上是不可以開槽的。然而,在一些不可避免要開槽的場合,PCB 設計者必須首先確定在開槽的區域沒有信號迴路經過。同樣的規則也適用於混合信號電路 PCB 板中除非用到多個地層。特別是在高性能ADC 電路中可以利用分離模擬信號、數字信號及時鐘電路的地層有效的減少信號間的干擾。需要再次強調的,在一些不可避免要開槽的場合,PCB 設計者必須首先確定在開槽的區域沒有信號迴路經過。

在帶有一個鏡像差異的電源層中也應注意層間區域的面積(如下圖)。在板卡的邊緣存在電源平面層對地平面層的輻射效應。從邊沿泄漏的電磁能量將破壞臨近的板卡。見下圖a。適當的減少電源平面層的面積(見下圖b),以至於地平面層在一定的區域內交疊。這將減少電磁泄漏對鄰近板卡的影響。

[admin via 研發互助社區 ] 高速電路設計中信號完整性分析已經有16027次圍觀

http://cocdig.com/docs/show-post-44123.html