列位看觀,在上一次的連載中,我們介紹了什麼是時序電路,時序分析的兩種分類(同步和非同步),並講述了一些關於SDRAM 的基本概念。這一次的連載中,我們將介紹什麼是定時問題,怎樣保證接收端的建立和保持時間。

信號經過傳輸線到達接收端之後,必須滿足建立時間和保持時間這兩個時序參數,它們由接收器本身的特性決定,可以從晶元的數據手冊中獲得。時鐘沿有效時,要求數據必須已經存在一段時間,這就是器件需要的建立時間(Setup Time);而時鐘邊沿觸發之後,數據還必須要繼續保持一段時間,以便能穩定的讀取,這就是器件需要的保持時間(Hold Time)。數據信號在時鐘沿觸發前後持續的時間必須分別都要超過建立和保持時間,否則接收端可能不能正確地採樣到數據,setup/hold 時間是時序問題產生的根源。

我們分析DSP 讀取SDRAM 數據時怎樣才能滿足DSP 的建立和保持時間。不管列位看觀在哪篇文獻里看到了哪樣的定時數學公式,請你將它遺忘。我們從來不需要死記硬背任何的數學公式,我們要的是聰明的分析頭腦。

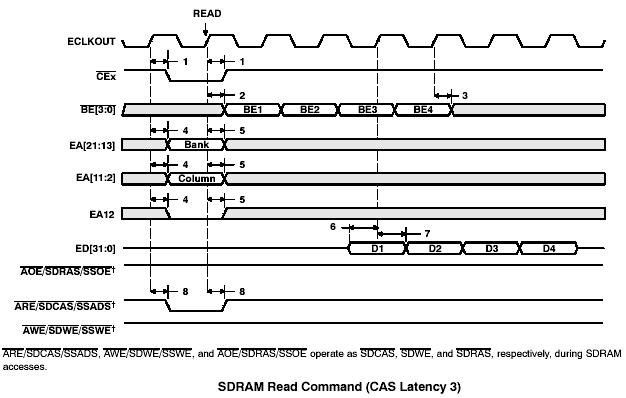

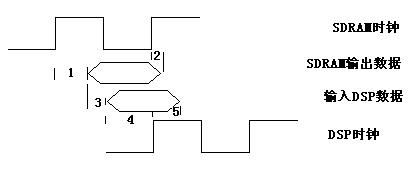

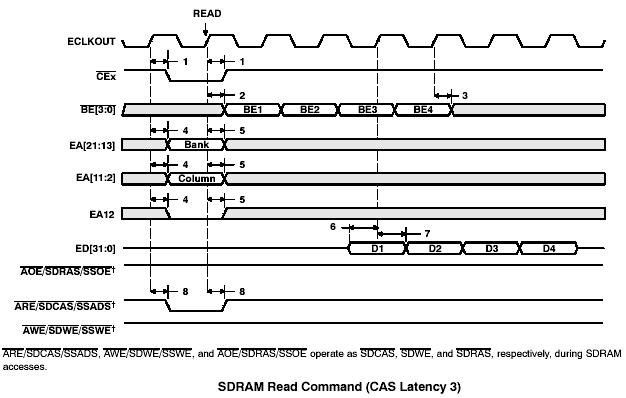

圖6 為DSP 讀取SDRAM 數據的定時,很明顯,DSP 在ECLKOUT 的上升沿採樣數據,圖6 中的時間6 和時間7 分別是建立和保持時間,查TMS320C6713 數據手冊獲知建立時間最小為1.5ns,保持時間最小為2.5ns。

圖6 TMS320C6713 讀取SDRAM 數據的時序

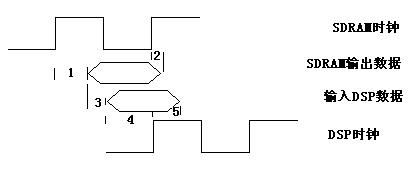

在DSP 讀取SDRAM 數據時,SDRAM 在第一個時鐘的上升沿后將數據放入匯流排,而DSP 總是在接下來的一個時鐘上升沿觸發時採樣數據,如圖7 所示,我們先假設SDRAM與DSP 的時鐘是完全同步的。

顯然欲滿足DSP 的setup/hold,必須有:

T

4 > DSP setup time;T

5 > DSP hold time

②即T

clk-T

1-T

3 > DSP setup time; T

2+T

3 > DSP hold time

②請列位看觀不要將此看做公式,我反對公式,贊成直觀和推理。

圖7 DSP 讀取SDRAM 數據

很顯然,我們弄明白了T

1 、T

2和T

3的含義,就完全明白了setup/hold時間的需求!

什麼是

T1,直觀而言,就是源端時鐘上升沿有效到其在匯流排上放入的數據達到參考電平時的時間,這就是傳說中的Tco。確定Tco的方法是在源端輸出的末端直接相連一個測量負載,最常見的是50歐姆的電阻或者30pF的電容,然後測量負載上的信號電壓達到一定電平的時間,這個電平稱為測量電壓(Vms),一般是信號高電平的一半。T

3則是指在源端到第2個時鐘周期上升沿后,數據還能準確地在數據線上保持多長時間(過了下文所說的First Switch Delay就不叫還在準確地保持)。很多文獻中將T

1和T

3混為一談,分別稱為T

co-max和T

co-min,實際上是不準確的。

T

3 是什麼呢?列位看觀一看就明白,不準確地說就是源端的數據到接收端數據之間的時間,那麼這個時間具體是什麼呢?就是傳說中的飛行時間T

flight,注意T

flight 不同於傳播時延,後者僅由傳輸線長和傳輸速度決定,而前者還受接收端負載大小的影響。T

flight 分為最小飛行時間T

flight-min 和最大飛行時間T

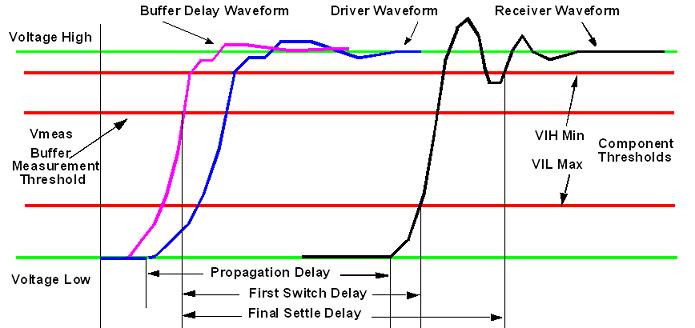

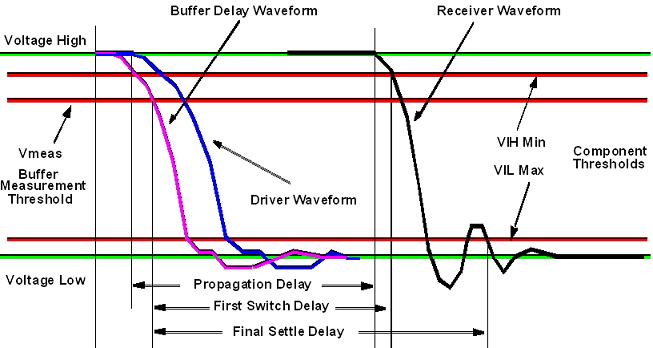

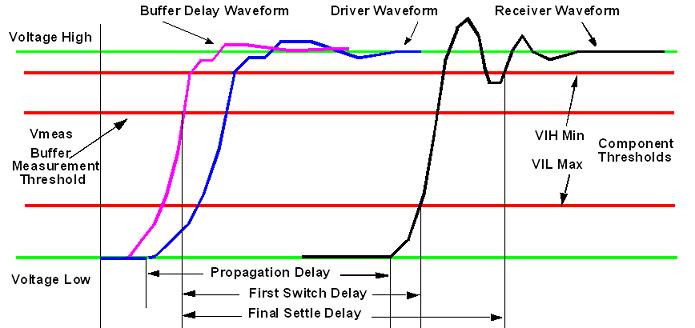

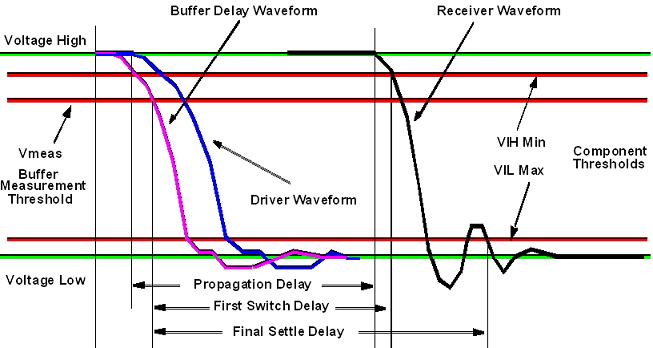

flight-max,在Cadence 軟體中,T

flight-min 定義為First Switch Delay,T

flight-max 定義為Final Settle Delay,而這個定義,我認為,遠遠要超過飛行時間來得準確,讓我們熱情地歌頌它。如圖8,假設數據從0 到1(上升沿),First Switch Delay指的是從這一刻起,接收端就不能準確地判斷原來的0 了;而Final Settle Delay 這是指接收端只有從這一刻起才能準確地判斷新來的1,雖然信號以前已經在1 上面跑過了一回(但是它又振蕩回去了)。在數據的下降沿,如圖9,看觀們可以自己推理得出什麼是First Switch Delay 和Final Settle Delay。很顯然了,First Switch Delay 會被用在保持時間的計算中,而Final Settle Delay 則會用於建立時間的計算中。

圖8 數據上升沿

圖9 數據下降沿

於是乎,要滿足T

clk-T

1-T

3 > DSP setup time 變成了要滿足:

T

clk-T

co-max-T

flight-max > DSP setup time

而要滿足T2+T3 > DSP hold time 就變成了要滿足:

T

co-min+T

flight-min > DSP hold time

以上皆是基於SDRAM 的時鐘與DSP 的時鐘完全同步的假設,如果二者的時鐘不同步,情況又當如何?我們假設SDRAM 的時鐘比DSP 的早T

skew,很顯然這個早(也就是DSP採樣數據的晚)對於DSP 建立時間的獲取是有利的(DSP 可以爭取到更多的建立時間),而對保持時間是不利的。

有利就是說建立時間條件中的“>”更容易被滿足,怎樣才能更加容易滿足,顯然是將T

skew 加入方程左邊,於是最終版的T

clk-T

co-max-T

flight-max > DSP setup time 應為

T

clk-T

co-max-T

flight-max+T

skew > DSP setup time

而保持時間中的“>”更難被滿足,於是T

co-min+T

flight-min > DSP setup time 最終變成

T

co-min+T

flight-min -T

skew > DSP hold time

在本例的DSP 與SDRAM 互連中,SDRAM 的時鐘由DSP 輸出,SDRAM 時鐘晚於DSP,於是本例應該滿足的條件則是:

T

clk-

Tco-max-T

flight-max -T

skew > DSP setup time

T

co-min+T

flight-min +T

skew > DSP hold time

經過一段痛苦的推理過程后,一切變得豁然開朗。請記住:在判斷是該+還是該- Tskew時,請使用是否“有利於”等式成立法則!記得江core 提出過“三個有利於”,考研的時候被它搞暈了。

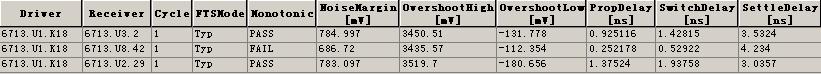

我們學會了這樣的推理過程后,以後面對任何情況的CPU 與RAM 時序,都可以分析出來。表2 列出了TMS320C6713 和MT48LC4M32B2-7 的參數。

表2 TMS320C6713 和MT48LC4M32B2-7 的參數 | 參數 | 時間(ns) |

| MT48LC4M32B2 Tco-min | 2.5 |

| MT48LC4M32B2 Tco-max | 5.5 |

| TMS320C6713 setup time | 1.5 |

| TMS320C6713 hold time | 2.5 |

下面我們將要面對真實的Cadence 了,我們看看怎樣模擬獲得準確的T

flight-max 和T

flight-min。很抱歉,Cadence 中不計其數的設置搞得你我暈頭轉向,讓我們無情地批判它。

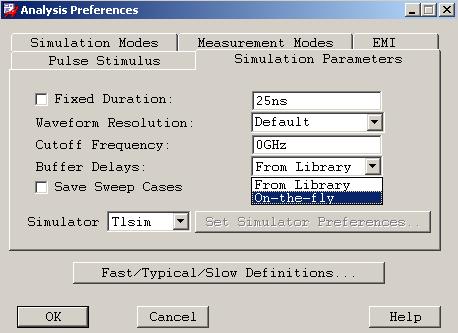

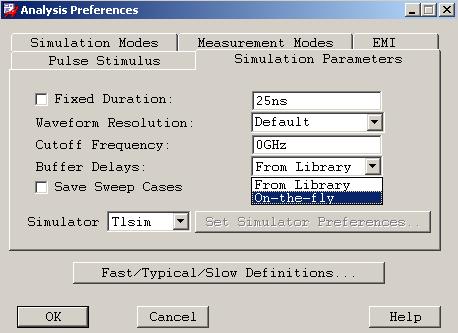

第一個設置:請在SigXplorer 中將Buffer Delay 設置為On-the-fly(圖10),如果你有興趣可以將Waveform Resolution 設置地更小,以便追求更大的模擬精度。Default 指的是周期的1/100。

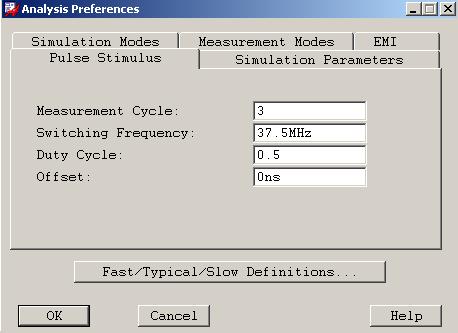

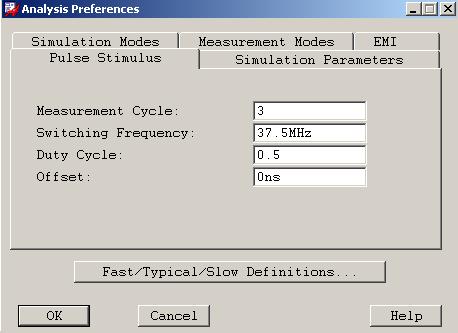

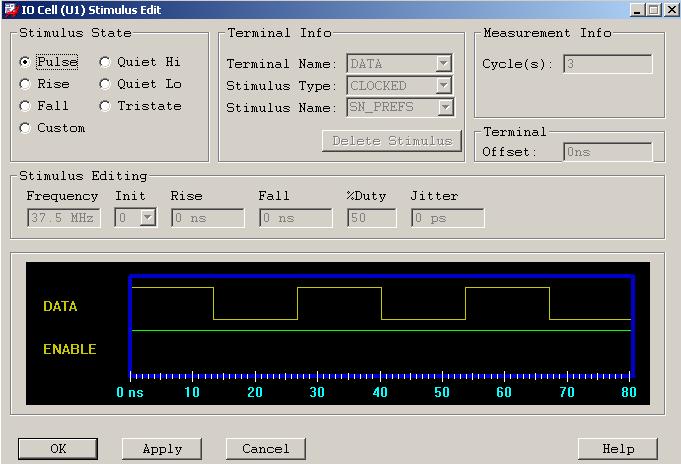

第二個設置:設置脈衝的Switching Frequency 為數據線的頻率(也即時鐘頻率的一半,見圖11)。

圖10 設置Buffer Delay 為On-the-fly

圖11 設置Switching Frequency 為數據線的頻率

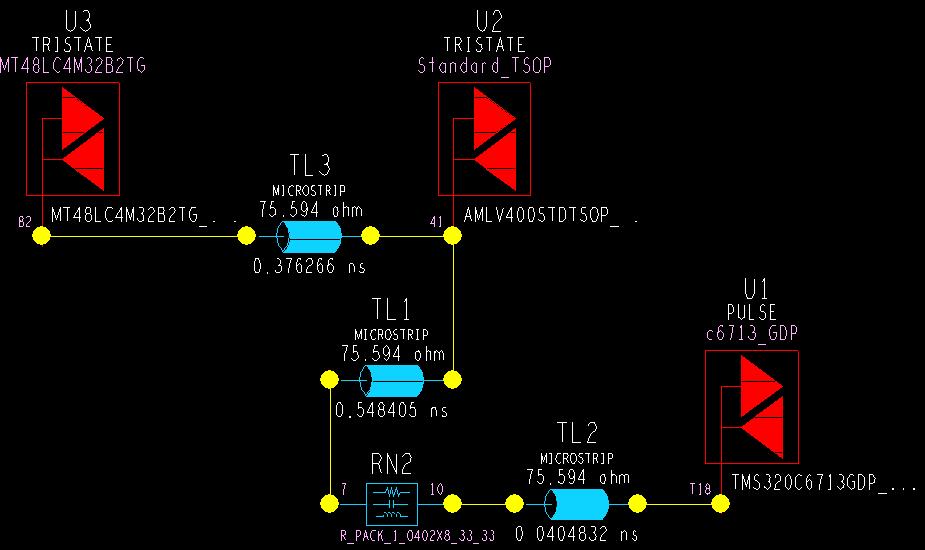

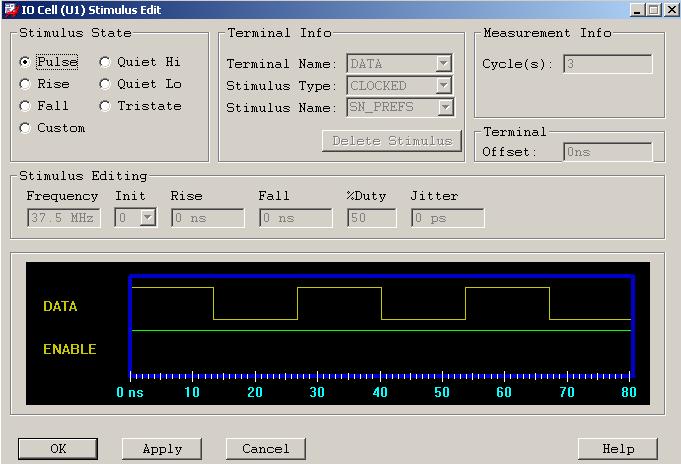

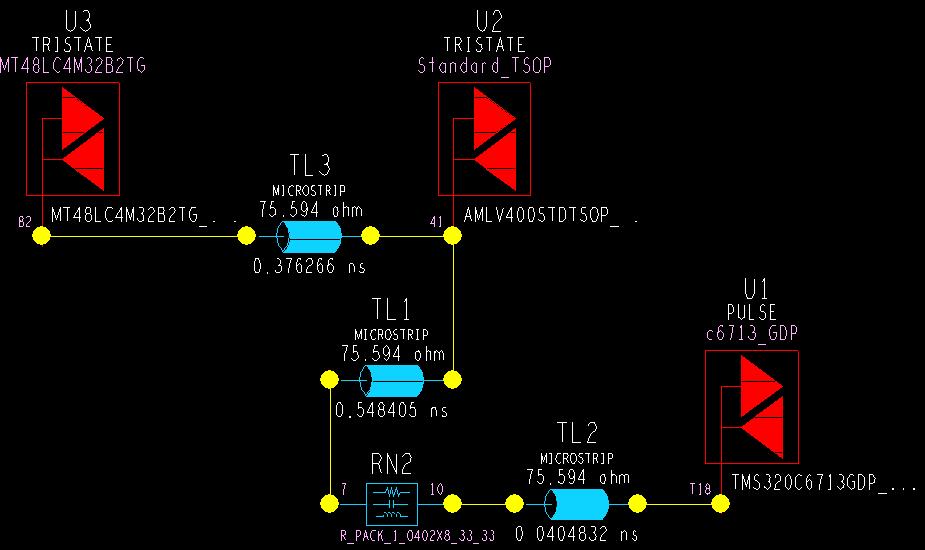

第三個設置:設置驅動端脈衝,如圖13,在提取的如圖12 的拓樸圖中點擊驅動端U1,在彈出的窗口中設置其為pulse。

圖12 提取的拓樸

圖13 設置驅動端脈衝

現在可以點擊

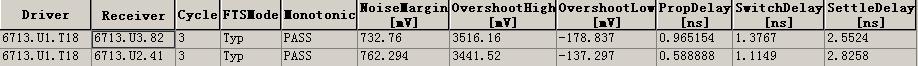

開始模擬,得到了下面的模擬結果

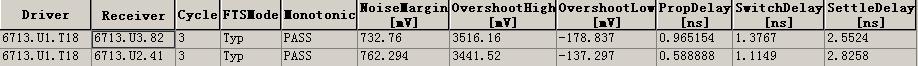

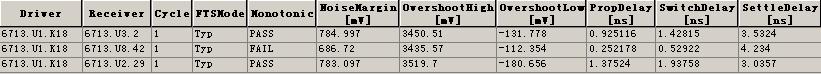

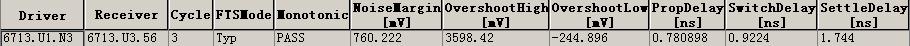

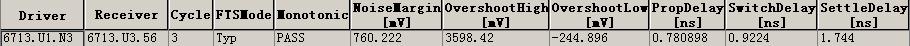

由於32 根數據線上的拓樸並非完全一樣,我們將拓樸相同的歸為一組BUS,共獲得三組BUS 的

Tflight-max 和T

flight-min 然後取所有中的最大和最小值。對另外兩組數據BUS 執行同樣的模擬后,獲得的結論如下:

從三組結論中我們也看出這樣一個事實,DSP 帶越少的負載,

Tflight-max 和T

flight-min 越接近於傳播時延,這顯然是合理的。

T

flight-min = 0.9224ns

T

flight-max = 3.5324ns

而時間偏移Tskew 則為0.8625ns,Tclk = 1/37.5mhz = 26.6667ns

T

clk-T

co-max-

Tflight-max -T

skew =26.6667-3.5324-5.5-0.8625=16.7717ns

16.7717ns >1.5ns(DSP setup time)顯然成立!

T

co-min+T

flight-min +T

skew =0.9224+2.5+0.8625=4.2849ns

4.2849ns >2.5ns(DSP hold time) 顯然成立!

我們可以預測以當前的拓樸和負載情況,SDRAM 的數據頻率跑到37.5mhz 是可以滿足DSP 的定時要求的。上面兩式好像滿足的非常輕鬆,可以,事實上,我們給了Tclk 一個較大的值,既讓數據運行在了較低的頻率上。如果我們降低Tclk,相應的T

flight-max 則很可能會增加,要滿足建立時間的難度要大一些。

我們驚訝地發現,欲保持時間似乎與工作頻率無關!是的,事實正是如此!(我們不否認T

flight-min 會隨著工作頻率有微小的波動。)

另外,請記住:

讀寫都要滿足setup/hold!在DSP 寫SDRAM 時,要滿足SDRAM 的建立和保持時間!

讓我們進入規則設置環節!規則,你如此可怕,以致於學習你需要費盡心機,肝腸寸斷;規則,你如此可愛,以致於精通了你就可以在PCB 界瀟洒地仗劍江湖,馳騁沙場;規則,你如此可恨,以致於不懂你,一切地原理圖、PCB 繪製過程都是在重複地做著傻瓜的遊戲。接下來,讓我們踐踏你,解剖你,玩死你。

(精彩內容,請聽下回分解。列位看觀,今天談到這裡先。)

連載待續 版權所有

21cnbao@21cn.com

宋寶華

2004-10-20

開始模擬,得到了下面的模擬結果

開始模擬,得到了下面的模擬結果