0 引言

功放進入了數字時代。數字功放的關鍵部分集成電路已經達到了較高水半,如TDA8902J數字功放有效地降低了信號間的干擾、可實現高保真。雖然核心技術解決了,但印製線路板(PCB)布線不當, 也很難達到理想的效果。筆者在TDA8902J數字功放的PCB設計過程中總結了一點經驗, 現就PCB設計應遵守的布線原則及抗干擾設計要求與電磁兼容性要求作簡要分析介紹。

1.PCB的布局及布線原則

PCB提供了功放電路元器件之間的電氣連接,要使功放電路獲得最佳性能,元器件的布局及印製導線的布設是關鍵。

1.1 布局原則

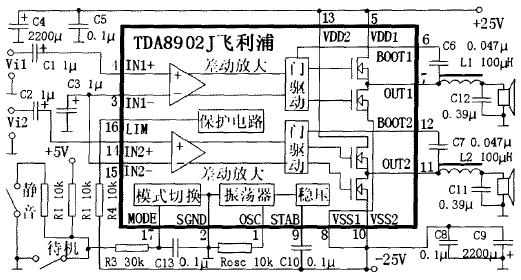

(1)數字功放的功率管工作在開關狀態,頻率高、電流大,且與電源部分靠得近, 而該功放(如圖1—1)由於採用開關電源(圖中未畫出)供電,干擾和紋波係數較大,因此,元器件在PCB上排列的位置要考慮抗電磁干擾,各部件之間的引線要盡量短。在布局上,要把模擬信號、數字信號和雜訊源這三部分合理地分開,使相互間的耦合為最小。即要求與LM4651⑩ 腳相連的模擬輸入部分與其它數字部分要分開, 電源輸入、去耦濾波元件,也要與數字處理部分分開, 此外,還要考慮電源變壓器的方向性, 使之對電路的輻射最小。

(2)元件在排列時應按輸出濾波器、H-橋電路、比較器、振蕩發生器、電壓放大器的次序, 如果各級交叉排列, 很容易相互影響,出現自激或吸收。

(3)對電磁場輻射較強的元件(如L3,L2)、和對電磁感應較敏感的元件(R1、C1,R5、C3), 應加以屏蔽,或遠離電磁場輻射源,以減少干擾。

(4)儘可能縮短高頻元件(如R5、C3)之間的連線, 設法減少它們的分佈參數和相互間的電磁干擾。易受干擾的元器件不能相互挨得太近, 輸入和輸出元件應盡量遠離。

(5)有些元器件或導線之間有較高的電位差, 應加大它們之間的距離, 以免放電出現意外短路。如TDA8902J的⑤ 、⑦ 腳:LH4652的① 、

③ 腳走線不宜相距太近。帶高電壓的元器件(如電源開關)應盡量布置在調試時手不易觸及的地方。

1.2 布線原則

(1)輸入輸出端(如R8、L1)用的導線應盡量避免相鄰平行,最好加線間地線,以免發生反饋耦合。

(2)各級走線應儘可能短,元件應盡量靠攏,大信號、高阻抗走線更要注意。如R11、C18的走線應儘可能短,音頻的輸入(C1 、R1)輸出(L1、L2)線也不宜長,否則易感應交流信號。

(3)導線的最小寬度主要由導線與絕緣基板間的粘附強度和流過它們的電流值決定。當銅箔厚度為0.05mm、寬度為1—15mm時,通過2A 的電流,溫度不會高於3℃ 。該功放可選0.5~5mm導線寬度。導線的最小間距主要由最壞情況下的線間絕緣電阻和擊穿電壓決定,可使間距小至5~8mm。

(4)印製導線拐彎處一般取圓弧形,而直角或夾角在高頻電路中會影響電氣性能。圖1—2(a)(b)(c)為三種拐角線的形式, 圖(C)採用45°外斜切面拐角線的傳輸性能和反射性能要優於其它兩種拐角線。圓弧的拐角線的性能要比這三種走線形式要好, 但是弧度的刻劃對制板的工藝要求比較高,會增加生產成本,該功放採用45°外斜切面拐角走線能滿足設計要求。

2.抗干擾設計措施

PCB的抗干擾設計針對不同電路有不同的要求,以下從三個方面討論該功放的PCB抗干擾設計措施。

2.1電源線設計

在直流電源迴路中,負載的變化會引起電源雜訊。根據PCB 電流的大小,盡量加粗電源線寬度,減少環路電阻。該功放電路LM4651L部

分電源的走線,導線寬度為1.5 mm便可滿足要求, 而在LM4652部分則要求3~5mm。同時使電源線和地線的走向和數據傳遞的方向一致,

這樣有助於增強抗雜訊能力。

2.2地線設計

地線比電源線更重要。克服電磁干擾,最主要的手段是地線的設計。地線的布線特別講究,通常採用單點接地法。模擬地、數字地和大功率器件地分開, 最後都彙集到電源地。該功放地線結構有系統地、機殼地、數字地和模擬地等。地線的設計原則是:

(1)數字地與模擬地分開。該功放既有邏輯電路又有線性電路,應使它們盡量分開,分別與電源端地線相連,並儘可能加大線性電路的接地面積。模擬音頻的地應盡量採用單點並聯接地。

(2)接地線應盡量加粗。若接地線很細。接地電位則隨電流的變化而變化,致使功放電路信號電平不穩,抗雜訊性能變壞。通常使地線能通過三倍的電流。該功放接地線應在3 ~6mm 以上。

(3)正確選擇單點接地與多點接地。該功放的模擬部分, 工作頻率低,它的布線和器件間的電感影響較小,而接地電路形成的環流對干擾影響較大,因而應採用單點接地。而在數字部分工作頻率大於10MHz時,地線阻抗變得很大,此時應盡量降低地線阻抗, 就近多點接地。當工作頻率在1—10MHz時,如果採用單點接地,其地線長度不應超過波長的1/20,否則應採用多點接地法。該功放數字部分雖然開關頻率為125kHz,但由於諧波的影響,採用多點接地更好。

(4)將接地線構成閉環路。數字功放的PCB,將接地線設計成閉環路可以明顯地提高抗雜訊能力。其原因在於:電路中耗電元件多,因受接地線粗細的限制,會在地線上產生較大的電位差,引起抗雜訊能力下降,若將接地構成環路,則會縮小電位差值,提高功放電路的抗雜訊能力。

2.3 信號線的設計

與PCB以外的弱信號相連時,通常採用屏蔽電纜。對於高頻和數字信號,屏蔽電纜兩端都接地。該功放模擬音頻信號用的屏蔽電纜,採用一端接地為好。而PCB 中的信號走線應盡量短並避開干擾源。

3.電磁兼容性(EMC)設計

一個簡單的電磁干擾模型由三部分組成, 如圖3—1所示。該功放含有開關電源和大功率、大電流驅動電路以及含有微弱模擬信號電路與高精度A/D 變換電路的系統,電磁干擾不可避免。EMC設計的目的是使功放既能抑制各種外來的干擾,同時又能減少本身對其它電子設備的電磁干擾。

3.1 PCB設計中的EMC措施

該功放注意了不同的布局區域,使專用零伏線、電源線的走線寬度≥ 1mm, 電源與地呈“井” 字形分佈,分佈線電流達到了均衡,並為模擬電路專門提供一根零伏線。為減少線間串擾,增加了印刷線條間距,並安插了幾根零伏線作為線間隔離。PCB的插頭也多安排二根零伏線作為線間隔離。特別注意了電流流通中的導線環路尺寸。

3.2配套於PCB的開關電源的EMC

電源在向功放供電的同時,也將雜訊加到了電路中。該功放電路的信號輸入、振蕩及控制部分最容易受外界雜訊的干擾。電網上的強幹擾通過電源進入電路,電路中的模擬信號最容易受到來自電源的干擾。該電源對電網的傳導騷擾及輻射騷擾是非線性流和初級電路中功率晶體管外殼與散熱器之間的耦合在電源輸入端產生的共模雜訊。

該電源對開關電壓波形進行了修整,在晶體管與散熱器之間加裝了帶屏蔽層的絕緣墊片,在市電輸入端加接了互感濾波器,並減小了環

路面積,在次級整流迴路中使用的軟恢復二極體上並聯了聚酯薄膜電容,因而使開關電壓波形得到了很大的改善。

3.3傳輸線的EMC

同軸電纜有較好的抗電磁干擾能力。該功放信號線所用同軸電纜為美國的AUDIOOUEST(線聖), 採用單端接地,為磁感應減小了環路

電流,使磁場屏蔽性能增強。

4.結束語

基於TDA8902J的數字功放, 功率大、熱損耗小、音質好、體積小,通過對其PCB 進行電磁兼容設計后,音質更好、信噪比更高、抗干

擾能力也明顯增強, 可應用於很多音頻設備中,如音效卡、有源音箱、汽車音響等,具有廣闊的前景。

[admin via 研發互助社區 ] 基於TDA8902J的數字功放PCB的設計已經有2162次圍觀

http://cocdig.com/docs/show-post-44307.html