1、IBIS模型

隨著數字系統性能的不斷提升,信號輸出的轉換速度也越來越快,在信號完整性分析中,不能簡單的認為這些高速轉換的信號是純粹的數字信號,還必須考慮到它們的模擬行為。為了在PCB進行生產前進行精確的信號完整性模擬並解決設計中存在的問題,要求建立能描述器件I/O特性的模型。這樣,Intel最初提出了IBIS的概念,IBIS就是I/O BufferInformation Specification的縮寫。

為了制定統一的IBIS格式,EDA公司、IC供應商和最終用戶成立了一個IBIS格式制定委員會,IBIS公開論壇也隨之誕生。在1993年,格式制定委員會推出了IBIS的第一個標準Version 1.0,以後不斷對其進行修訂,現在的版本是1999年公布的Version 3.2, 這一標準已經得到了EIA的認可,被定義為ANSI/EIA-656-A標準。每一個新的版本都會加入一些新的內容,但這些新內容都只是一個IBIS模型文件中的可選項目而不是必須項目,這就保證了IBIS模型的向後兼容性能。

現在,已經有幾十個EDA公司成為IBIS公開論壇的成員,支持IBIS的EDA公司提供不同器件的IBIS模型以及軟體模擬工具。有越來越多的半導體廠商開始提供自己產品的IBIS模型。

2、IBIS與SPICE的比較

SPICE作為一種通用的電路模擬語言,最早由加州大學伯克利分校發明。SPICE模型是對電路中實際的物理結構進行描述。由於其精確性和多功能性,已經成為電子電路模擬的標準語言。SPICE模型目前有兩個主要的版本:HSPICE和PSPICE,HSPICE主要應用於集成電路設計,而PSPICE主要應用於PCB板和系統級的設計。

採用SPICE模型在PCB板級進行SI分析時,需要集成電路設計者和製造商提供能詳細準確的描述集成電路I/O單元子電路的SPICE模型和半導體特性的製造參數。由於這些資料通常都屬於設計者和製造商的知識產權和機密,所以只有較少的半導體製造商會在提供晶元產品的同時提供相應的SPICE模型。SPICE模型的分析精度主要取決於模型參數的來源(即數據的精確性),以及模型方程式的適用範圍。而模型方程式與各種不同的數字模擬器相結合時也可能會影響分析的精度。有的半導體生產者在向外界提供SPICE模型時,常常會對一些涉及到知識產權的部分進行‘清理’,這樣也會導致模擬結果的不準確。

IBIS模型不對電路的具體結構進行描述,而只是採用I/V和V/t表的形式來描述數字集成電路I/O單元和引腳的特性。半導體廠商很容易在不透露自己的知識產權的同時為客戶提供這種模型。

IBIS模型的分析精度主要取決於I/V和V/T表的數據點數和數據的精確度。由於基於IBIS模型的PCB板級模擬採用查表計算,因而計算量較小,通常只有相應的SPICE模型的1/10到1/100。用它進行模擬的速度要比用SPICE模型快很多。隨著電路板的設計越來越複雜,使用SPICE模型模擬會花去很長的時間,而使用IBIS模型使得對整個電路板上的系統進行模擬成為可能。雖然IBIS模型沒有SPECE模型那麼精確,但對於系統級分析而言已經是完全足夠了。

使用IBIS模型的另外一個優點就是,很多的IBIS模型都是由實際的器件得到,這樣,一旦有了完全的IBIS數據,那麼模擬得到的數據就與實際的器件有了直接的關係。

總之,由於IBIS模型的方便,快捷,以及具有必要的精確度,越來越多的半導體廠商都願意向客戶免費提供自己產品的IBIS模型。

由於目前還沒有一種統一的模型來完成所有的PCB板級信號完整性分析,因此在高速數字PCB板設計中,需要混合各種模型來最大程度地建立關鍵信號和敏感信號的傳輸模型。

對於分立的無源器件,可以尋求廠家提供的SPICE模型,或者通過實驗測量直接建立並使用簡化的SPICE模型。對於關鍵的數字集成電路,則必須尋求廠家提供的IBIS模型。目前大多數集成電路設計和製造商都能夠通過web網站或其它方式在提供晶元的同時提供所需的IBIS模型。對於非關鍵的集成電路,若無法得到廠家的IBIS模型,還可以依據晶元引腳的功能選用相似的或預設的IBIS模型。當然,也可以通過實驗測量來建立簡化的IBIS模型。對於PCB板上的傳輸線,在進行信號完整性預分析及解空間分析時可採用簡化的傳輸線SPICE模型,而在布線后的分析中則需要依據實際的版圖設計使用完整的傳輸線SPICE模型。

3、IBIS模型的構成

一個IBIS文件包括了從行為上模擬一個器件的輸入、輸出和I/O緩衝器所需要的數據,它以ASCII的格式保存。IBIS文件中的數據被用來構成一個模型,這個模型可以用來對印刷電路板進行信號完整性模擬和時序分析。進行這些模擬所需的最基本的信息是一個緩衝器的I/V參數和開關參數(輸出電壓與時間的關係)。要注意的是,IBIS本身只是一種文件格式,它說明在一個標準的IBIS文件中如何記錄一個晶元的驅動器和接收器的不同參數,但並不說明這些被記錄的數據如何使用,這些參數要由使用IBIS模型的工具來讀取。

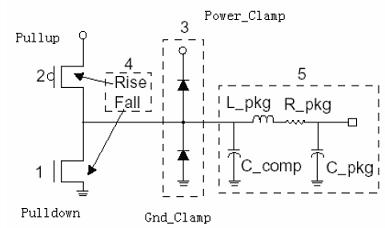

IBIS模型是以元件為中心的,也就是說,一個IBIS文件允許你模擬整個的一個元件,而不僅僅是一個特定的輸入、輸出或I/O緩衝器。因而,除了器件緩衝器的電學特性參數以外,IBIS文件還包括了器件的管腳信息以及器件封裝的電學參數。從Version 1.1開始,就定義了一個IBIS模型文件的最基本的組成元素為I/V數據表、開關信息和封裝信息(圖1)。

圖1 IBIS模型的基本組成元素

圖中,模塊2 Pullup和模塊1 PullDown表現了標準輸出緩衝器的上拉和下拉晶體管,用直流I/V數據表來描述它們的行為。模塊3中的Power_Clamp和Gnd_Clamp是靜電放電或鉗位二極體,也是用直流I/V數據表來描述的。模塊4在IBIS文件中是Ramp參數,表示輸出從一個邏輯狀態轉換到另一個邏輯狀態,用dV/dt來描述某一特定阻性負載下輸出波形的上升沿和下降沿。模塊5描述的是體電容和封裝寄生參數,其中C_comp是硅晶元電容,它是不包括封裝參數的總的輸出電容_L_pkg、R_pkg和C_pkg分別是由封裝帶來的寄生電感、寄生電阻和寄生電容。如果描述的僅僅是輸入管腳的IBIS模型,則只由模塊3和模塊5兩部分組成即可。

IBIS規範要求的I/V曲線的範圍是Vcc到(2*Vcc),制定這一電壓範圍的原因是,由全反射所引起的過沖理論上的最大值是兩倍的信號擺幅。Gnd_Clamp的I/V曲線範圍定義為-Vcc到Vcc,而Power_Clamp的I/V曲線範圍是0到(2*Vcc)。要注意的是,Pullup和Power_Clamp在IBIS文件中的電壓Vtable為Vcc-Voutput。

[Pulldown]

|

| Voltage I(typ) I(min) I(max)

|

-5.0V -40.0m -34.0m -45.0m

-4.0V -39.0m -33.0m -43.0m

| …

0.0V 0.0m 0.0m 0.0m

| …

5.0V 40.0m 34.0m 45.0m

10.0V 45.0m 4 0.0m 4 9.0m

|

[Pullup] | Note: Vtable=Vcc -Voutput

|

Voltage I(typ) I(min) I(max)

-5.0V 32.0m 30.0m 35.0m

-4.0V 3 1.0m 2 9.0m 33.0m

| …

0.0V 0.0m 0.0m 0.0m

| …

5.0V -32.0m -30.0m -35.0m

10.0V -38.0m -35.0m -40.0m

|

[GND C1amp]

|

| Voltage I(typ) I(min) I(max)

|

-5.0V -390 0.0m -3800.0m -4000.0m

-0.7V -80.0m -75.0m -85.0m

-0.6V -22.0m -20.0m -25.0m

-0.5V -2.4m -2.0m -2.9m

-0.4V 0.0m 0.0m 0.0m

5.0V 0.0m 0.0m 0.0m

|

[POWER Clamp] | Note:Vtable=Vcc—Voutput

|

| Voltage I(typ) I(min) I(max)

|

-5.0V 4450.0m NA NA

-0.7V 95.0m NA NA

-0.6V 23.0m NA NA

-0.5V 2.4m NA NA

-0.4V 0.0m NA NA

0.0V 0.0m NA NA

Ramp參數表示了緩衝器的上升和下降時間,Ramp中的dV是緩衝器輸出電壓由20%變化到80%間的差值。這一參數只計入了晶元電容C_comp的影響,而不考慮封裝寄生參數的影響。有時也用dV/&曲線來描述同樣的開關特性,相比之下dV/&曲線要更加精確一些。R_load表示這些數據是在什麼樣的負載狀況下得到的,如果使用的是標準的50 ohm負載,那麼這一項是可選擇的。

[Ramp]

| variable typ min max

dV/dt_r 2.20/1.06n 1.92/1.28n 2.49/650p

dV/dt_f 2.46/1.21n 2.21/1.54n 2.70/770p

R_load=300ohms

上面所提到的這些數據都有三個值可供選擇:典型值、最小值和最大值.這些是由工作環境的溫度、電源電壓以及工藝製程的變化來決定的。使用各種數據的最小值和最大值,就可以表現出模型的最差和最好情況。例如,要得到一個快速的模型,可以使用最高值的電流、最快的ramp數據以及最小的封裝寄生參數:而要得到慢速的模型則正好相反。在有的模型中,並不提供最小值和最大值,只是用N/A來表示,如上面舉的Power Clamp的例子。而典型值在模型中是必須要提供的。

封裝寄生參數在IBIS模型文件中用R_pkg、L_pkg和C_pkg來表示,如果在文件中對管腳的說明部分對每個管腳又賦予了具體的封裝參數值,那麼全局定義的封裝參數就不起作用。

在前面給出的IBIS文件的例子中可以看到,每一部分的開頭都由方括弧開始,在方括弧中的是定義語句的關鍵字,它對跟在後面的數據作出了說明,這樣模擬器就可以使用這些數據。在一個IBIS文件中,有的關鍵字是必須的,而有的則是可選擇的。一個有效的IBIS文件必須包括以下三部分的數據和關鍵字:

4、建立IBIS模型

IBIS模型可以通過模擬器件的SPICE模型來獲得,也可以用直接測量的方法來獲得。作為最終用戶,最常見的方法是到半導體製造廠商的網站上去下載各種器件的IBIS模型,在使用前要對得到的IBIS模型進行語法檢查。

建立一個器件的IBIS模型需要以下幾個步驟:

5、使用IBIS模型

IBIS模型可以通過模擬器件的SPICE模型來獲得,也可以用直接測量的方法來獲得。最為最終用戶,最常見的方法是到半導體製造廠商的網站上去下載各種器件的IBIS模型,在使用前要對得到的IBIS模型進行語法檢查。

IBIS模型主要用於板級系統或多板信號的信號完整性分析。可以用IBIS模型分析的信號完整性問題包括:串擾、反射、振鈴、上沖、下沖、不匹配阻抗、傳輸線分析、拓撲結構分析等等。IBIS模型尤其能夠對高速信號的振鈴和串擾進行準確精細的模擬,它可用於檢測最壞情況的上升時間條件下的信號行為,以及一些用物理測試無法解決的問題。在使用時,用戶用PCB的資料庫來生成電路板上的連線的傳輸線模型,然後將IBIS模型賦給電路板上相應的驅動端或接收端,就可以進行模擬了。

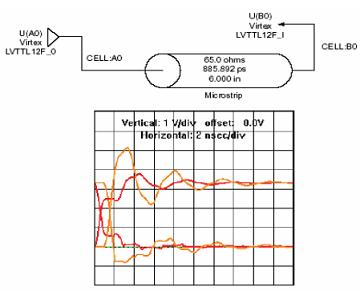

圖2和圖3給出了一個用IBIS模型進行信號完整性分析的例子。可以看到,在使用IBIS模型進行模擬后,發現信號質量不佳,於是採取了添加終端匹配的方法,使信號質量有了較大的改善。

圖2 未添加終端匹配的例子

圖3 添加了串聯匹配的例子

為了滿足多板信號模擬的要求,IBIS最新的版本Version3.2中添加了EBD(ElectricalBoard Description)的新特點。EBD模型的基本語法與IBIS模型相同,它是將整塊電路板做為一個器件來對待,這樣,在多板模擬時就可以直接調用EBD模型,而不用關心EBD模型所描述的電路板內部的具體情況。使用一些電路板模擬軟體可以自動生成EBD模型,例如HyperLynx6.1就有這一功能。

雖然IBIS模型有很多的優點,但是也存在一些不足。目前,仍有許多廠商缺乏對IBIS模型的支持。而缺乏IBIS模型,IBIS模擬工具就無法工作。雖然IBIS文件可以手動創建或通過Spice模型來轉換,但是如果無法從廠家得到最小上升時間參數,任何轉換工具都無能為力。另外,IBIS還缺乏對地彈雜訊的建模能力。

6、IBIS相關工具及鏈接

IBIS問世以來,出現了很多相關的工具,下面介紹幾種常用的免費工具 :

如果需要到網上查找一些IBIS的相關內容,下面的幾個鏈接可能會提供一些幫助:

http://www.eigroup.org/ibis/ibis.htm

http://www.innoveda.com/products/datasheets_HTML/ibis.asp

http://www2.ncsu.edu/eos/project/erl_htm

[admin via 研發互助社區 ] IBIS模型介紹已經有23665次圍觀

http://cocdig.com/docs/show-post-44304.html