--謹以此文獻給初學SI 的艱苦歲月

IBIS 模型在做類似板級SI 模擬得到廣泛應用。在做模擬的初級階段,經常對於ibis 模型的描述有些疑問,只知道把模型拿來轉換為軟體所支持的格式或者直接使用,而對於IBIS 模型裡面的數據描述什麼都不算很明白,因此下面的一些描述是整理出來的一點對於ibis 的基本理解。在此引用很多presention來描述ibis 內容(有的照抄過來,阿彌陀佛,不要說抄襲,只不過習慣信手拈來說明一些問題),僅此向如muranyi 等ibis 先驅者致敬。本文難免有些錯誤或者考慮不周,隨時歡迎進行討論並對其進行修改!

IBIS 模型的一些基本概念

IBIS 這個詞是Input/Output buffer information specification 的縮寫。本文是基於IBIS ver3.2 所撰寫出來(www.eigroup.org/IBIS/可下載到各種版本spec),ver4.2增加很多新特性,由於在目前設計中沒用到不予以討論。。。

在業界經常會把spice 模型描述為transistor model 是因為它描述很多電路細節問題。而把ibis 模型描述為behavioral model 是因為它並不象spice 模型那樣描述電路的構成,IBIS 模型描述的只不過是電路的一種外在表現,象個黑匣子一樣,輸入什麼然後就得到輸出結果,而不需要了解裡面驅動或者接收的電路構成。因此有所謂的garbage in, garbage out,ibis 模型的模擬精度依賴於模型的準確度以及考慮的worse case,因此無論你的模型如何精確而考慮的worse case 不周全或者你考慮的worse case 如何周全而模型不精確,都是得不到較好的模擬精度。

IBIS 模型的構成

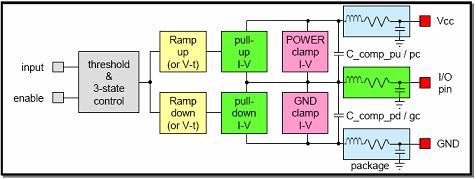

經典示意圖如下:

從上圖可以看出,基本的IBIS模型包括如下的一些信息(對於不同類型的model有一些信息會省略掉)

VI 曲線: Pullup & Pulldown &POWER clamp& GND clamp

VT曲線: Rise waveform, Fall waveform

還有一些其它比較重要的信息比如Die capacitance: C_comp(最近好像那個muranyi對這個很感興趣,一直發布presentation討論怎麼把這個做的更精確)以及RLC package parameter。至於一些基本的輸入以及使能信息會在軟體設置自動生成,不需要我們多關注。對於於ibis模型長什麼樣子,大家去micron主頁ddr2 sdram模塊下載幾個io buffer看看是什麼樣。希望你先看看長啥樣再看下面的一些說明。

IBIS 的應用場合

任何電路都可以用下面的模型(好像是Shannon 模型我不知道。。。)來描述

Driver -------------interconnect------------------Receiver

注意IBIS 模型描述的是Driver/Receiver 的行為特性而並不是它們的電路特性,因而內部的一些邏輯延時是沒有考慮的(在此你就該好好明白為啥要區分Tco的概念),通過使用IBIS 模型,從而得出interconnect 對於電路的影響。在目前一些使用ibis model 模擬的軟體中,在Cadence 裡面,ibis 模型是轉換為dml 格式,在Hyperlynx 裡面直接調用ibis 模型。由於ibis 支持的buffer type 很多,每個類型都會有對應的格式以及需要包含的信息,常用有output, input 以及IO 模型,至於其他的模型,大家可以參照ibis 說明,有些些微的差異。

IBIS 模型中vi/vt 曲線的由來

有大牛的示意圖形,不多說

Pull down 曲線由來(此曲線需要考慮與clamp 曲線重複的部分)

Ground clamp 曲線由來

Pull up 曲線由來(此曲線需要考慮與clamp 曲線重複的部分)

Power clamp 曲線由來

注意:ibis 裡面定義電流流入方向為正;在此圖中pull up 以及power clamp 曲線都沒經過轉化(傳說的vcc relative 沒出現,^_^,使用Vcc relative 從目前得到的解釋是模型可以應用在兼容電壓模式,舉個例子2.5v 兼容3.3V 的器件,2.5v 和3.3v 工作狀態下可以使用相同的模型而不用建立兩模型描述單個器件)

IBIS 模型在軟體中的應用

目前高速信號軟體大部分都是spice-compatible 軟體,而且很多都內嵌field solver分析傳輸線,因而在模擬中勢必會把ibis 模型的信息轉換成spice 信息來使用,來看看ibis 模型是如何轉換成spice 信息使用的。看下如下的示意圖,

但是VI 曲線僅僅描述的是DC 狀態,那麼在ibis 模型中描述瞬態的vt 曲線如何

轉換值得商討,看以下的等效圖

可以得出等式:-Iout=Ku*Ipu+Kd*Ipd+Ipc+Igc

如果rising/falling waveform 只有一條曲線,比如VCC+Rfixture,可假設

得方程

如果有兩條曲線,比如VCC/GND+Rfixture,Ku 與Kd 獨立解出,從而可以得出模擬的瞬態曲線

比較有趣的問題

Vi/Vt 曲線的匹配(參考hyperlynx 的幫助)

對於falling waveform R_fixture=50 Ohms and V_fixture=3.3V負載線與pull up 曲線交界為falling waveform 起始點,與pull down 曲線交界為falling waveform 終點(始終記住pull up 是Vcc relative 需要轉換)

對於Rising waveform R_fixture=50 Ohms and V_fixture=3.3V

負載線與pull down 曲線交界為rising waveform 起始點,與pull up 曲線交界為rising waveform 終點

Package model 的應用

在ibis 裡面有三個地方可以使用package model

A, [Pin] 語句裡面,描述的是local package 參數,只有typ 值

B, [Package]語句裡面,描述的是global package 參數,有slow/typ/fast 取值

C, [Define Package Model]裡面,描述的是local package 參數,能帶傳輸線,只有typ 值

Ramp 數值由來

測量vt 曲線

dv=(80%-20%)*(Vmaximum-Vminimum)

dt= t [80%*(Vmaximum-Vminimum)]- t [20%*(Vmaximum-Vminimum)]

總結

1,很多人告訴我說想驗證ibis 模型,比較好玩,實際上你用軟體檢查后你會發現很少有其它事情我們可以做的。。。畢竟,你不是做晶元的,不要扁我!對於有問題的ibis 模型,我們有辦法做什麼事情么?沒有,但你一定要知道問題在那兒,滅那些晶元的而不用被他們嘲笑,哈哈。

2,關於ibis 的發展前途,從目前發展趨勢,它的歸宿只有兩個:

a 由於自動化的需要,遲早要成為一個編程語言,哈哈,又多一個求生的飯碗,大家快去學。。。

b 不要高興太早,它有可能語法太龐大複雜最終被其它取代。。。

參考文獻

1.Hyperlynx 幫助

2.The Development of Analog SPICE Behavioral Model Based on IBIS Model

3.Introduction to IBIS models and IBIS model making

[admin via 研發互助社區 ] IBIS 理解說明已經有12648次圍觀

http://cocdig.com/docs/show-post-44277.html