1.引言

隨著電子產品功能的日益複雜和性能的提高,印刷電路板的密度和其相關器件的頻率都不斷攀升,保持並提高系統的速度與性能成為設計者面前的一個重要課題。信號頻率變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串擾在高速PCB設計中的影響顯著增加。串擾問題是客觀存在,但超過一定的界限可能引起電路的誤觸發,導致系統無法正常工作。設計者必須了解串擾產生的機理,並且在設計中應用恰當的方法,使串擾產生的負面影響最小化。

2.高頻數字信號串擾的產生及變化趨勢

串擾是指當信號在傳輸線上傳播時,相鄰信號之間由於電磁場的相互耦合而產生的不期望的雜訊電壓信號,即能量由一條線耦合到另一條線上。

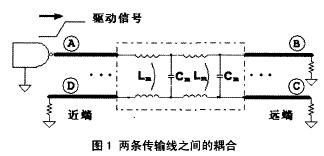

如圖1所示,為便於分析,我們依照離散式等效模型來描述兩個相鄰傳輸線的串擾模型,傳輸線AB和CD的特性阻抗為Z0,且終端匹配電阻R=Z0。如果位於A點的驅動源為干擾源,則A—B間的線網稱為干擾源網路(Aggressor line),C—D之間的線網被稱為被干擾網路(Victim line),被干擾網路靠近干擾源網路的驅動端的串擾稱為近端串擾(也稱後向串擾),而靠近干擾源網路接收端方向的串擾稱為遠端串擾(也稱前向串擾)。串擾主要源自兩相鄰導體之間所形成的互感Lm和互容Cm。

2.1感性耦合

在圖1中,先只考慮互感Lm引起的感性耦合。線路A到B上傳輸的信號的磁場在線路C到D上感應出電壓,磁耦合的作用類似一個變壓器,由於這是個分散式的傳輸線,所以互感也變成一連串的變壓器分佈在兩個相鄰的并行傳輸線上。當一個電壓階躍信號從A移動到B,每個分佈在干擾線上的變壓器會依序感應一個干擾尖脈衝出現在被干擾網路上。互感在被干擾網路上疊加的這個電壓雜訊,其大小跟干擾網路上驅動電流的變化成正比。由互感產生的雜訊計算公式為

值得注意的是,耦合變壓器每一段的互感耦合的極性是不同的,這些感應到被干擾網路的干擾能量依序前向和後向,但極性相反,沿著傳輸線CD分別往C和D點行進。

如圖2所示,往C方向的前向干擾能量,是和入射電壓及每個互感分量Lm成正比,因為所有前向干擾能量幾乎同時抵達C點,所以前向干擾能量與兩傳輸線的互感總量成正比,傳輸線平行的長度越長,所產生的互感總量就越大,前向干擾能量也隨即增加;然而往D點的後向干擾能量與往C點的前向干擾能量不同的是,雖然兩者耦合的總區域是一樣的,但每個互感變壓器所感應的干擾分量是依序到達D,後向干擾能量的有效時間長達2Tp(Tp為傳播延時),隨著線路平行長度的延長(即互感增加),後向串擾的幅度大小是不會變化的,而持續時間會增加。

2.2容性耦合

互容是產生串擾的另一個機制。互容Cm會對被干擾網路產生一個感應電流,該電流正比於干擾網路上電壓的變化速率,由互容Cm產生的雜訊計算公式為:

分散式耦合電容的耦合機制和分散式電感耦合相類似,區別在於耦合的極性。如圖3所示,互容耦合的前向和後向干擾能量的極性都是正的。

2.3互感和互容的合成效應

通常,容性串擾和感性串擾是同時發生的。由文獻[1],我們可以分別得到近端和遠端的總串擾的計算公式,它們是分別由容性耦合和感性耦合疊加而成的。

近端串擾總雜訊為:

遠端串擾總雜訊為:

其中,Z0,C,l,Cm,Lm,L,V0分別為傳輸線的特徵阻抗、單位長度電容、單位長度電感,兩傳輸線之間耦合電容、耦合電感,兩傳輸線平行長度和電壓峰值。

由以上兩式,我們可以看出遠端串擾總雜訊由於容性和感性耦合的極性關係而相互消減,即遠端串擾是可以消除的。在PCB布線中,帶狀線(Stripline)電路更能夠顯示感性和容性耦合之間很好的平衡,其前向耦合能量極小;而對於微帶線(Microstfip),與串擾相關的電場大部分穿過的是空氣,而不是其它的絕緣材料,因此容性串擾比感性串擾小,導致其前向耦合是一個小的負數。這也就是通常設計中,常忽略遠端串擾的干擾,而較著重於近端串擾改善的原因。

在實際設計中,PCB的有關參數(如厚度,介電常數等)以及線長、線寬、線距、傳輸線與地平面的位置和電流流向都會影響c、l、Cm、Lm、L、的大小,而信號頻率和器件的上升/下降時間決定了 。

在這裡我們不做這些參數對串擾影響的定量分析,有關這些參數的相互關係及對串擾影響的程度,詳見其它相關參考文獻。

2.4串擾的變化趨勢

互感與互容的大小影響著串擾的大小,從而等價地改變傳輸線特徵阻抗與傳播速度。同樣,傳輸線的幾何形狀在很大程度上影響著互感與互容的變化,因此傳輸線本身的特徵阻抗對這些參數也有影響。在同一介質中,相對低阻抗的傳輸線與參考平面(地平面)間的耦合更加強烈,相對地與鄰近傳輸線的耦合就會弱一些,因而低阻抗傳輸線對串擾引起的阻抗變化更小一些。

3 串擾導致的幾種影響

在高速、高密度PCB設計中一般提供一個完整的接地平面,從而使每條信號線基本上只和它最近的信號線相互影響,來自其它較遠信號線的交叉耦合是可以忽略的。儘管如此,在模擬系統中,大功率信號穿過低電平輸入信號或當信號電壓較高的元件(如TTL)與信號電壓較低的元件(如ECL)接近時,都需要非常高的抗串擾能力。在PCB設計中,如果不正確處理,串擾對高速PCB的信號完整性主要有以下兩種典型的影響。

3.1串擾引起的誤觸發

信號串擾是高速設計所面臨的信號完整性問題中一個重要內容,由串擾引起的數字電路功能錯誤是最常見的一種。

圖4是一種典型的由串擾脈衝引起的相鄰網路錯誤邏輯的傳輸。干擾源網路上傳輸的信號通過耦合電容,在被干擾網路和接收端引起一個雜訊脈衝,結果導致一個不希望的脈衝發送到接受端。如果這個脈衝強度超過了接收端的觸發值,就會產生無法控制的觸發脈衝,引起下一級網路的邏輯功能混亂。

3.2串擾引起的時序延時

在數字設計中,時序問題是一個重要考慮的問題。圖5顯示了由串擾雜訊引起的時序問題。圖下半部分是干擾源網路產生的兩種雜訊脈衝(Helpful圖5串擾雜訊導致的延時glitch和Unhelpful glitch),當雜訊脈衝(helpful glitch)疊加到被干擾網路,就引起被干擾網路信號傳輸延時減少;同樣,當雜訊脈衝(Unhelpful glitch)疊加到被干擾網路時,就增加了被干擾網路正常傳輸信號的延時。儘管這種減少網路傳輸延時的串擾雜訊對改善PCB時序是有幫助的,但在實際PCB設計中,由於干擾源網路的不確定性,這種延時是無法控制的,因而對這種串擾引起的延時必須要加以抑制。

4.串擾最小化

串擾在高速高密度的PCB設計中普遍存在,串擾對系統的影響一般都是負面的。為減少串擾,最基本的就是讓干擾源網路與被干擾網路之間的耦合越小越好。在高密度複雜PCB設計中完全避免串擾是不可能的,但在系統設計中設計者應該在考慮不影響系統其它性能的情況下,選擇適當的方法來力求串擾的最小化。結合上面的分析,解決串擾問題主要從以下幾個方面考慮:

5.結束語

數字系統設計已經進入了一個新的階段。許多過去處於次要地位的高速設計問題,現在已經對於系統性能具有關鍵的影響。包括串擾在內的信號完整性問題帶來了設計觀念、設計流程及設計方法的變革。面對新的挑戰,對於串擾雜訊而言,最關鍵的就是找出那些對系統正常運行真正有影響的網路,而不是盲目的對所有網路進行串擾雜訊的抑制,這也是和有限的布線資源相矛盾的。本文所討論的串擾問題對於高速高密度電路設計中解決串擾問題具有十分重要的意義。

參考文獻

[1]Brain Yong,Digital Signal Integrity-Modeling and Simulafion with Interconnects and Package,Prentice

Hall PTR,2001

[2]Signal and Design Integrity,Cadence Design Systems Inc.2001

[3]謝金明 高速數字電路設計及雜訊控制技術 電子工業出版社2003.4

[admin via 研發互助社區 ] 高速PCB串擾分析及其最小化已經有4494次圍觀

http://cocdig.com/docs/show-post-44269.html