摘要:本文通過對源同步時序公式的推導,結合對SPECCTRAQuest時序模擬方法的分析,推導出了使用SPECCTRAQuest進行時序模擬時的計算公式,並對公式的使用進行了說明。

一、前言

通常我們在時序模擬中,首先通過時序計算公式得到數據信號與時鐘信號的理論關係,在cadence模擬中,我們也獲得了一系列的模擬結果,怎樣把模擬結果正確的運用到公式中,模擬結果的具體含義是什麼,是我們正確使用Cadence模擬工具的關鍵。下面對時序計算公式和模擬結果進行詳細分析。

二.時序關係的計算

電路設計中的時序計算,就是根據信號驅動器件的輸出信號與時鐘的關係(Tco——時鐘到數據輸出有效時間)和信號與時鐘在PCB上的傳輸時間(Tflytime)同時考慮信號驅動的負載效應、時鐘的抖動(Tiitter)、共同時鐘的相位偏移(Tskew)等,從而在接收端滿足接收器件的建立時間(Tsetup)和保持時間(Thold)要求。通過這些參數,我們可以推導出滿足建立時間和保持時間的計算公式。

時序電路根據時鐘的同步方式的不同,通常分為源同步時序電路(Source-synchronous timing)和共同時鐘同步電路(common-clock timing)。這兩者在時序分析方法上是類似的,下面以源同步電路來說明。

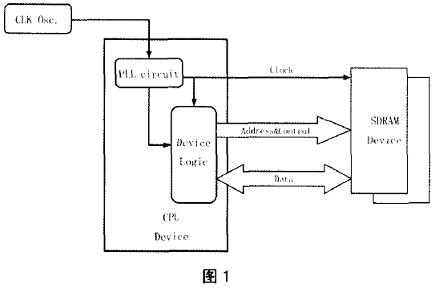

源同步時序電路也就是同步時鐘由發送數據或接收數據的晶元提供。圖1中,時鐘信號是由CPU驅動到SDRAM方向的單向時鐘,數據線Data是雙向的。

圖2是信號由CPU向SDRAM驅動時的時序圖,也就是數據與時鐘的傳輸方向相同時的情況。

圖中參數解釋如下:

由圖2的時序圖,我們可以推導出,為了滿足接收晶元的Tsetup和Thold時序要求,即Tsetup'>Tsetup和Thold'>Thold,所以Tft_clk和Tft_data應滿足如下等式:

Tft_data_min>Thold-Tco_min+Tft_clk (公式1)

Tft_data_max<Tcycle-Tsetup-Tco_max+Tft_clk (公式2)

當信號與時鐘傳輸方向相反時,也就是圖1中數據由SDRAM向CPU晶元驅動時,可以推導出類似的公式:

Tft_data_min>Thold-Tco_min-Tft_clk (公式3)

Tft_data_max<Tcycle-Tsetup-Tco_max-Tft_clk (公式4)

如果我們把時鐘的傳輸延時Tft_clk看成是一個帶符號的數,當時鐘的驅動方向與數據驅動方向相同時,定義Tft_clk為正數,當時鐘驅動方向與數據驅動方向相反時,定義Tft_clk為負數,則公式3和公式4可以統一到公式1和公式2中。

三.Cadence的時序模擬

在上面推導出了時序的計算公式,在公式中用到了器件手冊中的Tco參數,器件手冊中Tco參數的獲得,實際上是在某一種測試條件下的測量值,而在實際使用上,驅動器的實際負載並不是手冊上給出的負載條件,因此,我們有必要使用一種工具模擬在實際負載條件下的信號延時。Cadence提供了這種工具,它通過模擬提供了實際負載條件下和測試負載條件下的延時相對值。

我們先來回顧一下CADENCE的模擬報告形式。模擬報告中涉及到三個參數:FTSmode、SwitchDelay和SettleDelay。其中Cadence時序模擬的結果是通過SwitchDelay和SettleDelay兩個參數反映出來的。

在解釋FTSmode、SwitchDelay和SwitchDelay前先解釋一下BufferDelay曲線的含義。BufferDelay曲線是Cadence模擬器斷開實際負載,帶上驅動晶元器件手冊提供的測試負載條件下獲得的一條曲線。測試負載是在IBIS模擬模型庫中設置的。Cadence模擬報告中的延時測量是以BufferDelay為基準曲線,以V Measure為起始測量點獲得的相對延時值。

從SwitchDelay和SettleDelay的定義我們可以看出,SettleDelay是一個與輸入端的建立時間(Tsetup)有關的量,SwitchDelay是一個與輸入端保持時間有關的量(Thold)。

公式1和公式2中的Tft_data與Tft_clk在Cadenee模擬工具中是通過模擬獲得的數據,它與Cadence模擬中fast和slow狀態下的SwitchDelay與SettleDelay參數有關。

為了了解Cadence模擬中的SwitchDelay和SettleDelay與時序公式中參數的關係,我們重新分析一下包含有BufferDelay曲線的時序圖。

在圖4中,時鐘輸出和數據輸出使用的是BufferDelay曲線,此時Tco是時鐘BuferDelay曲線和數據BufferDelay曲線之間的延時關係,這種定義符合“手冊中的Tco是在特定負載下測得的”說法。

在圖4中,CPU CLK OUT(BuferDelay)和CPU Signals OUT(Buferdelay)是在測試負載條件下的信號輸出波形(對應於圖3中的BuferDelay曲線,而不是驅動端輸出曲線),SDRAM CLK IN和SDRAM Signals IN是在實際負載條件下輸入埠的模擬波形。

在器件手冊中給出時序關係時,對於時鐘信號,通常以某一測量電壓為時間測量點,如圖4中的Vmeas1和Vmeas2,對於驅動端測量電壓點為驅動器件手冊中定義的測量點,對於接收端測量電壓點為接收器件手冊中定義的測量點。在Cadence模擬時,對於接收端電壓測量點的設置,通常在接收器件模型中,把輸人高低門限電平定義成Vmeas2來實現。對於驅動端電壓測量點的設置,是在驅動器件模型參數中設置的。此時對於時鐘模擬的結果是,時鐘信號的SettleDelay和SwitchDelay值相等。

對於數據信號的測量點就稍微有點複雜了,這要根據手冊中Tco的測量方式來確定,有的器件手冊Tco是從時鐘的Vmeas到數據的Vmeas來測量的,有的手冊是從時鐘的Vmeas到數據的門限電平來測量的。如果採用從時鐘的Vmeas到數據的門限電平來測量的,則在Cadence模擬中,要對高低電平門限分別作為測量點模擬,然後取最惡劣的模擬結果。

對於公式中數據的延時Tft_data,從Cadence模擬中對SettleDelay和SwitchDelay的定義和圖4中的時序關係可以看出,Tft_data就是模擬結果中的SettleDelay和SwitchDelay參數,並且SettleDelay是與建立時間(Tsetup)有關,SwitchDelay是與保持時間(Thold)有關,因此公式中的Tft_data_min對應模擬結果中的SwitchDelay,Tft_data_max對應模擬結果中的SettleDelay,考慮到通常Slow狀態的延時比Fast狀態的延時要大,因此,公式中的Tft_data_min對應模擬結果中Fast狀態的SwitchDelay,Tft_data_max對應模擬結果中Slow狀態的SettleDelay。

對於公式中時鐘的延時,從測量方式中可以看出Tft_clk=SettleDelay=SwitchDelay,考慮到同一公式中模擬狀態的一致,因此,公式中與Thold有關的不等式中的Tfl_clk對應於Fast狀態的模擬值,與Tsetup有關的不等式中的Tft_clk對應Slow狀態的模擬值。寫成公式就是:

Tft_data_fast_switchdelay>Thold口Tco_min+Tft_clk_fast (公式5)

Tff_data_slow_settledelay<Tcycle-Tsetup 口Tco_max+Tft_clk_slow (公式6)

在實際模擬中,我們只要保證模擬結果滿足公式5和公式6的時鐘和數據關係,也就保證了單板工作時序的正確性。

四.總結

Cadence公司的Allegro SI和SigXplor設計工具為硬體開發工程師提供了一個功能強大的高速PCB模擬手段,通過模擬設計,可以設計出符合要求的信號時序和信號完整性,從而提高單板和系統的工作穩定性,降低開發風險和開發成本。

[admin via 研發互助社區 ] 時序計算和Cadence模擬結果的運用已經有2852次圍觀

http://cocdig.com/docs/show-post-44329.html