1 LVDS信號的工作原理和特點

對於高速電路,尤其是高速數據匯流排,常用的器件一般有:ECL、BTL、GTL和GTL+等。這些器件的工藝成熟,應用也較為廣泛,但都存在一個共同的缺點,即功耗大。

新興的CM0S工藝的低壓差分信號(Low Voltage Differential Signal,簡稱LVDS)器件給了我們另一種選擇。LVDS低壓差分信號,最早由美國國家半導體公司(National Semiconductor)提出的一種高速串列信號傳輸電平,由於它傳輸速度快,功耗低,抗干擾能力強,傳輸距離遠,易於匹配等優點,迅速得到諸多晶元製造廠商和應用商的青睞,並通過TIA/EIA (Telecommunication Industry Association/Electronic Industries Association)的確認,成為該組織的標準(ANSI/TIA/EIA-644 standard)。LVDS信號被廣泛應用於計算機、通信以及消費電子領域,並被以PCI-Express為代表的第三代I/O標準中採用。

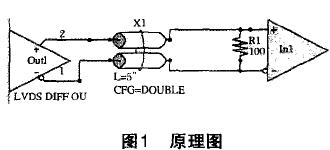

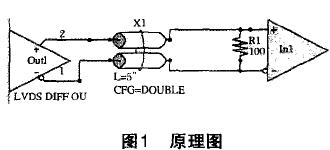

LVDS器件的工作原理如下:

如圖1所示,其中發送端是一個3.5mA的電流源,產生的3.5mA的電流通過差分線中的一路到接收端。由於接收端對於直流表現為高阻,電流通過接收端的100Ω的匹配電阻產生350mV的電壓,同時電流經過差分線的另一路流回發送端。當發送端進行狀態變化時,通過改變流經100Ω電阻的電流方向產生有效的'0'和'1' 態。

LVDS的特點是電流驅動模式,低電壓擺幅350mV可以提供更高的信號傳輸率,使用差分傳輸的方式,輸入信號只與2個信號的差值有關,可將共模干擾抑制掉,可以使信號的雜訊和EMI都減少。綜上所述,LVDS有以下主要特點:

- 低的輸出電壓擺幅(350mV);

- 差分特徵是磁干擾相互抵消,消除共模雜訊,減少EMI;

- 傳輸速度快,功耗低,抗干擾能力強,傳輸距離遠,易於匹配等優點。

2 LVDS信號在PCB上的設計

由LVDS信號的工作原理及特點可以看出:LVDS信號不僅是差分信號,而且還是高速數字信號;因此LVDS傳輸媒質不管使用的是PCB線對還是電纜,都必須採取措施防止信號在媒質終端發生反射,同時應減少電磁干擾以保證信號的完整性。只要我們在布線時考慮到以上這些要素,設計高速差分線路板並不很困難。下面將簡要介紹LVDS信號在PCB 上的設計要點:

- 布成多層板。

有LVDS信號的印製板一般都要布成多層板。由於LVDS信號屬於高速信號,與其相鄰的層應為地層,對LVDS信號進行屏蔽防止干擾。另外密度不是很大的板子,在物理空間條件允許的情況下,最好將LVDS信號與其它信號分別放在不同的層。例如,對於四層板,通常可以按以下進行布層:LVDS信號層、地層、電源層、其它信號層。 - LVDS信號阻抗計算與控制。

LVDS信號的電壓擺幅只有350 mV,適於電流驅動的差分信號方式工作。為了確保信號在傳輸線當中傳播時不受反射信號的影響,LVDS信號要求傳輸線阻抗受控,通常差分阻抗為(100±10)Ω。阻抗控制的好壞直接影響信號完整性及延遲。如何對其進行阻抗控制呢?

① 確定走線模式、參數及阻抗計算。LVDS分外層微帶線差分模式和內層帶狀線差分模式兩種,分別如圖2、圖3所示。通過合理設置參數,阻抗可利用相關阻抗計算軟體(如POLAR-SI6000、CADENCE的ALLEGRO)計算也可利用阻抗計算公式計算。圖2、圖3為POLAR-SI6000阻抗計算軟體計算阻抗值。

阻抗計算公式計算阻抗。以上微帶線和帶狀線種方式阻抗計算公式分別為:

(i)微帶線(microstrip)

Z={87/[sqrt(εr+1.41)]}ln[5.98H/(0.8W+T)]

其中,W為線寬,T為走線的銅皮厚度,H為走到參考平面的距離,εr是PCB板材質的介電常數(dielectric Constant)。此公式必須在0.1<(W/H)<2.0及1<(εr)<15的情況才能應用。

(ii)帶狀線(stripline)

Z=[60/sqrt(εr)]ln{4H/[0.67π(T+0.8W)]}

其中,H為兩參考平面的距離,並且走線位於參考平面的中間。此公式適應於雙線,線間距與抗成正比,必須在W/H<0.35及T/H<0.25的情況才應用。

由上面兩公式可以看出,雖然其計算公式各不同,但阻抗值均與絕緣層厚度成正比,與介電常數、線的厚度及寬度成反比。

② 走平行等距線(如圖4)。確定走線線寬及間距,在走線時要嚴格按照計算出的線寬和間距,兩線間距要一直保持不變,也就是要保持平行(如圖4示)。平行的方式有兩種: 一種為兩條線走在同一線層(side-by-side),另一種為兩條線走在上下相兩層(over-under)。一般盡量避免使用後者即層間差分信號,因為在PCB板的實際加工過程中,由於層疊之間的層壓對準精度大大低於同層蝕刻精度,以及層壓過程中的介質流失,不能保證差分線的間距等於層間介質厚度,會造成層間差分對的差分阻抗變化。困此建議盡量使用同層內的差分。

- 緊耦合原則。

在計算線寬和間距時最好遵守緊耦合的原則,也就是差分對線間距小於或等於線寬。當兩條差分信號線距離很近時,電流傳輸方向相反,其磁場相互抵消,電場相互耦合,電磁輻射也要小得多。 - 走短線、直線。

為確保信號的質量,LVDS差分對走線應該儘可能地短而直,減少布線中的過孔數,避免差分對布線太長,出現太多的拐彎,拐彎處盡量用45°或弧線,避免90°拐彎。 - 不同差分線對間處理。

LVDS對走線方式的選擇沒有限制,微帶線和帶狀線均可,但是必須注意要有良好的參考平面。對不同差分線之間的間距要求間隔不能太小,至少應大於3~5倍差分線間距。必要時在不同差分線對之間加地孔隔離以防止相互問的串擾。 - LVDS信號遠離其它信號。

對LVDS信號和其它信號比如TTL信號,最好使用不同的走線層,如果因為設計限制必須使用同一層走線,LVDS和TTL的距離應該足夠遠,至少應大於3~5倍差分線間距。 - LVDS差分信號不可以跨平面分割。

儘管兩根差分信號互為迴流路徑,跨分割不會割斷信號的迴流,但是跨分割部分的傳輸線會因為缺少參考平面而導致阻抗的不連續(如圖5箭頭處所示,其中GND1、GND2為LVDS相鄰的地平面)。 - 接收端的匹配電阻的布局。

對接收端的匹配電阻到接收管腳的距離要盡量靠近。如圖5的矩形處為接收端的匹配電阻。 - 匹配電阻的精度要求。

對於點到點的拓撲,走線的阻抗通常控制在100Ω,但匹配電阻可以根據實際的情況進行調整。電阻的精度最好是1%~2%。因為根據經驗,10%的阻抗不匹配就會產生5%的反射。

3、LVDS信號PCB設計實例

根據以上處理原則,簡單介紹一塊LVDS信號PCB設計實例,此板為16層多層印製板,疊層與板材(FR-4板材)關係如圖6。

LVDS信號分別走在L1和L16層,L1的屏蔽層為G2,L16屏蔽層為G15(其中G2、G15是一完整的地平面),這樣不但可以減少過孔數、線短,而且每個LVDS信號層都有完整的參考地平面相鄰。

利用POLAR-SI6000計算表面微帶差分走線:線寬6mils,線間距為6mils,阻抗理論計算值為99.1Ω。在生產過程中通過嚴格控制各種參數,利用CITS500S阻抗測試儀測試附連板的阻抗值範圍為(95.6~106.8)Ω,完全符合阻抗控制要求。

4、結束語

在LVDS信號PCB設計上,我們要考慮的因素很多,不僅要考慮與其他信號相互間的影響,更關心是其自身阻抗的控制和線長控制等。