隨著行動電話、WLAN(Wireless Local Area Network)、藍牙(Bluetooth)的普及化,高頻電子設備已經成為生活中的必需品,而電子設備使用的頻率也從過去的1GHz逐漸朝5GHz甚至更高頻方向發展。由於FET等主動電子組件與電容、電感等被動電子組件性能的提升,使得高頻電路的特性獲得大幅的改善。以往GHz的電路大多是由micro strip line等分佈定數電路所構成,最近因為電子組件晶元化,因此高頻電路以集中定數電路居多,不過即使高頻電路已經進入集中定數電路時代,然而設計者卻還未意識到配線長度、組件形狀等分佈定數性對高頻電路的影響。此外電子組件晶元化之後若單靠是集中定數設計電路,勢必會遭遇到設計上的極限,因此必需藉助計算機模擬技術,針對pattern與組件的形狀、配置(layout)等物理性尺寸進行精密的分析、設計,有鑒於此本文將深入探討有關5GHz高頻電路設計要領。

頻率與信號位相

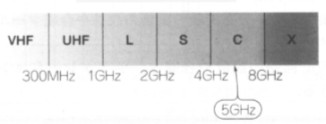

如圖1所示5GHz剛好介於C band的中央部位,5GHz的信號在自由空間的波長為60nm,相較之下厚度1.0mm的FR-4玻璃環氧基板上的50Ω micro strip line的波長?有32 nm,在該line如果組件位置偏差8mm,信號位相會產生900的相違,進而直接、間接造成電路結構、設計以及功能上的差異。此外電子組件晶元化並不代表可以完全取消matching調整等外置組件,換言之設計5GHz等級的高頻電路,仍應該以被動電子組件的特性為主要考慮。尤其是使用chip inductor時必需詳讀該組件的規格表(spec sheet)。表1是太陽誘電公司高頻積層chip inductor HK1608系列的型錄摘要,值得注意的是表中列示的「自我共振頻率」,由於該組件會引發自我共振,所以chip inductor的等價電路會成為電感(inductor)與電容(condenser)的等價電路,當頻率低於自我共振頻率時,會出現誘導性形成電感(inductor)功能,如果頻率高於自我共振頻率時就會出現容量性。

圖1 頻率分佈chart

| 型號 | 電感值(nH) | 最小Q | 最小Q的測試頻率 (MHz) | Q的代表值 | 自我共振頻率(MHz) | 直流阻抗(Ω) | ||||||

| 測試頻率(MHz) | ||||||||||||

| 100 | 300 | 500 | 800 | 1000 | min. | typ. | max. | typ. | ||||

| HK1608 1NOS | 1.0±0.3 | 8 | 100 | 14 | 30 | 40 | 70 | 90 | 10000 | >13000 | 0.05 | 0.015 |

| HK1608 1N2S | 1.0±0.3 | 8 | 100 | 14 | 30 | 40 | 70 | 90 | 10000 | >13000 | 0.05 | 0.015 |

| | | | | | | | ||||||

| HK1608 5N6 | 1.0±0.3 | 10 | 100 | 14 | 25 | 33 | 42 | 46 | 4000 | 5800 | 0.18 | 0.09 |

| HK1608 6N8 | 1.0±0.3 | 10 | 100 | 14 | 25 | 33 | 43 | 47 | 4000 | 5600 | 0.22 | 0.11 |

| HK1608 8N2 | 1.0±0.3 | 10 | 100 | 14 | 26 | 34 | 44 | 48 | 3500 | 5200 | 0.24 | 0.13 |

| | | | | | | | ||||||

| HK1608R15 | 1.0±0.3 | 8 | 50 | 13 | 19 | 16 | -- | -- | 500 | 800 | 1.2 | 0.73 |

| HK1608R18 | 1.0±0.3 | 8 | 50 | 13 | 18 | 12 | -- | -- | 400 | 700 | 1.3 | 0.85 |

| HK1608R22 | 1.0±0.3 | 8 | 50 | 12 | 16 | -- | -- | -- | 400 | 600 | 1.5 | 0.95 |

圖8是50Ω插入並聯(series)與分路(shunt)時的模擬(simulation)電路;

圖8 電容串聯與分路的模擬電路

圖9與圖10分別是並聯(series)與分路(shunt)時的通過特性圖。為了簡化比較因此用?有電感值(inductance)成份的特性方式表示,也就是說測試結果並無無寄生容量的特性。由圖10的測試結果可知50Ω插入分路(shunt)時,會以共振頻率為中心出現極大差異,相較之下50Ω插入並聯(series)時,若與?有電容(capacitor)成份比較,雖然並未出現很大差異,不過在共振頻率附近的損失卻明顯減少。由此可知若將電容單純當作藕合電容(coup ling condenser)使用時,電感成份的影響會比較少,相較之下或若將電容當作matching特性調整使用時,電感成份的影響則明顯增加。

圖9 電容串列電路的通過特性

圖10 電容並聯電路的通過特性

此外GND(Ground)的設計對高頻電路具有關鍵性的影響,如果未正確設計GND,其結果不單是增幅器等主動電路受到影響,經常連filter等被動電路也無法獲得預期的性能。以如圖11所示的micro strip電路為例,通常多層電路板內側表層會成為基準的接地層(Ground layer),封裝於電路板表層的組件接地,則是利用小直徑via hole與內層連接。為了確認與內側表層連接的表層patter是否屬於GND,因此不斷變更厚0.8的FR4玻璃環氧基板上的via hole直徑,並利用模擬分析探討via hole的阻抗(impedance)特性,亦即所謂電抗(reactance)特性。

圖11 連接表、裡層GND的via hole

圖12是模擬電路,圖13是模擬分析后的阻抗特性。

圖12 via hole的simulation電路

圖13 via hole的頻率阻抗特性

由分析結果可知via hole具有微量的電抗成份,因此多層電路板表面的GND會比照微量的電抗成份,從內側基準的接地層浮現,如圖13所示via hole的直徑越大,電抗成份相對的越小。此外頻率越高電抗也越大,如果將via hole視為inductor,並計算等價性電感值其結果為:

根據實驗結果顯示基板厚度越薄,via hole直徑越大且複數設置時,基本上可以有效減緩電抗。

[admin via 研發互助社區 ] 5GHz的高頻電路設計技巧已經有3877次圍觀

http://cocdig.com/docs/show-post-44272.html