翻譯:Michael Qiao

當你認為你已經掌握了PCB 走線的特徵阻抗Z0,緊接著一份數據手冊告訴你去設計一個特定的差分阻抗。令事情變得更困難的是,它說:“……因為兩根走線之間的耦合可以降低有效阻抗,使用50Ω的設計規則來得到一個大約80Ω的差分阻抗!”這的確讓人感到困惑!

這篇文章向你展示什麼是差分阻抗。除此之外,還討論了為什麼是這樣,並且向你展示如何正確地計算它。

單線:

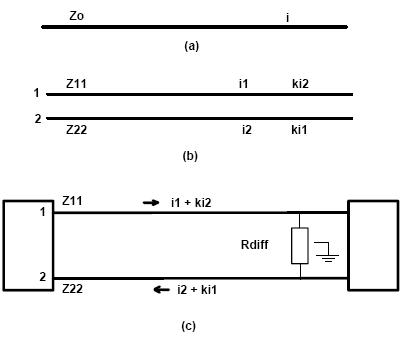

圖1(a)演示了一個典型的單根走線。其特徵阻抗是Z0,其上流經的電流為i。沿線任意一點的電壓為V=Z0*i( 根據歐姆定律)。

一般情況,線對:

圖1(b)演示了一對走線。線1 具有特徵阻抗Z11,與上文中Z0 一致,電流i1。線2具有類似的定義。當我們將線2 向線1 靠近時,線2 上的電流開始以比例常數k 耦合到線1 上。類似地,線1 的電流i1 開始以同樣的比例常數耦合到線2 上。每根走線上任意一點的電壓,還是根據歐姆定律,為:

V1 = Z11*i1 + Z11*k*i2 (1)

V2 = Z22*i2 + Z22*k*i1

現在我們定義Z12 = k*Z11 以及Z21 =k*Z22。這樣,式(1)就可以寫成:

V1 = Z11*i1 + Z12*i2 (2)

V2 = Z21*i1 + Z22*i2

這是一對熟悉的聯立方程組,我們可以經常在教科書中看到。這個方程組可以一般化到任意數量的走線,並且可以用你們中大部分人都熟悉的矩陣形式來表示。

圖1 各種走線的結構

特殊情況,差分對:

圖1(c)演示了一對差分走線。重寫式1:

V1 = Z11*i1 + Z11*k*i2 (1)

V2 = Z22*i2 + Z21*k*i1

現在注意在仔細設計並且是對稱的情況下,

Z11 = Z22 = Z0,且

i2 = -i1

這將導致(經過一些變換):

V1 = Z0*i1*(1-k) (3)

V2 = -Z0*i1*(1-k)

注意V1 = -V2,當然,這是我們已經知道的,因為這是一個差分對。

有效(差模)阻抗:

電壓V1 以地為參考。線1 的有效阻抗(單獨來看,在差分對中叫做“差模”阻抗,通常叫做“單線”阻抗)為電壓除以電流,或:

Zodd = V1/i1 = Z0*(1-k)

由上可知,因Z0 = Z11 且k = Z12/Z11,

上式可寫成:

Zodd = Z11 - Z12

這也是一個在許多教科書中都可以看到的公式。

為了防止反射,正確的端接方法是用一個值為Zodd 的電阻。類似地,線2 的差模阻抗與此相同(在對稱差分對的特定情形下)。

差分阻抗:

假定在某一瞬間我們將兩根走線用電阻端接到地。因為i1 = -i2,所以根本沒有電流流經地。也就是說,沒有真正的理由把電阻接地。事實上,有人認為,為了將差分信號和地雜訊隔離,一定不能將它們連接到地。因此通常的連接形式如圖1(c)中所示,用單個電阻連接線1 與線2。電阻的值是線1和線2 差模阻抗的和,或:

Zdiff = 2*Z0*(1-k) 或

2*(Z11 - Z12)

這就是為什麼你經常看到實際上一個差分對具有大約80Ω的差分阻抗,而每個單線阻抗是50Ω。

計算:

知道Zdiff 是2*(Z11-Z12)不是很有用,因為Z12 的值並不直觀。但是,當我們看到Z12與耦合係數k 有關,事情就變得清晰了。事實上,耦合係數與我在Brookspeak 中關於串擾的專欄I中談到的耦合係數是相同的。國家半導體發布的計算Zdiff 的公式II已經被廣泛接受:

Zdiff = 2*Z0(1-.48*e-.96*S/H) 微帶線

Zdiff = 2*Z0(1-.347*e-2.9*S/H) 帶狀線

其中的術語在圖2 中定義。Z0 為其傳統定義III。

圖2 查分阻抗計算中的術語定義

共模阻抗:

為了討論完整起見,共模阻抗與上面略有不同。第一個差別是i1 = i2(沒有負號),這樣式3 就變成:

V1 = Z0*i1*(1+k) (4)

V2 = Z0*i1*(1+k)

並且正如所期望的,V1 = V2。因此單線阻抗是Z0*(1+k)。在共模情況下,兩根線的端接電阻均接地,所以流經地的電流為i1+i2 且這兩個電阻對器件表現為並聯。也就是說,共模阻抗是這些電阻的並聯組合,或:

Zcommon = (1/2)*Z0*(1+k),或

Zcommon = (1/2)*(Z11 + Z12)

注意,這裡差分對的共模阻抗大約為差模阻抗的1/4。

I "Crosstalk, Part 2: How Loud Is It?" Brookspeak, December, 1997.

II 參考國家半導體"Introduction to LVDS"(第28-29 頁),可以從其官方網站上訪問:http://www.national.com/appinfo/lvds/。

III 參考"PCB Impedance Control, Formulas and Resources", March, 1998, 第12頁。公式為:

本文發表在Printed Circuit Design,一種Miller Freeman 的出版物,1998 年8 月. 1998 Miller Freeman, Inc. . 1998 UltraCAD Design Inc.

[admin via 研發互助社區 ] 差分阻抗-什麼是差分?已經有19773次圍觀

http://cocdig.com/docs/show-post-44267.html