前言

印刷電路板的pattern線路有很多必需是藉助thruogh hole完成線路路徑的布局,對低頻電路而言thruogh hole幾乎不會對該電路產生不良影響,不過高頻電路的阻抗(impedance)整合卻扮演關鍵性角色,換言之若將具有thruogh hole的線路當作一般傳輸線路處理,就會面臨許多超乎預期的困擾,主要原因是在傳輸線路上如果設有thruogh hole,該部位就會產生非連續性點阻抗,而該點或多或少會形成反射波,最後造成電路誤動作,模擬電路的精度發生誤差等嚴重後果。

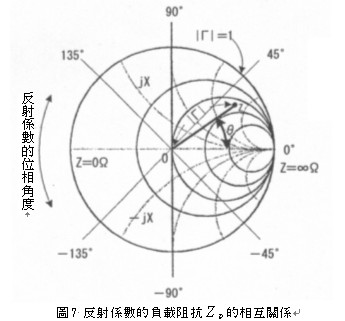

該反射波的反射程度是用反射係數表示,它是用復素數處理變成復素量。雖然電子電路經常使用復素數與admittance等計算方式,不過實際上復素數計算相當煩瑣,其中傳輸線路與高頻電路常用的復素數計算,如果改成史密斯特性圖表(Smith chart)方式,就可輕鬆獲得相同的計算結果。有鑒於此,本文將介紹史密斯特性圖表(Smith chart)使用上必需注意的事項。

反射係數

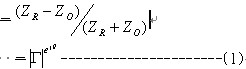

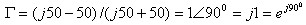

反射係數是表示整合狀態的尺度,反射係數是負載阻抗與傳輸線路特性阻抗Z0相異時,部份入射電力未被負載吸收,變成反射電力折返信號源時,入射電力與反射電力的比亦即反射係數可由下式求得:

Γ=反射波/入射

也就是說反射係數是具有大小與位相的量,它可由上式ZR 與 Z0 兩個阻抗關係求得,此外式(1)可轉換成下式:

【試算例1】

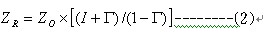

假設傳輸線路特性阻抗 Z0 為50Ω,負載阻抗分別是0Ω、50Ω、1kΩ、j50Ω時,反射係數Г=0.5ㄥ450,試算負載阻抗ZR 。

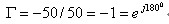

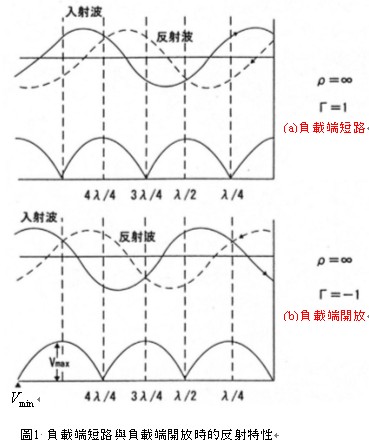

①ZR=0Ω 時(負載端短路)

這意味著振幅大小相等,位相 1800相異的反射波折返信號源,如圖1(b)所示。

②ZR=50Ω 時(整合)

Г=(50-50)/(50+50)=0

這表示成為整合狀態,未發生反射波。

③ZR=1000Ω 時(不整合)

Г=(1000-50)/(1000+50)=0.95

④ZR=∞Ω 時(負載端開放)

這表示振幅大小相等,位相相等的反射波折返信號源,如圖1(a)所示。

⑤ZR=j50Ω 時

⑥Г=0.5ㄥ450時

ZR=50x[(1+0.5ㄥ450)/(1-5ㄥ450)]

ZR=50x[(1+0.335+j.355)/(1-0.335-j0.355)]

=69.07+j65.12(Ω)

由試算例1可知從負載阻抗可求得反射係數的互動關係,反過來說也可由反射係數求得負載阻抗的互動關係,不過若改用史密斯圖表方式,就可直接從圖表中輕易獲得相果。

定常波比(VSWR)

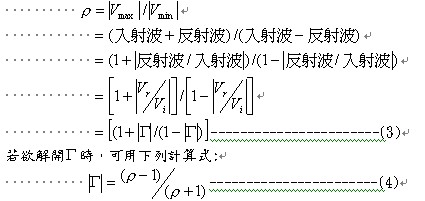

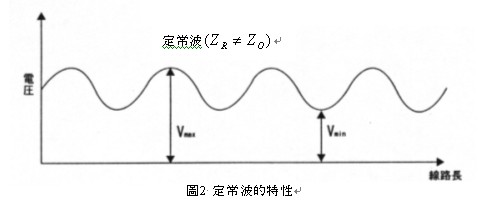

定常波比ρ與上述反射係數一樣,使用尺度表示整合狀態,定長波一旦產生反射波,就會在傳輸線路上與入射波合成,外觀上似乎在傳輸線路上變成停止狀態的波形,波的最大值與最小值的比稱讚定在波比ρ,亦即:

此處假設:

①整合(ZR=Z0) 時

則式(3)與(4)的反射係數Г=0,定常波比ρ=1 。

②不整合時

不整合時會產生反射波,如果出現如圖2所示定在波時,傳輸線路便具有頻率特性。如上所述在高頻電路阻抗整合具體重要意義,如果傳輸線路的特性阻抗Z0 與收信端(負載)的阻抗相同時,定常波就無法停滯,也就不會有信號傳輸問題產生,此時的線路可視為無損耗狀態,單位長度的特性阻抗

史密斯特性圖表(Smith chart)

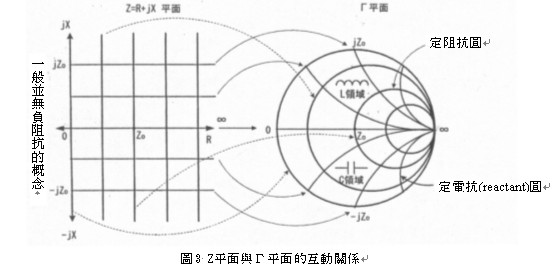

圖3是在直交坐標上將任意點的阻抗(復素數)轉換成反射係數 平面時,阻抗平面與反射係數平面 的互動關係。由於高頻電路的pattern線路必需考慮分佈定數迴路程傳輸線路,所以阻抗的整合也越來越重要。處理阻抗整合概念時,在史密斯特性圖表可將線路的特性阻抗 當作基準,同時還能將它視為正規化阻抗使用。

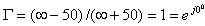

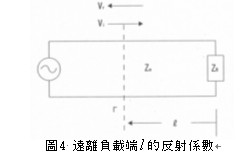

如圖4所示遠離負載端ZR 的反射係數 ,若以正規化阻抗z表示時,就可利用式(1)求得,亦即

Г=(ZRZ0-1)/(ZR/Z0+1)=(Z-1)/(Z+1)

如果用z表示則變成下式:

Z=(1+Г)/(1-Г)-------------------(5)

如上所述z與 是復素量,因此可轉換成下式:

Z=r+jx

Г=m+jn-------------------------(6)

z平面轉換成 平面的復素數時,可將各關係代入式(5)與(6)。

r+jx=(1+Г)/(1-Г)

=[1+(m+jn)]/[1+(m+jn)]

上式展開后將實數部與虛數部分開整理就變成圓的方程式,其結果如下:

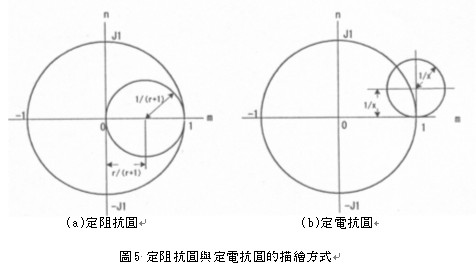

①定阻抗圓

正規化阻抗r為一定時,表示它是反射係數的圓,而圓的中心與半徑分別用下式求得:

圓的中心m=r/(r+1)

n=0

圓的半徑 1/(r+1)

例如整合時:

圓的中心 m=1/2

n=0

圓的半徑1/2

亦即通過半徑1(中心的正規化阻抗z=1+j0)時就會形成一個圓。為了獲得整合因此必需使r=1,依此前提便可利用組件L與C構成整合電路。

②定電抗(reactant)圓

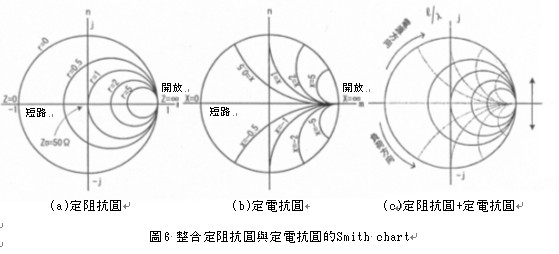

圖5是定阻抗圓與定電抗圓的描繪方式,圖6則是將定阻抗圓與定電抗圓描繪在同一平面的史密斯特性圖表(Smith chart)。

史密斯特性圖表的應用

使用史密斯特性圖表必需必需注意下列事項:

①史密斯特性圖表是在特性阻抗正規化前提下使用正規化阻抗。

②任意阻抗可用半徑為1的圓表示。

③特性阻抗正規化的正規化阻抗的z=1時(亦即與特性阻抗相呈整合狀),它的

位置相當於史密斯特性圖表平面的中心(z=1+jo)。

④由圖7可獲得負載阻抗ZR 與反射係數Г 的相互關係。

⑤電路組件直列連接時,阻抗平面與並連都可使用admittance。

[admin via 研發互助社區 ] 史密斯圖表的應用與阻抗整合已經有5127次圍觀

http://cocdig.com/docs/show-post-44244.html