a. OP增幅器構成的全波形整流電路patterning

圖1 的全波形整流電路,經常因正端(plus side)與負端(minus)gain的未整合,導致波形不均衡,所以決定gain值的電阻使用誤差為±1%的金屬皮膜電阻。本電路可以使IC1b作差動動作,因此能夠減緩高頻時波形不均衡現象。雖然OP 增幅器採用LF412,不過可以根據設計需求,改用與OP增幅器腳架相容的LM358

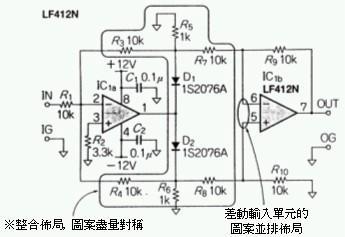

圖1 利用OP差動增幅器作全波整流的電路

IC1 的1、2 號腳架至5、6 號腳架路徑(route)是本電路基板主要設計重點,如圖2所示如果導線繞過IC的外側,路徑會變長所以採取IC下方布線設計,正、負電源的圖案導線寬度完全相同,信號則沿著箭頭方向流動,二極體(diode)等整流電路則整合在基板左側,電源導線加粗的同時接地採取full ground設計,如此一來雙面電路基板就可以滿足以上所有的要求。

圖2 利用OP差動增幅器作全波整流的電路基板圖案

b. 光學耦合器的基本周邊導線

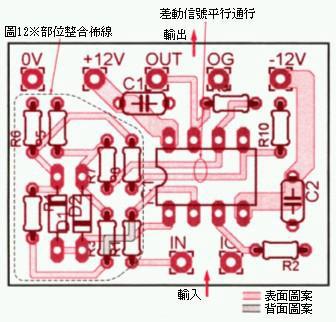

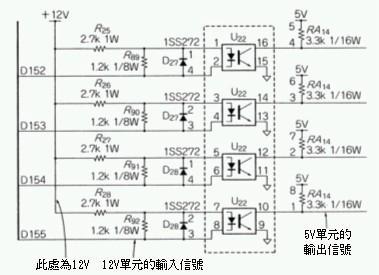

接著介紹封裝光學耦合器(photo coupler)的電路基板分離圖案設計技巧。光學耦合器主要功能是將board或是設備之間絕緣,主要原因是為了保障各組件保證的絕緣耐壓特性,因此電路基板出現所謂的分離圖案設計。圖3 的電路12V 的輸入單元與5V 的輸出單元就是採用分離圖案設計,它使用四個編號為的PS2801-4光學耦合器。

圖3 使用photo coupler 的電壓轉換電路

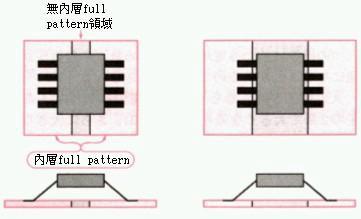

如圖4 所示為確保1次端(發光側)與2 次端(收光側)的沿面距離,所以設計上分成表層圖案與內層圖案,內層圖案若是full pattern時,與一般full pattern一樣需作除料設計。所謂沿面距離是線導體之間的指導,沿著絕緣物通行時最短距離而言,有關耐壓與沿面距離,UL、VDE 等各國的安全規範都有嚴謹的規定與說明。

(a)pattern的間隔過窄設計例 (b)pattern的間隔適當設計例

圖4 photo coupler 正下方的1 次端與2 次端圖案必需確實分離

I/O 點數很多而且使用複數個光學耦合器的場合,必需將散熱問題一併列入考慮。圖5 是根據以上需求,兼具散熱效果的pattern設計範例,由圖可知1 次端與2 次端的接地共通時,利用full pattern連接可以提高散熱效果;內層有接地時可以在full pattern設置數個via 與內層接地連接。如上所述根據1 次端與2 次端的電流值與散熱要求,最後才能決定電阻的定額與pattern 寬度

圖5 兼具散熱效果的pattern設計

c. 100V以上商用電源線的圖案

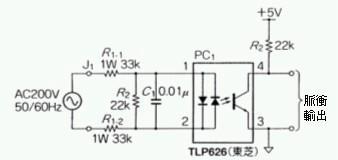

圖6 是已經絕緣可輸出脈衝的商用交流zero cross point電路。TLP626 LED 兩者未點燈時,光學耦合器的光學晶體管(photo transistor)成為OFF,輸出正極性的脈衝。

圖6 商用交流zero cross point 檢測電路

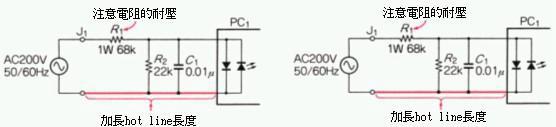

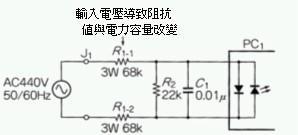

由於商用交流的輸入線相當危險,因此設計電路基板圖案時必需充分考慮絕緣與安全性。圖7 所示雖然R1單獨一個電阻電氣上動作完全相同,不過與商用交流的輸入直接連接的圖案變長,或是流入電阻的電壓變高時,電阻的耐電壓特性會出現問題,因此建議讀者最好分成數個電阻。圖8 的輸入電壓變高時,R1 電力損失會以電壓的二次方增加,此時必需改佣可以封裝更大阻抗的電路基板圖案。

圖7 以R1取代圖17的R1-1 R1-2

圖8 加大圖17 的R1-1 R1-2容許電力可支持大電壓範圍

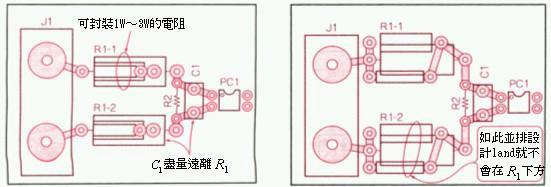

設計圖9 的電路基板圖案,必需考慮下列事項:

①採用full pattern設計,組件盡量緊湊封裝。

②R1 等發熱組件附近設置低高度R1,同時盡量遠離C1。

③R1 設置複數個可以封裝1W,2W,3W 電力阻抗的land。

圖9 電路基板圖案最大缺點是封裝2W,3W 電阻時,會因為實際電阻封裝情況,造成未使用的land 太接近胴體部位;圖10 是設計變更后的電路基板圖案,如此一來R1封裝在任何位置,組件下方不會出現land

圖9 商用交流zero cross point 檢測電路基板圖案 圖10 設計變更后的基板圖案.可發揮24 位解析度的A-D converter 周邊電路基板圖案

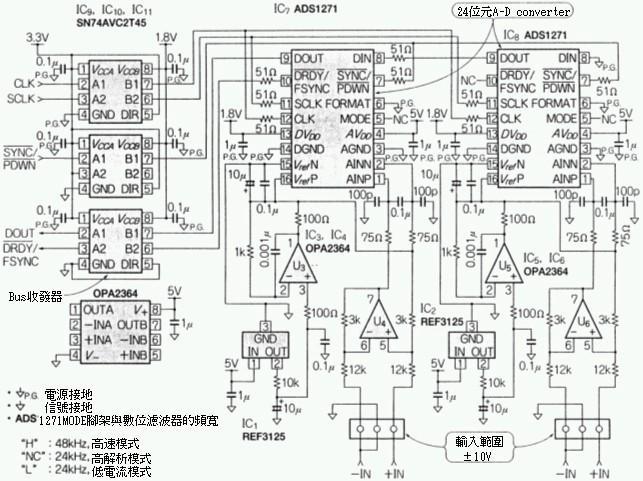

圖11 是由複數個24 位A-D converter 構成,具備電壓測試精度與SN 比最佳化,與直流甚至20kHz 信號的多頻道數據記錄前置器(multi channel data recorder front end)電路圖。本電路亦可應用在3 頻數據記錄器,為達成目的因此將成為ADC的轉換基準的參考(reference)電源REF3125 IC(以下簡稱為REF)當作ADC 與pair 使用,雖然如此設計ADC 頻道之間的gain誤差會增大,不過複數ADC使用共通同的REF,圖案的設計自由度提高,而且容易獲得理想的基板布線設計。

圖11 複數個24 位A-D converter 構成的多頻數據記錄器電路

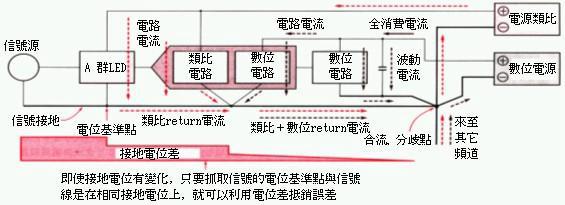

圖12 是從信號源一直到電源的過程中產生的接地電位差統計一覽、上述電路為模擬/數字混載電路,因此接地會有模擬/數字電流流動,如果處理錯誤的話數字電路的return 電流,會混入模擬接地變成噪訊源。

圖12 接地電流的種類與接地電位差的統計一覽

此外各電路的電流是由電源的正極提供,再折返至供給元的負極,因此設計上利用此特性,設置return電流合流點與分歧,點使通行路徑明確分隔。初段的模擬電路(前置增幅器)根據本身的電位基準點接受信號電壓,信號源與該電位基準點若與接地的同電位時,正確信號電壓會傳遞至前置增幅器。

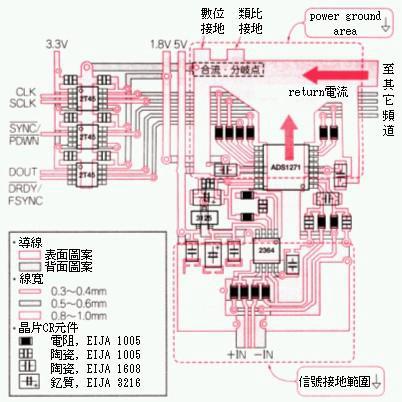

圖12是表示電流的合流與分歧電位差。此外ADC 包含模擬/數字兩種電路兩者的接地之間電位若有動態變化的話,模擬單元會出現耦合(coupling)造成SN 比惡化現象,所以圖13 的ADC直接連接在與地電位上完全相同位置。圖24 是充分反映以上構想的數據記錄器電路基板圖案,如圖所示寬幅的接地圖案在ADC 與OP 增幅器正下方通行,它除了達成低接地阻抗化之外,還兼具對IC晶元的遮蔽(shield)效果,尤其是電路內層或是背面設有可以傳輸脈衝信號的圖案時,通常都可以獲得極佳低接地阻抗與遮蔽效果。

圖13充分反映圖12 的構想的數據記錄器電路基板圖案

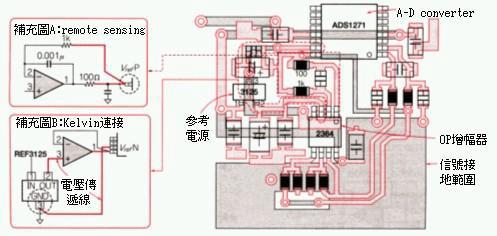

圖14 是基板背面圖案,圖中的補充圖A又稱為remote sensing手法。雖然OP增幅器的輸出部設置利用電容負載防止波動的電阻,不過只要插入包含該電阻與VrefP電位的復歸loop,就能夠正確將參考電壓傳至VrefP。補充圖B 則稱為Kelvin連接手法,由於OPA2346 的第2 與第3 腳架之間會產生參考(reference)基準電壓,因此直接在VrefP至VrefN 之間鋪設電壓傳輸線,如此就可以防止return電流波動產生電壓誤差

圖14 可以提供A-D converter 良好參考電壓的電路基板

[admin via 研發互助社區 ] 模擬電路基板導線設計已經有4517次圍觀

http://cocdig.com/docs/show-post-44229.html