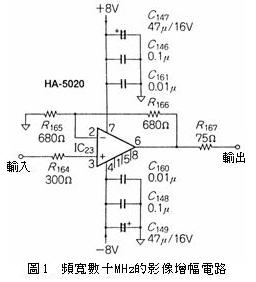

模擬信號尤其是類似0~數十MHz video信號寬頻電路時,電路圖上詳細標示信號的流動路徑與組件位置非常重要。圖1 是電流復歸型video 用OP 增幅器HA-5020 構成的影像增幅電路(video amplifier)。傳統電壓復歸型OP增幅電路,gain一旦變大時頻寬會降低,相較之下電流復歸型OP增幅電路,由於理論上頻寬取決於復歸阻抗值決,因此不受gain的影響可以獲得較大頻寬。如圖1 所示從左側輸入的video信號,利用 (HA-5020)構成的OP增幅器增幅2 倍之後輸出至右側。

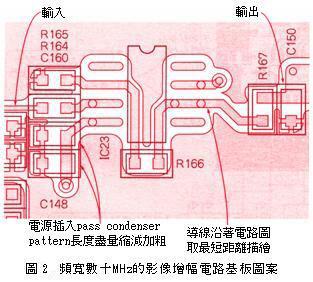

圖2 是頻寬數十MHz 的影像增幅電路基板圖案,頻率一旦進入影像頻寬範圍時,電路基板的設計直接影響電路特性,尤其是最短距離的連接,同時沿著電路圖的流動路徑設計基板圖案非常重要。根據以上觀點比較圖1 與圖2 時,可以確定信號的流動路徑與組件的設置,幾乎與圖1 電路圖完全一致。

若影像增幅電路使用晶元型組件,一般比較容易獲得預期的動作特性,如果使用傳統導線組件,導線的電感成份可能會影響電路特性。

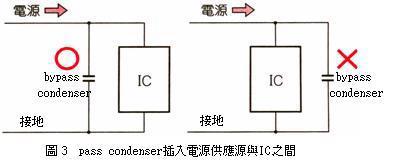

如圖1所示提供IC的電源與接地之間插入旁通電容(bypass condenser),此外圖1與圖2 IC腳架附近分別插入47μF電解電容,與並聯的0.1μF、0.01μF陶瓷電容,接著再用粗短圖案連接,由於受限於組件封裝空間,因此等組件封裝在圖2 電路基板的背面。如圖3(a)所示電源供給源與接地之間插入旁通電容,如果從3(b)IC的右側插入,就無法發揮旁通電容的功能。

D-A converter 周邊模擬-數字電路的布線圖案分離技巧

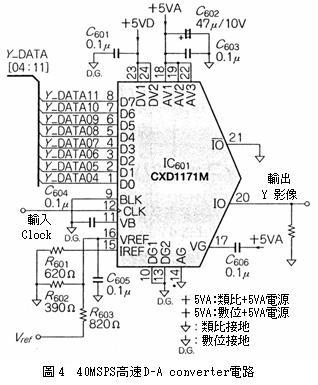

D-A converter 與後述的數字影像編碼器(digital video encoder),是模擬介面輸出不可或缺的LSI,由於基板上混載模擬與數字信號,因此電路基板圖案的設計非常重要。

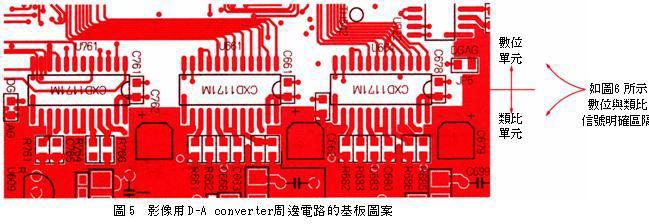

此處以SONY 開發的8 位,40MSPS高速D-A converter CXD1171M為例,介紹電路基板圖案設計技巧。圖4是CXD1171M 40MSPS高速D-A converter 的電路圖;圖5 是使用3 個影像用D-A converter CXD1171M的周邊電路基板圖案。

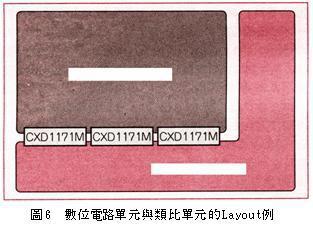

設計模擬與數字電路混載的基板圖案時,必需注意兩電路的隔離(isolation),如果隔離不完全會發生crosstalk,以及數字電路的噪訊(noise)重迭至模擬電路等現象,因此設計階段必需考慮組件與布線數量,最後才能決定模擬與數字電路block的大小與位置(圖6),組件則分別封裝在各block內,接著進行圖案布線Layout。

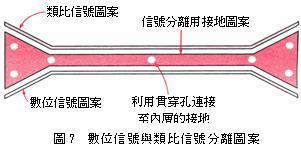

設計上避免模擬信號圖案貼近數字信號圖案或是兩信號圖案平行並排,如果基板結構兩信號圖案有鄰近之虞時,圖案之間必需插入接地圖案(ground pattern),藉此分隔兩信號(圖7)。

以上介紹單面電路基板布線圖案設計技巧;雙面電路基板的場合必需檢查數字電路圖案是否與模擬電路圖案交叉、重迭,圖案層間盡量插入接地層,同時還需使用具備遮蔽(shield)效果的4 層以上多層電路基板;模擬電源與數字電源由基板上相同電源提供時,盡量由低阻抗電源連接單元提供。

可確保模擬信號精度的數字影像編碼器電路基板圖案

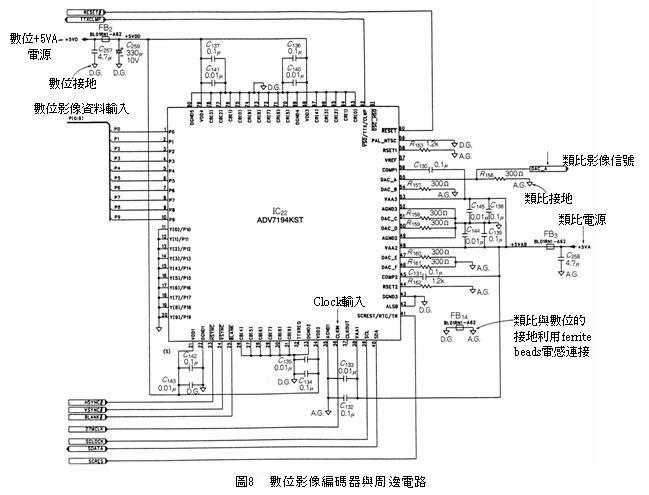

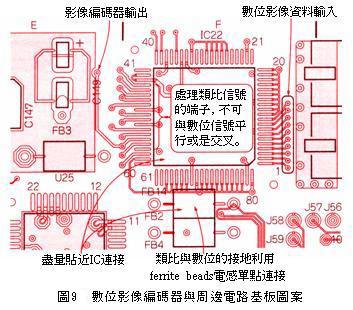

圖8 是數字影像編碼器ADV7194與周邊的電路圖;圖9 是數字影像編碼器與周邊電路基板圖案。數字影像編碼器主要功能是將數字影像數據轉換成組合(composite)信號與Y/C等模擬影像信號。

圖8 電路圖中的ADV7194會針對27MHz 高速頻率(clock),輸入數字信號進行數字編碼器,接著再從高精度10位D-A converter 輸出模擬影像信號。一般影像編碼器等D-A轉換電路或是A-D 轉換電路,為降低噪訊通常會將模擬與數字的接地分開,此時基於兩接地的電位能變成一致等考慮,盡量靠近IC附近作單點連接。不過本電路並未作單點連接,而是利用Ferritebeads防止數字接地的噪訊流入模擬接地。

如圖9 所示ADV7194左側的44~58 pin變成模擬信號,其它三邊的腳架則變成數字信號,此處必需注意兩信號的導線圖案不可平行或是交叉,此外模擬信號系需作full ground,因此ADV7194 左側與內層為full ground結構。

隨著頻率高頻化接地的阻抗也大幅增加,數字電路的信號越高速噪訊量也越多,模擬信號微小變化可能會因為噪訊的滲入無法獲得預期的精度,為了使類似ADV7194 高速、高精度IC發揮功能,因此必需降低基板圖案的接地阻並抗抑制噪訊。

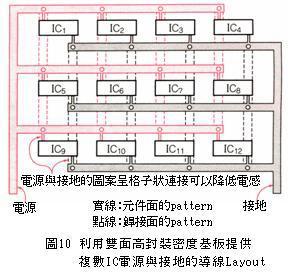

降低基板圖案的接地阻抗可以採用full ground設計,雙面電路基板的場合,組件盡量作單面封裝,背面作full ground設計;高密度封裝卻無法作full ground設計時,組件可以封裝在寬度較大的圖案上(圖10),雖然這種方法可以有效降低阻抗,不過反面缺點是噪訊處理相當棘手。

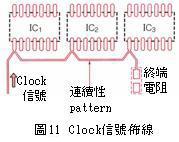

成本允許的範圍下建議改用多層電路基板,因為內層基板具有電源層、接地層結構,所以多層電路基板可以降低電源與接地的阻抗;基板表層無法布線、內層基板有布線圖案設計,或是利用複數的電源電壓細分電源層時必需增加基板層數,類似圖9 的場合建議使用6 層電路基板。各數字IC的頻率端子為了減輕反射波的影響,一般會使用圖11 的筆直性圖案連接,組件的封裝設計則需考慮頻率信號圖案的Layout方便性。

可精確傳輸25~165Mp/s差動介面的電路基板圖案

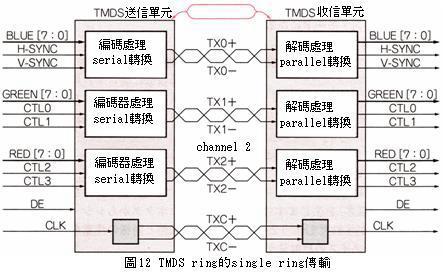

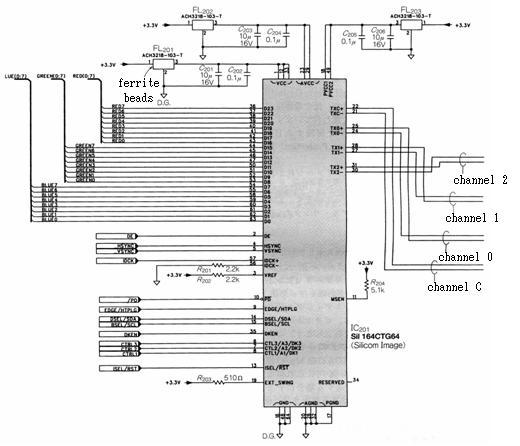

99 年DDWG(Digital Display Working Group)正式公布的DVI(Digital Visual Interface)規範,DVI主要應用在PC與顯示器之間的影像傳輸,爾後隨著HDMI(High Definition Multimedia Interface)規格化之後,DVI 立即被HDMI 取代,成為消費性電子產品數字介面主流,不論事DVI或是HDMI內部都設有保護digital contents 的HDCP(High-bandwidth Digital Content Protection)。DVI 的影像傳輸使用Silicon Image 公司開發的TMDS(Transition Minimized

Differential Signaling)ring技術,TMDS可分為single ring與dual ring兩種。

一個畫素數據24 位(R、G、B各8位),加上2位同步信號與4 位控制數據,變成30 位再經過編碼處理后,轉換成三頻(channel)10位serial數字信號,三頻信號依照畫素頻率(pixel clock)以4 對(pair)差動信號傳輸時稱為single ring(圖12)。

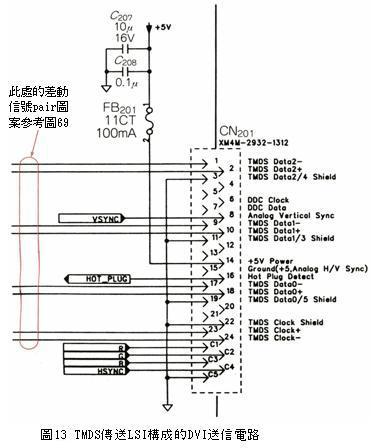

single ring傳輸極限大約是162Mp/s(UXGA)(p/s: pixel/second),超過該速度傳送影像,必需改用dual ring方式。dual ring使用6 頻,它會隨著畫素頻率傳,輸兩畫素數據48 位(R、G、B各8位×2 畫素)、10 位控制數據。圖13 是TMDS 傳送器(transmitter) LSI SiI164 構成的DVI送信電路。

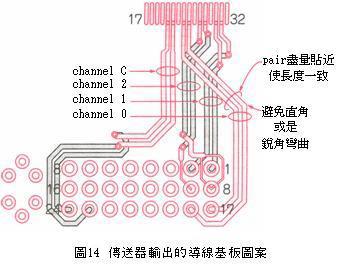

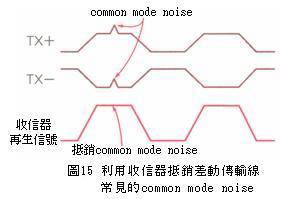

圖14 是上述傳送器的電路基板基板圖案。設計DVI送信電路基板基板圖案時,必需注意傳送器的輸出布線圖案,由於傳送器的各輸出頻道屬於差動信號對(pair),雖然差動信號對不易受噪訊影響,而且噪訊的釋放非常少,不過布線圖案設計不當時就無法發揮上述特徵,因此差動信號對盡量鄰近設置,即使噪訊重迭變成common mode也會被接收器抵銷,而且抵銷時還會朝抵銷磁界的方向,因此可以抑制噪訊的放射(圖15)。

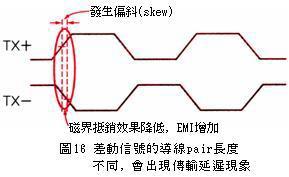

差動信號對之間必需維持一定的距離,同時還需整合pair 的Layout位置與導線的彎曲位置,因為pair 之間維持均衡對差動傳輸非常重要。差動信號的導線長度必相同,如果長度不同時會產生傳輸延遲(skew)現象,一旦位相偏移就無法抵銷磁界噪訊放射量則大幅增加(圖16)。

包含差動信號在內幾乎所有高速信號的布線圖案,都非常忌諱直角或是銳角彎曲設計,為降低阻抗變化布線圖案通常都採用 或是曲線彎曲設計。DVI穩定傳輸要素除了送信電路之外,纜線(cable)與收信電路也需列入檢討,例如使用twist pair twinax等平衡纜線等等。此外收信電路從輸入連接器(connector)到接收器LSI之間的布線圖案設計注意事項,與上述送信電路布線圖案完全相同。

同軸纜線作1.485Gbps傳輸的電路基板圖案

所謂SDI(Serial Digital Interface)是指將影像信號轉換成serial數字信號傳輸的介面而言。4:2:2的組件(component)傳輸率為270Mbps,HDTV則高達1.485Gbps。由SDI構成的電路可以利用電視播放台內的同軸纜線,傳輸高解析度的影像數據,除此之外它還可能在輔助性(ancillary)影像數據間隙領域,重迭傳輸audio數據、字幕數據,以及播放台之間的數據。有關HDTV的serial數字介面,在SMPTE 292 規範中有詳細說明,雖然分成同軸纜線介面與光纖介面兩種,不過此處以Gennum公司的IC為例,介紹使用同軸纜線的介面器。

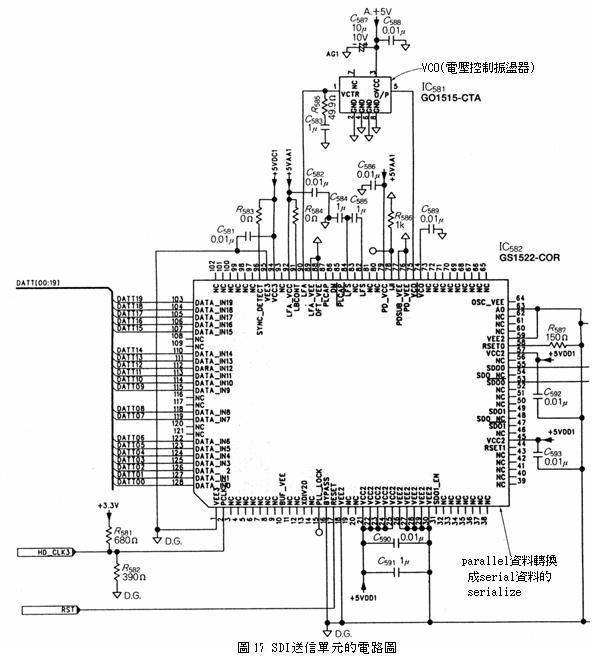

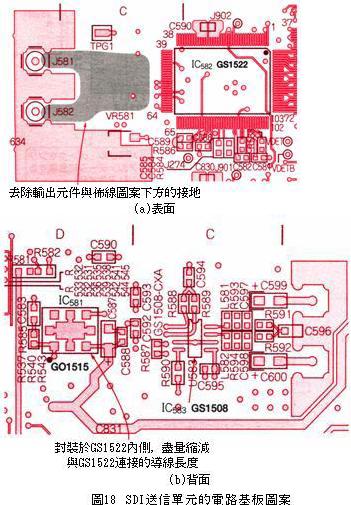

圖17 是HDTV serial digital serialize GS1522、VCO GO1515,與HDTV纜線驅動器GS1508構成的SDI送信單元的電路圖;圖18 是SDI送信單元的電路基板圖案。GS1522是SMPTE274M、SMPTE 260M的parallel數字數據,轉換成SMPTE 292M serial數字信號的IC,該IC可以支持1.485Gbps 與1.485/1.001Gbps;GO1515則是組合serialize與接收器(receiver)的電壓控制振蕩器VCO,它可以接收GS1522的控制電壓,產生1.485GHz或是1.485/1.001GHz的基準頻率給GS1522。

封裝時GS1522 設在基板背面,同時盡量縮短導線長度,GS1508 可以和Gennum公司的IC連接使用,不過也可以當作一般驅動器使用,它是具備兩條75Ω的同軸纜線的纜線驅動器。SDI的輸出屬於1.485Gbps 高速傳輸線路,本電路基板為了降低寄生容量,所以取消輸出組件與布線圖案下方的接地設計。

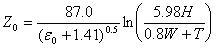

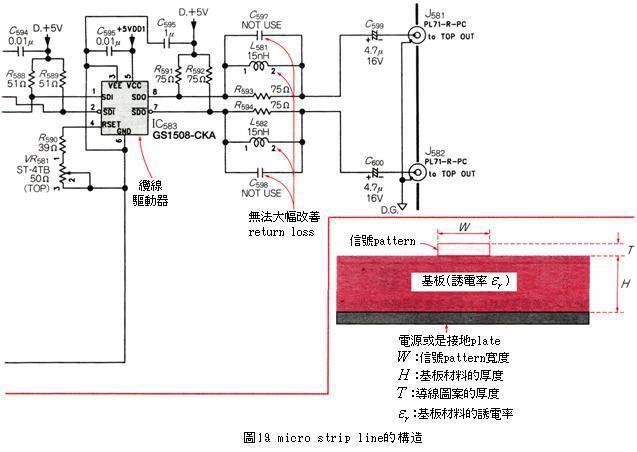

如果布線圖案長度超過1cm時,必需使用micro strip line作特性阻抗整合,1.485Gbps 高速傳輸時,無法沿用傳統的組件與基板處理方式,組件的寄生容量與寄生電感(inductance)必需視為組件範疇處理,在此同時布線圖案必需當作分散封裝的電阻、電容、電感來處理,類似這樣將布線圖案當作組件處理的電路稱為「分佈定數電路」。分佈定數電路中經常使用microstrip line。

圖19 是micro strip line的結構,micro strip line的特性組抗與電路整治,可以作低損失(loss)的的數據傳輸。特性阻抗(impedance)是由布線圖案的寬度W、電路基板圖案厚度W、電路基板厚度H,以及電路基板材料的比誘率εr決定。特性阻抗 可用下列計算式求得:

設計SDI輸出電路必需注意return loss,雖然SMPTE 292M規範與ARIB BTA-S-004B規範的內部有些差異,不過兩者都有限度值的規定。return loss主要是表示阻抗值不整合時的反射波大小,反射值越大表示反射波越小特性越好。

實際上電路基板或是電子設備組裝后,利用網路分析儀(analyzer)測試return loss,如果測試結果不如預期一般只能改變圖17 電路圖中的的值或是重新製作電路板,因此筆者建議設計電路基板時,最好作計算機模擬分析檢討。

[admin via 研發互助社區 ] 寬頻數十MHz video增幅電路PCB的設計技巧已經有6168次圍觀

http://cocdig.com/docs/show-post-44224.html