5、串擾分析

當今飛速發展的電子設計領域,高速化和小型化已經成為一種趨勢。如何在縮小電子系統體積的同時,保持並提高系統的速度與性能成為擺在設計者面前的一個重要課題。信號頻率變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串擾越來越成為一個值得注意的問題。而隨著電子工程師不斷把設計推向技術與工藝的極限,串擾分析變得越來越重要。本節討論的串擾問題是高速、高密度電路設計中需要重點考慮的問題,下面的模擬結果均是使用 Mentor Graphics公司的Interconnect Synthesis(IS)軟體完成的。

5.1、串擾的基本概念

串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓雜訊干擾。過大的串擾可能引起電路的誤觸發,導致系統無法正常工作。

串擾是由電磁耦合形成的,耦合分為容性耦合和感性耦合兩種。容性耦合是由於干擾源(Aggressor)上的電壓變化在被干擾對象(Victim)上引起感應電流從而導致的電磁干擾,而感性耦合則是由於干擾源上的電流變化產生的磁場在被干擾對象上引起感應電壓從而導致的電磁干擾。因此,信號在通過一導體時會在相鄰的導體上引起兩類不同的雜訊信號:容性耦合信號與感性耦合信號。

5.2、幾種典型情況的串擾分析

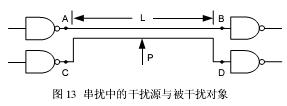

我們以圖 13為例,先來介紹一下串擾的有關術語。圖中如果位於 A點的驅動源稱為干擾源(Aggressor),則位於 D點的接收器稱為被干擾對象(Victim),A、B之間的線網稱為干擾源網路,C、D之間的線網稱為被干擾對象網路;反之,如果位於 C點的驅動源稱為干擾源(Aggressor),則位於 B點的接收器稱為被干擾對象(Victim),C、D之間的線網稱為干擾源網路,A、B之間的線網稱為被干擾對象網路。當干擾源狀態變化時,會在被干擾對象上產生一串擾脈衝,在高速系統中,這種現象很普遍。

為方便下面的模擬,我們組成構造如下的模擬條件:電路布局布線嚴格按照圖 13中兩線系統的結構,設兩線的線寬均為 W,兩線的線間距為 P,而兩線的平行長度為 L,如不特殊說明,W、P和L的取值分別為 W=5mils,P=5mils,L=1.3inches,兩線均為頂層微帶傳輸線。PCB板的參數設置為:

電介質介電常數εr為 4.5,為 8層板(4個信號層和 4個電源層),8層板的順序為:1層頂層信號層,2層電源層(GROUND),3層中間信號層,4層電源層(VCC),5層電源層(GROUND),6層中間信號層,7層電源層(VCC),8層底層信號層。各層之間的電介質厚度均為 7.2mil。信號驅動器和接收器均使用標準 TTL工藝器件的 IBIS模型。以下模擬將 AB線網看作干擾源網路,其信號頻率為 f1,而將 CD線網看作被干擾對象網路,其信號頻率為 f2,f1和 f2的預設頻率均為 20MHz。

(1)電流流向對串擾的影響

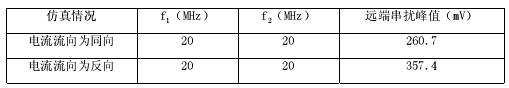

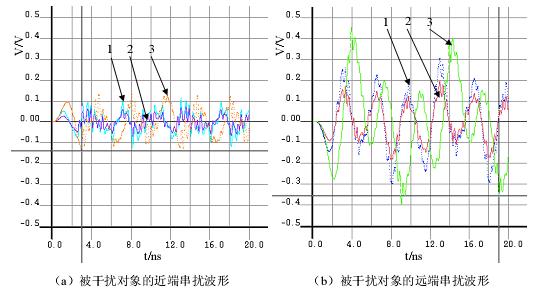

串擾是與方向有關的,其波形是電流流動方向的函數,這裡我們作了兩種情況的信號模擬。第一種情況是干擾源線網與被干擾對象線網的電流流向相同,第二種情況是干擾源線網與被干擾對象線網的電流流向相反(AB線網中的驅動源與負載互換位置,即位於 B點的為驅動源,而位於 A點的為負載),在這兩種情況下,AB和 CD線網都加入 20MHz的信號,表 5.4給出了遠端 D點的串擾峰值,串擾的波形模擬結果如圖 14所示。圖中,左邊圖(a)所示為電流流向為同向時的串擾波形,右邊圖(b)所示為電流流向為反向時的串擾波形,標記“1”和標記“2”箭頭所指的波形分別為被干擾對象遠端 D點和近端 C點的串擾信號波形。

表 2 電流流向不同時的峰值串擾

由模擬結果可知,電流流向為反向時的串擾(遠端串擾峰值為 357.4mV)要大於電流流向為同向時的串擾(遠端串擾峰值為 260.7mV),即圖 14中 AB線網的驅動源與負載交換位置后,雖然信號的頻率沒有改變,但是在被干擾對象上的串擾卻加大了。同時由圖 14可以看到,當改變干擾源信號線上電流的流動方向後,在被干擾對象上的串擾極性也改變了。這說明被干擾對象上的串擾電壓的大小和極性都是與相應干擾源上信號的電流流向有關的。

另外,我們還發現在被干擾對象的負載端 D點的串擾幅值大於被干擾對象驅動端 C點的串擾幅值,這說明遠端串擾是感應耦合累積的結果,因此一般大於近端串擾,這也是為什麼被干擾對象線網的遠端 D點通常被作為考察線網峰值串擾電壓大小的位置,且在串擾抑制中需要被重點考慮的原因。

圖 14 電流流向對串擾的影響

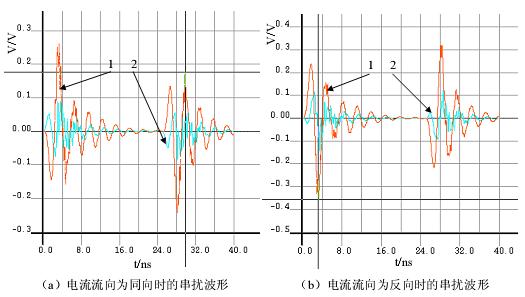

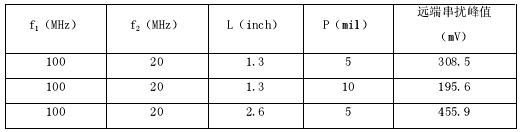

(2)兩線間距 P與兩線平行長度 L對串擾大小的影響

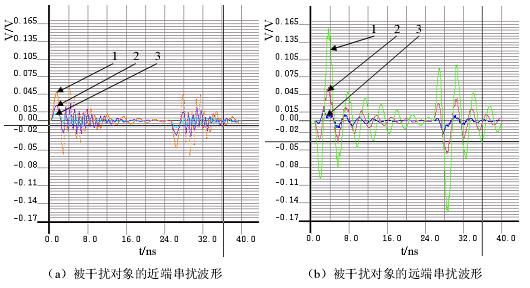

對於圖 13所示的兩線系統,我們進行了三種情況的模擬:第一種情況是在兩線間距和平行長度不變的條件下,探測被干擾對象的串擾;第二種情況是在兩線平行長度不變的前提下,將兩線間距增加到 10mils,然後探測被干擾對象的串擾;第三種情況是在兩線間距不變的條件下,將兩線的平行長度增加到 2.6inches,然後探測被干擾對象的串擾。對以上三種情況的模擬,線網 AB上的信號頻率均為 100MHz。表 3為相應的模擬條件與被干擾對象遠端 D點的串擾峰值,圖 15為兩線間距 P和平行長度 L取不同值時,被干擾對象網路上驅動端與負載端的串擾波形。圖中,標記“1”箭頭所指的波形為兩線間距 P和平行長度 L不變時所對應的初始條件下的串擾信號,而標記“2”和標記“3”箭頭所指的波形分別為兩線平行長度 L不變、間距 P增大一倍和兩線間距不變、平行長度增大一倍時所對應的串擾信號。

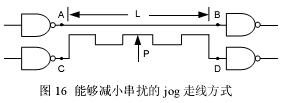

由模擬結果可見,當兩線的間距拉大時(P由 5mils變為 10mils),串擾明顯地減小了,而當兩線的平行長度加長時(L由 1.3inches變為 2.6inches),串擾顯著增大了。由此可知,串擾電壓的大小與兩線的間距成反比,而與兩線的平行長度成正比,但卻不是完全的倍數關係。在實際高速電路中進行布線時,當布線空間較小或布線密度較大時,應慎重對待信號線之間的串擾問題,因為高頻信號線對與其相鄰的信號線的串擾可能會導致門級的誤觸發,而這樣的問題在電路調試的過程中是很難被輕易發現並妥善解決的。因此,在布線資源允許的條件下,應近可能地拉開線間距(差分線除外)並減小兩根或多根信號線的平行長度,必要時可採用固定最大平行長度推擠的布線方式(也稱 jog式走線),即對於平行長度很長的兩根信號線,在布線時可以間斷式地將間距拉開,這樣既可以節省緊張的布線資源,又可以有效地抑制串擾,走線示意圖如圖 16所示。

表 3 兩線間距 P 和平行長度 L 取不同值時的峰值串擾

圖 15 兩線間距P與兩線平行長度 L對串擾大小的影響

圖 16 能夠減小串擾的 jog走線方式

(3)干擾源信號頻率及上升時間對串擾的影響

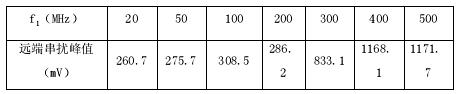

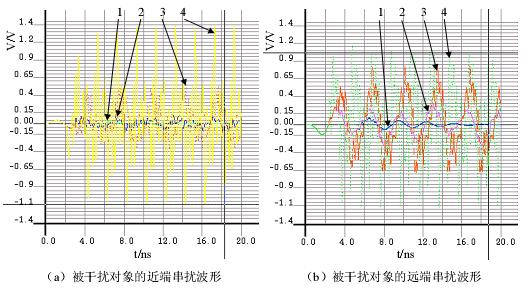

干擾源信號的頻率變化會對被干擾對象上的串擾產生一定的影響,這裡對圖 13中干擾源網路 AB上的信號頻率 f1分別取 20MHz、50MHz、100MHz、200MHz、300MHz、400MHz、500MHz等頻率值時,被干擾對象上的串擾進行了模擬,模擬結果見表 4,同時圖 17給出了 f1分別取 20MHz、100MHz、300MHz、500MHz時的串擾波形,這 4種頻率所對應的波形分別為標記“1”、“2”、“3”、“4”箭頭所指的波形。

表 4 干擾源信號頻率取不同值時對應的峰值串擾

由模擬結果可見,隨著干擾源信號頻率的增加,被干擾對象上的串擾幅值也隨之增加,當干擾源信號頻率取值為 100MHz以上時,峰值串擾增加得很快,而當其頻率為 300MHz以上時,被干擾對象上的串擾已經達到了無法容忍的程度。這說明被干擾對象上的串擾電壓與干擾源信號的頻率取值成正比,當干擾源頻率大於 100MHz時,必須採取必要的措施來抑制串擾。同時,由圖 17還可以看出,當干擾源頻率大到一定程度時,如圖中標記“4”箭頭所指的波形,它對應的干擾源頻率為 500MHz,這時可以明顯看出被干擾對象的近端 C點的串擾已經大於其遠端 D點的串擾,這說明此時容性耦合已經超過感性耦合而成為主要的干擾因素,這種情況下不但要象通常一樣關心遠端串擾,而且需要謹慎處理經常容易被忽略的近端串擾。

圖 17 干擾源信號的頻率變化對串擾的影響

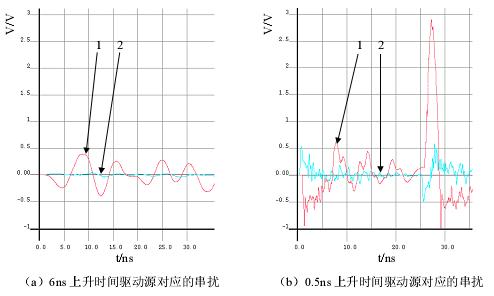

由上面的分析模擬可知,干擾源頻率的增加會導致串擾的增加,但這是否就意味著干擾源頻率較低時,它對被干擾對象的串擾影響就較低呢?答案是否定的。因為存在著一項容易被忽視的對串擾影響極大的因素,它就是干擾源線網中驅動源的上升/下降時間,圖 18是對同一布線結構所作的模擬,不同的是圖(a)和圖(b)中使用了兩個不同的干擾源。對於左邊圖(a)中的串擾模擬,干擾源採用的驅動源是早期工藝的器件,其上升時間為 6ns左右,而右邊圖(b)中的串擾模擬則是基於一個具有0.5ns上升時間的驅動源進行的,圖中標記“1”和標記“2”箭頭所指分別為被干擾對象遠端和近端的串擾波形。由圖可見,對於上升時間不同的驅動源,被干擾對象的遠端串擾峰值由圖(a)中的不到0.5V上升到圖(b)中的接近 3V。在此例中,電路的布局布線結構及其它有關的物理參數都沒有改變,而干擾源信號的頻率不管取多麼低的頻率值,只要採用具有 0.5ns上升時間的驅動源,被干擾對象都會有較大的串擾產生,圖 5.42的模擬結果都是基於干擾源頻率 f1=20MHz時作出的。由此可見,在數字電路中,除了信號頻率對串擾有較大影響外,信號的上升/下降時間或邊沿變化(上升沿和下降

沿)對串擾的影響更大,邊沿變化越快,串擾越大。由於在現代高速數字電路的設計中,具有快速上升時間的器件的應用越來越廣泛,因此對於這類器件,即使其信號頻率不高,在布線時也應認真對待以防止過大的串擾產生。

圖 18 干擾源信號的上升時間變化對串擾的影響

(4)地平面對串擾的影響

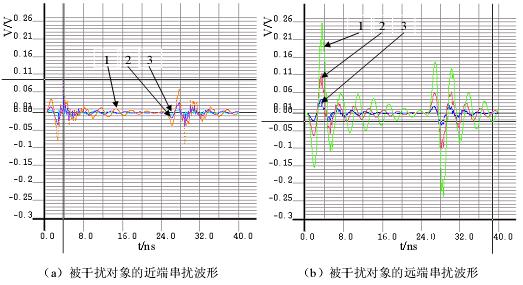

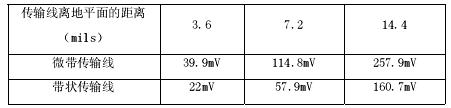

在當今高速系統的設計實現中,多層 PCB板已經被廣泛地用於電路的布局布線中,採用多層PCB板的最大優點是可以在有限面積的條件下,極大地提高布線資源,設計中使用的元器件在布局時即使擺放的很密,也可以通過多層信號走線來實現互連,從而使系統的小型化成為現實。多層 PCB板一般都包括若干個信號層和若干個電源層,多個信號層和電源層的疊放順序沒有特殊規定,但通常是通過疊放順序來構成標準的微帶傳輸線和帶狀傳輸線。對於微帶傳輸線和帶狀傳輸線來說,與之相鄰的一般都有一個電源平面,相應信號層與電源層之間是用電介質填充的。我們知道,這個電介質層的厚度是影響傳輸線特性阻抗的重要因素,當它變厚時,傳輸線特性阻抗變大,當它變薄時,傳輸線特性阻抗變小。實際上,電介質層的厚度對串擾的影響也十分顯著,這裡對圖 13中的兩線系統在布線時分別採用微帶傳輸線(第一層)和帶狀傳輸線(第三層)兩種布線結構進行了模擬,這兩種情況除了使用不同的布線層以外,其它條件如兩線平行長度、間距、信號頻率等均不變。因為二者相鄰的電源平面均有地平面,我們通過改變傳輸線信號層與地平面層之間電介質的厚度(第一層和第二層之間電介質層的厚度,第二層和第三層之間電介質層的厚度)來觀察串擾的變化。模擬結果為電介質厚度 取三個典型值 3.6mils、7.2mils、14.4mils時相應微帶傳輸線和帶狀傳輸線上的串擾。圖 19和圖 20分別為微帶傳輸線和帶狀傳輸線上相對不同電介質層厚度的串擾波形,圖中標記“1”、“2”、“3”箭頭所指分別為電介質層厚度取 14.4mils、7.2mils、3.6mils時相應的被干擾對象的近端串擾波形(圖a)和遠端串擾波形(圖 b)。表 5給出了被干擾對象的遠端峰值串擾。

圖 19 地平面對微帶傳輸線的串擾影響

圖 20 地平面對帶狀傳輸線的串擾影響

表 5 傳輸線離地平面的不同距離對應的遠端峰值串擾

由模擬結果可見,傳輸線與地平面的距離,即傳輸線與地平面之間的電介質層的厚度對串擾的影響很大,對於同一布線結構,當電介質層的厚度增大一倍時,串擾明顯加大了,反之,當電介質層厚度減小時,串擾有明顯減小。另外,由表 5可以看出,對於同樣的電介質層厚度,帶狀傳輸線的串擾要小於微帶傳輸線的串擾,由此可知,地平面對不同結構的傳輸線的影響也是不同的。因此在高速電路布線時,如帶狀傳輸線的阻抗控制能夠滿足要求,那麼使用帶狀傳輸線可以比使用微帶傳輸線獲得更好的串擾抑制效果。

5.3、針對串擾的幾點重要結論

通過以上分析與串擾模擬結果,這裡總結出了一些關於串擾的重要結論,了解這些結論對於高速設計是非常重要的。

首先,串擾具有如下特性:

其次,針對以上這些串擾的特性,可以歸納出幾種減小串擾的主要方法:

[admin via 研發互助社區 ] 高速電子線路的信號完整性設計(三)已經有3341次圍觀

http://cocdig.com/docs/show-post-44454.html