翻譯:Michael Qiao

我們通常認為信號以三種模式沿電路傳播:單端、差模或共模。

單模是我們最熟悉的。它包括介於驅動器與接收器之間的單根導線或走線。信號沿走線傳播並從地返回1。

差模包括介於驅動器與接收器的一對走線(或導線)。我們一般認為其中一根走線傳送正信號而另一根傳送負信號,並且大小相等極性相反,沒有通過地的返回信號;信號沿一根走線前進並從另外一根返回。

共模信號通常更難於理解。既可以包括單端走線也可以包括兩個(可能更多)差分走線。同樣的信號沿走線以及返迴路徑(地)或者沿差分對中的兩根走線流動。大部分人往往對共模信號不熟悉,因為我們自己從來不會故意產生它們。它們通常是由從其它(鄰近或外部)源耦合進電路的雜訊引起的。一般來講,結果最好情況是中性的,最壞情況是具有破壞性的。共模信號能夠產生干擾電路正常運行的雜訊,並且是常見的EMI 問題的來源。

優點:差分信號相比單端信號有一個顯著的缺點:需要兩根走線而不是一根,或者兩倍的電路板面積。但是差分信號有幾個優點:

重要假設:差分信號的一個重要方面常常被工程師或者設計人員忽略,甚至有時被誤解。我們從兩條廣為人知的規則開始:(a)電流在一個閉合的環路內流動以及(b)電流在環路內處處相等。

考慮差分對的“正”走線。電流沿走線流動並且必須在一個環路內流動,通常從地返回。另外一根走線中的負信號也必須在一個環路內流動,通常也從地返回。這很容易明白如果我們暫時想象一個差分對中的一根走線上的電流保持不變。另一根走線中的信號必須從某個地方返回,並且很清楚返迴路徑應該是單端信號的返迴路徑(地)。我們說差分對沒有通過地的返回信號不是因為不能,而是因為返回信號的確存在並且大小相等且極性相反所以相互抵銷了(和為零)。

這一點非常重要。如果從一個信號(+i)返回的信號嚴格等於,且符號相反,另一個信號(-i),那麼它們的和(+i-i)為零,沒有電流從任何地方流過(特別是地)。現在假定信號並非嚴格相等且極性相反。設一個為+i1 另一個為-i2。這裡i1 和i2 的值近似但是不等。返回電流的和為(i1-i2)。因為不是零,這個增加的電流必須從某個地方返回,推測應該是地。

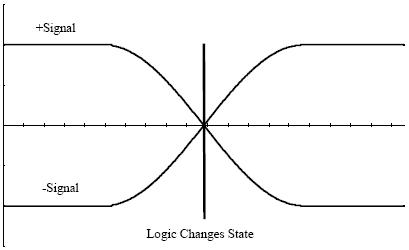

你說什麼?那麼讓我們假定發送電路發送一對差分信號,嚴格相等且極性相反。再假定他們在路徑的終點仍然如此。但是如果路徑長度不等會如何呢?如果(差分對中的)一條路徑比另外一條長,那麼信號在傳輸到接收器的階段就不再是嚴格相等且極性相反了(圖2)。如果信號在它們從一個狀態到另一個狀態的轉變過程中不再是嚴格相等且相反,沒有電流流經地就不再是正確的了。如果有流經地的電流存在,那麼電源完整性就一定成為一個問題,並且可能EMI也會成為一個問題。

圖2:(-)走線比圖1 中短,在紅色箭頭所標示出的範圍內差分信號是大小相等且極性相反不再正確。從而在這個時間片內將有流經電源系統的電流。

設計規則1:我們處理差分信號的第一個規則是:走線必須等長。

有人激烈地反對這條規則。通常他們的爭論的基礎包括了信號時序。他們詳盡地指出許多差分電路可以容忍差分信號兩個部分相當的時序偏差而仍然能夠可靠地進行翻轉。根據使用的不同的邏輯門系列,可以容忍500 mil 的走線長度偏差。並且這些人們能夠將這些情況用器件規範和信號時序圖非常詳盡地描繪出來。問題是,他們沒有抓住要點!差分走線必須等長的原因與信號時序幾乎沒有任何關係。與之相關的僅僅是假定差分信號是大小相等且極性相反的以及如果這個假設不成立將會發生什麼。將會發生的是:不受控的地電流開始流動,最好情況是良性的,最壞情況將導致嚴重的共模EMI問題。

因此,如果你依賴這樣的假定,即:差分信號是大小相等且極性相反,並且因此沒有通過地的電流,那麼這個假定的一個必要推論就是差分信號對的長度必須相等。

差分信號與環路面積:如果我們的差分電路處理的信號有著較慢的上升時間,高速設計規則不是問題。但是,假設我們正在處理的信號有著有較快的上升時間,什麼樣的額外的問題開始在差分線上發生呢?

考慮一個設計,一對差分線從驅動器到接收器,跨越一個平面。同時假設走線長度完全相等,信號嚴格大小相等且極性相反。因此,沒有通過地的返回電流。但是,儘管如此,平面層上存在一個感應電流!

任何高速信號都能夠(並且一定會)在相鄰電路(或者平面)產生一個耦合信號。這種機制與串擾的機制完全相同。這是由電磁耦合,互感耦合與互容耦合的綜合效果,引起的。因此,如同單端信號的返回電流傾向於在直接位於走線下方的平面上傳播,差分線也會在其下方的平面上產生一個感應電流。但這不是返回電流。所有的返回電流已經抵消了。因此,這純粹是平面上的耦合雜訊。問題是,如果電流必須在一個環路中流動,剩下來的電流到哪裡去了呢?

記住,我們有兩根走線,其信號大小相等極性相反。其中一根走線在平面一個方向上耦合了一個信號,另一根在平面另一個方向上耦合了一個信號。平面上這兩個耦合電流大小相等(假設其它方面設計得很好)。因此電流完全在差分走線下方的一個環路中流動(圖3)。它們看上去就像是渦流。耦合電流在其中流動的環路由(a)差分線自身和(b)走線在每個端點之間的間隔來定義。

圖3:即使差分信號嚴格大小相等且極性相反,因而沒有流經電源系統的返回電流,仍然在走線下方的平面中存在在一個環路中流動的感應電流。

設計規則2:現在EMI 與環路面積已是廣為人知了3。因此如果我們想控制EMI,就需要將環路面積最小化。並且做到這一點的方法引出了我們的第二條設計規則:將差分線彼此靠近布線。有人反對這條規則,事實上這條規則在上升時間較慢並且EMI 不是問題時並不是必須的。但是在高速環境中,差分線彼此靠得越近布線,走線下方所感應的電流的環路就越小,EMI 也可以得到更好的控制。

值得一提的是一些工程師要求設計人員去掉差分線下方的平面。原因之一是減小或消除走線下方的感應電流環路。另外一個原因是防止平面上已有的雜訊耦合到(推測如此)走線上的低壓信號4。

還有一個將差分線彼此靠近布線的理由。差分接收器設計為對輸入信號的差敏感而對輸入的共模偏移不敏感。也就是說即使(+)輸入相對(-)輸入僅有輕微的偏移,接收器也會檢測到。但是如果(+)和(-)輸入一起偏移(在同樣的方向),相對而言接收器對這種偏移不敏感。因此如果任何外部雜訊(比如EMI 或串擾)等同地耦合到差分線中,接收器將對此種(共模耦合)雜訊不敏感。差分線布得越彼此靠近,任何偶合雜訊在每根走線上就越相近。因此電路的雜訊抑制就越好。

規則2推論:再次假定高速環境中,如果差分線彼此緊挨著布線(為了使其下方的環路面積最小化)那麼走線將彼此耦合。如果走線足夠長以至於端接成為一個問題,這種耦合就會影響到確切的端接阻抗5的計算。原因是:

考慮一個差分線對,線1 和線2。假使它們分別攜帶信號V1 和V2。因為它們是差分線,V2=V1。V1 在線1 引起一個電流I1 而V2在線2 引起一個電流I2。電流必然是從歐姆定律導出,I=V/Z0,這裡Z0 是走線的特徵阻抗。現在線1(舉例)攜帶的電流事實上由i1 和k*i2 組成,這裡k 是線1 與線2 間的耦合比例。這表明這種耦合的最終效果是線1 上的一個明顯的阻抗,這個阻抗等於

Z=Z0-Z12

這裡Z12 由線1 與線2 間的互耦6引起。如果線1 和線2 分得很開,它們之間的耦合就很小,確切的端接阻抗就只是Z0,單端走線的特徵阻抗。但是如果走線靠的更近,它們之間的耦合就會增加,這樣走線的阻抗與這種耦合成比例地減小。這就是說確切的走線端接(為了防止反射)為Z0-Z12,或者某個小於Z0 的值。這對差分對的兩根走線都適用。因為沒有流經地的電流(大概這是個假設)那麼端接電阻被連接在線1 和線2 之間,且確切的端接阻抗算得是2(Z0-Z12)。這個值經常被叫做“差分阻抗”7。

設計規則3:差分阻抗因互耦而變,而互耦因線距而變。因此在任何情況下,走線阻抗,也就是互耦,在全線為常數是很重要的。這就得到了我們的第三個規則:(差分對的)線距必須在全線為常數。

注意對差分阻抗的影響只是規則2 的推論。差分阻抗根本不是與生俱來的。我們要把差分線彼此靠近布線與EMI 和雜訊免疫有關。它對“長”線確切端接以及線距一致性的影響的事實只不過是為了EMI 控制而將走線彼此靠近布線的一個推論8。

結論:差分信號有幾個優點,它們中的三個是(a)與電源系統有效隔離,(b)對雜訊免疫,和(c)增強信噪比。與電源系統(特別是系統地)隔離依賴於差分線上的信號真正地大小相等且極性相反。這個假定也許不成立,如果差分對中單個線長不完全匹配。對雜訊的免疫經常依賴於走線的緊耦合。這將依次影響到為防止反射而對走線進行正確的端接的值,以及如果走線必須緊耦合,通常也是需要的,它們的間距必須全線為常數。

1 事實上信號可以僅僅/同時從地或電源系統返回。在這篇文章中我通篇使用單個術語“地”完全是為了方便。

2 光耦器件是解決這類問題的另一種方法。

3 參見"Loop Areas: Close 'Em Tight", January, 1999

4 據我所知沒有權威的研究支持或者反駁這個慣例。

5 阻抗控制走線在行業中有許多參考。比如,參見"PCB Impedance Control: Formulas and Resources", March, 1998; "Impedance Terminations: What's the Value?" March, 1999; 和"What Is Characteristic Impedance" by Eric Bogatin, January, 2000, 第18 頁。

6 參見"Differential Impedance: What's the Difference", August, 1998

7 對線對的差模及共模成分的有趣討論,參見"Terminating Differential Signals on PCBs",Steve Kaufer and Kellee Crisafalu, March, 1999, 第25 頁。

8 其它彼此靠近布線的走線(比如受串擾的走線)沒有發生這種情況的原因是其它走線之間沒有很好的互耦——例如大小相等且極性相反。如果耦合信號只是隨機地彼此相關,平均耦合是零並且對端接阻抗沒有影響。

這篇文章在Printed Circuit Design 發表,一種CMP Media 的刊物,2001 年10 月.2001 CMP Media, Inc. .2001 UltraCAD Design Inc. http://www.ultracad.com

譯者的話:

本人是一個PCB 設計人員,從Douglas Brooks 博士的文章中獲益良多,因此萌生翻譯這些文章的念頭。文中肯定還有諸多紕漏、謬誤,歡迎大家批評指正。同時也歡迎大家來信與敝人探討技術上的問題。

[admin via 研發互助社區 ] 差分信號-生存法則已經有4361次圍觀

http://cocdig.com/docs/show-post-44268.html