一、 實驗目的

(1) 學慣用MAX+Plus II開發系統對可編程邏輯器件編程的方法;

(2) 學習“CPLD/FPGA數字發展實驗箱”的使用方法以及把文件下載到CPLD晶元中的方法。

二、 模擬電路設計及設計思路

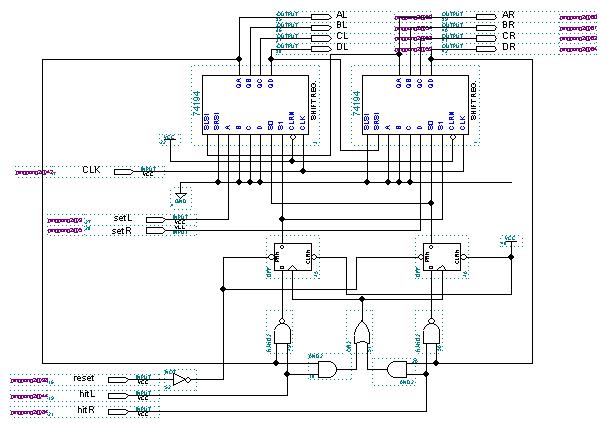

模擬電路圖如圖所示。具體的電路接法及工作原理說明如下:

用兩個74LS194四位雙向移位寄存器模擬乒乓球台,其中第一個74LS194的DL輸出端接第二個的右移串列輸入端,這樣當乒乓球往右準備移出第一個寄存器的時候就會在時鐘脈衝的作用下被移入第二個寄存器。同樣道理,第二個74LS194的AR輸出端接第一個的左移串列輸入端。

由於檯面只能有一個乒乓球,以及乒乓球到達球台末端就出界,所以第一個74LS194的右移串列輸入端及第二個的左移串列輸入端接低電平。

複位端操作原理如下:複位端reset通過非門接到兩個D觸發器的置1輸入端,使兩個D觸發器的輸出端Q均為高電平。這時兩個移位寄存器的控制端S0、S1均為高電平,移位寄存器處於并行輸入狀態。由於乒乓球在發球的時候只能處於球台的兩端,因此第一個寄存器的A輸入端接setL發球控制開關,第二個寄存器的D輸入端接setR發球控制開關,而兩個寄存器的其它并行輸入端都接低電平。

運動員擊球原理如下:假設現在乒乓球在球台的左側,AL輸出端為高電平,這裡運動員擊球,hitL為高電平,AL和hitL通過與門和非門給兩個D觸發器形成時鐘脈衝,這時第一個D觸發器的D輸入端為低電平;由於DR為低電平,第二個D觸發器的D輸入端為高電平。於是hitL產生脈衝的結果是Q1=0,Q2=1。這兩個電平作用到移位寄存器上就是:S0=1,S1=0。這兩個控制端電平使寄存器產生右移信號。右邊的運動員擊球的情況類似。

需要特別說明一下:上面的設計電路圖在擊球脈衝(hitL和hitR)的設計上與實驗指導書的設計稍微有點不同。在非門的兩個輸入端分別加了一個與門。這樣只有在乒乓球在球台左邊的時候hitL才能對D觸發器形成時鐘脈衝,只有乒乓球在球台右邊的時候hitR才能對D觸發器形成時鐘脈衝。也就是說,運動員過早或過晚揮拍都無效。

而按照指導書的原圖,運動員過早或過晚揮拍都會使移位寄存器的S0=1,S1=1,也就是說,遊戲重新回到開始狀態。我認為我的設計更加符合實際邏輯。

三、 模擬結果及結果分析

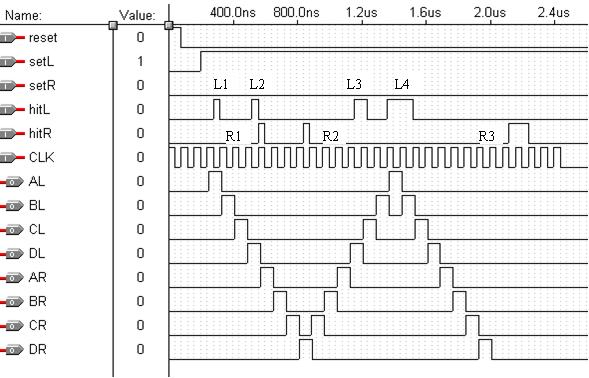

對以上電路圖進行模擬,模擬的波形圖如下:

首先裁判按下reset按鈕,對電路進行複位操作(複位不能長時間按下),然後打開setL開關,左邊的運動員發球。此時setR需一直保持低電平。

各擊球脈衝說明如下:

L1表示左運動員正常擊球,乒乓球往右移;

R1表示右運動員過早擊球,由於電路在設計時在非門的輸入端加了與門,因此R1不能對D觸發器形成時鐘脈衝,擊球無效,乒乓球繼續往右移;

L2表示左運動員隨意揮拍,和R1的結果一樣,球繼續往右移;

R2表示右運動員正常擊球,乒乓球被擊后改為往左移;

L3表示左運動員過早擊球,不影響球的運動;

L4表示左運動員正常擊球,乒乓球被擊后改為往右移;

R3表示右運動員過晚擊球,乒乓球出界。

四、 實驗總結

CPLD的出現使得實現電子設計自動化變得更加簡單。我們在設計的時候就可以花更多的時間進行抽象思維勞動,花更多的時間在電路原理的設計上,而不必去考慮電路實現的物理細節。同時,在設計的時候要盡量使電路的模擬結果更加符合實際邏輯。如本實驗中,運動員過早擊球的結果是本次擊球無效,過晚擊球的結果是球出界,而不是像原先指導書設計的那樣:移位寄存器進行并行輸入狀態,從而左邊或右邊的運動員重新發球。總而言之,要使電路的設計儘可能貼近實際邏輯,做到更人性化,這些都需要我們下大功夫。

[admin via 研發互助社區 ] CPLD打乒乓球遊戲電路模擬設計已經有2858次圍觀

http://cocdig.com/docs/show-post-43038.html