實例1:利用Modelsim 對Xinlinx 公司Virtex-II 產品DCM 模塊進行模擬。

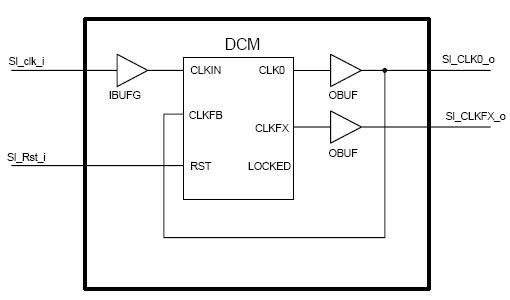

如圖1 所示。

圖1 基於Virtex-II 系列DCM 的模塊設計圖

Sl_Clk_i 為100MHz 的輸入時鐘,Sl_Rst_i 為複位控制信號,輸入時鐘經過一輸入緩衝器后輸入到DCM 的CLKIN 端,通過參數設置,我們分別設置無相位差控制,相位差3.5ns 和相位差4.2ns,利用Modelsim 對以上三種情況分別進行模擬得到的結果如圖2(a)(b)(c)所示:

圖2 相位延遲的Modelsim 模擬波形

從模擬結果來看,在無相位差控制的情況下,輸出時鐘相位延遲了2.38ns,在相位差為3.8ns 時,從圖2(b)看出,輸出時鐘提前了近1.12ns,圖2(c)中可以看出在相位差為4.2ns 的情況下,得到的輸出時鐘又向前提前了720ps。

通過實際測試分別得到圖3(a)(b)(c)所示的波形圖,從圖3(a)可以看出,在沒有相位差控制的情況下,輸出時鐘相位推遲了4.24ns,當將輸出時鐘相位差為3.5ns 時,從圖3(b)可以看出,輸出時鐘相位還延遲了720ps,圖3(c)顯示了在相位差4.2ns 的情況下,輸入時鐘與輸出時鐘相位幾乎完全一致。

(a) 無相位差控制的測試波形

(b) 相位差3.5ns 的測試波形

(c) 相位差4.2ns 的測試波形

圖3 相位差的示波器實測波形

從實測波形與模擬波形的比較可以看出,模擬結果與實測結果還是比較吻合的,兩者結果差別僅為1.88ns,造成這種差異的原因在於這麼兩個原因:

實例2:利用Modelsim 對亞穩態設計進行模擬及糾錯

在具有非同步設計的數字電路中,經常會由於數據的建立時間或保持時間不夠的原因而造成亞穩態的錯誤。我們曾經在設計中曾經利用時鐘鎖存數據,但在設計過程中出現了數據建立時間和保持時間不夠的情況,通過Modelsim 進行模擬,我們發現,數據輸出端的採集數據出現錯誤,如圖4(a)所示。為了糾正這一錯誤,我們一方面在設計中將時鐘信號經過門延時對時鐘的相位進行相應調節,另一方面利用較快的時鐘對數據進行同步處理,然後再用調節后的時鐘進行數據採集。再用Modelsim 進行模擬,發現數據輸出端的採集數據符合採集要求,如圖4(b)所示。

(a) 亞穩態采數錯誤

(b) 修改後的設計采數正確

圖4 亞穩態問題示意圖

[admin via 研發互助社區 ] Modelsim 的驗證實例已經有2686次圍觀

http://cocdig.com/docs/show-post-43155.html