一、主要環境參數是:

modelsim SE 6.1b+Quartus II 5.1 SP2

HDL 是verilog。

器件是Stratix II EP2S90F1020

採用兩種方法設計ROM,ROM的容量是1000×2×16bit。因為需要COS 和SIN 兩種數據。

第一種採用Altera 的LPM 生成ROM,ROM 的內容也是利用Quartus 生成hex 文件,之所以不採用mif 文件的原因是因為在modelsim不支持。

第二種是使用VC 編寫一個小程序,採樣case 語句來生成COS.v 和SIN.v 文件。

二、modelsim環境設置。

在modelsim 的安裝目錄下把modelsim.ini 文件的只讀屬性去掉,在[vsim]字樣下面添加

Veriuser = D:/Programs/altera/quartus51/eda/mentor/modelsim/convert_hex2ver.dll

有些網友說convert_hex2ver.dll 文件無法找到,是因為目錄不對,不是什麼dll directory,在自己quartus 的安裝目錄中搜索就可以找到的。另外注意要使用/代替。

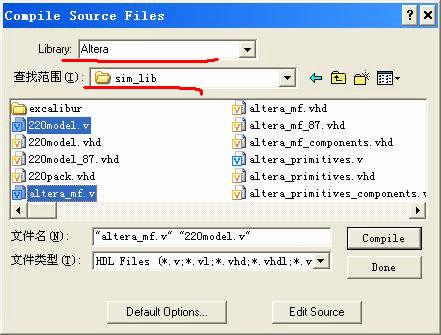

新建一個名稱為Altera 的庫,注意名稱不能是別的。至於放哪裡看個人的喜好,因為這是放置Altera 模擬庫的地方。然後按照下圖編譯quartusedasim_lib 下兩個.v 文件,因為我只用verilog HDL。

下面就可以在modelsim 裡面做模擬了。在編譯完文件后,在命令行裡面輸入vsim,然後在Design 的work 選擇要模擬的實體,在libraries 裡面選擇生成的Altera 庫,如下圖。

三、兩種設計ROM 的方法比較。

第一種資源佔用32000bit 和13ALU。這和1000×2×16bit 的設計容量一致。

第二種則佔用34816bit 和13ALU,相當於每個ROM多了1024bit,如果把case 中default輸入從高阻態(z)改為0,則佔用32768bit,即8 個M4K。

結論,Altera 的LPM 能最大程度優化自己器件資源,但移植性很差,使用case 生成的方法移植性好,向其他平台比如xilinx 的器件上移植不需要修改代碼,但多佔資源。

最後說一下,在modelsim 裡面模擬的時候,如果採用計數器產生地址,計數器一定要賦初值,定義的時候就可以賦,儘管綜合的時候被優化,但沒初值,modelsim 默認是高阻,計數器可能不動作,導致模擬無法進行。

[admin via 研發互助社區 ] modelsim模擬ROM已經有3355次圍觀

http://cocdig.com/docs/show-post-43052.html