邏輯器件的分類方法有很多,下面以邏輯器件的功能、工藝特點和邏輯電平等方法來進行簡單描述。

1:TTL和CMOS器件的功能分類

按功能進行劃分,邏輯器件可以大概分為以下幾類: 門電路和反相器、選擇器、解碼器、計數器、寄存器、觸發器、鎖存器、緩衝驅動器、收發器、匯流排開關、背板驅動器等。

1)門電路和反相器

邏輯門主要有與門74X08、與非門74X00、或門74X32、或非門74X02、異或門74X86、反相器74X04等。

2)選擇器

選擇器主要有2-1、4-1、8-1選擇器74X157、74X153、74X151等。

3)編/解碼器

編/解碼器主要有2/4、3/8和4/16解碼器74X139、74X138、74X154等。

4)計數器

計數器主要有同步計數器74X161和非同步計數器74X393等。

5)寄存器

寄存器主要有串-並移位寄存器74X164和並-串寄存器74X165等。

6)觸發器

觸發器主要有J-K觸發器、帶三態的D觸發器74X374、不帶三態的D觸發器74X74、施密特觸發器等。

7)鎖存器

鎖存器主要有D型鎖存器74X373、定址鎖存器74X259等。

8)緩衝驅動器

緩衝驅動器主要有帶反向的緩衝驅動器74X240和不帶反向的緩衝驅動器74X244等。

9)收發器

收發器主要有寄存器收發器74X543、通用收發器74X245、匯流排收發器等。

10)匯流排開關

匯流排開關主要包括匯流排交換和通用匯流排器件等。

11)背板驅動器

背板驅動器主要包括TTL或LVTTL電平與GTL/GTL+(GTLP)或BTL之間的電平轉換器件。

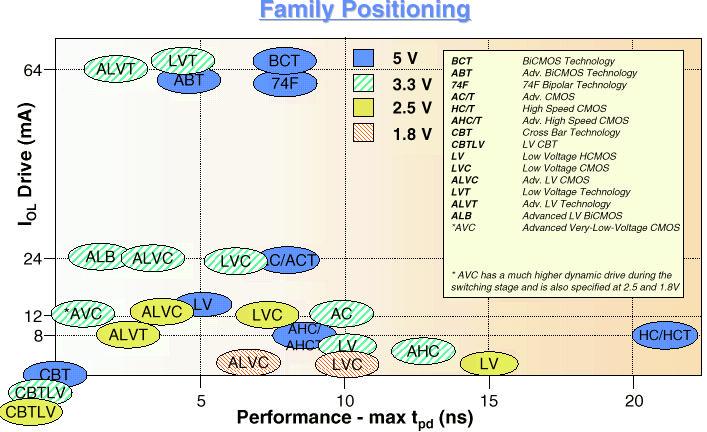

2:TTL和MOS邏輯器件的工藝分類特點

按工藝特點進行劃分,邏輯器件可以分為Bipolar、CMOS、BiCMOS等工藝,其中包括器件系列有:

3:TTL和CMOS邏輯器件的電平分類特點

TTL和CMOS的電平主要有以下幾種:5VTTL、5VCMOS(Vih≥0.7*Vcc,Vil≤0.3*Vcc)、3.3V電平、2.5V電平等。

具體情況可以參考下圖:

圖1:TI公司的邏輯器件示例圖

4:包含特殊功能的邏輯器件

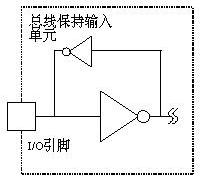

A.匯流排保持功能(Bus hold)

由內部反饋電路保持輸入端最後的確定狀態,防止因輸入端浮空的不確定而導致器件振蕩自激損壞;輸入端無需外接上拉或下拉電阻,節省PCB空間,降低了器件成本開銷和功耗。ABT、LVT、ALVC、ALVCH、ALVTH、LVC、GTL系列器件有此功能。命名特徵為附加了“H”如:74ABTH16244。

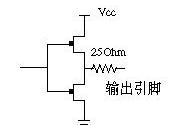

圖2:匯流排保持功能圖 圖3:串列阻尼電阻圖

B.串聯阻尼電阻(series damping resistors)

輸出端加入串聯阻尼電阻可以限流,有助於降低信號上沖/下沖雜訊,消除線路振鈴,改善信號質量。具有此特徵的ABT、LVC、LVT、ALVC系列器件在命名中加入了“2”或“R”以示區別,如ABT162245,ALVCHR162245。對於單向驅動器件,串聯電阻加在其輸出端,命名如SN74LVC2244;對於雙向的收發器件,串聯電阻加在兩邊的輸出端,命名如SN74LVCR2245。

C.上電/掉電三態(PU3S,Power up/power down 3-state)

即熱拔插性能。上電/掉電時器件輸出端為三態,Vcc閥值為2.1V;應用於熱拔插器件/板卡產品,確保拔插狀態時輸出數據的完整性。多數ABT、LVC、LVT、LVTH系列器件有此特徵。

D.ABT 器件(Advanced BiCMOS Technology)

結合了CMOS器件(如HC/HCT、LV/LVC、ALVC、AHC/AHCT)的高輸入阻抗特性和雙極性器件(Bipolar,如TTL、LS、AS、ALS)輸出驅動能力強的特點。包括ABT、LVT、ALVT等系列器件,應用於低電壓,低靜態功耗環境。

E.Vcc/GND對稱分佈

16位Widebus器件的重要特徵,對稱配置引腳,有利於改善雜訊性能。AHC/AHCT、AVT、AC/ACT、CBT、LVT、ALVC、LVC、ALB系列16位Widebus器件有此特徵。

F.分離軌器件(Split-rail)

即雙電源器件,具有兩種電源輸入引腳VccA和VccB,可分別接5V或3.3V電源電壓。如ALVC164245、LVC4245等,命名特徵為附加了“4”。

5:邏輯器件的使用指南

[admin via 研發互助社區 ] TTL和CMOS邏輯器件已經有4401次圍觀

http://cocdig.com/docs/show-post-44696.html