摘要:介紹了外置式USB無損圖像採集卡的設計和實現方案,它用於特殊場合的圖像處理及其相關領域。針對圖像傳輸的特點,結合FPGA/CPLD和USB技術,給出了硬體實現框圖,同時給出了FPGA/CPLD內部時序控制圖和USB程序流程圖,結合框圖和部分程序源代碼,具體講述了課題中遇到的難點和相應的解決方案。

現場圖像採集技術發展迅速,各種基於ISA、PCI等匯流排的圖像採集卡已經相當成熟,結合課題設計了一款USB外置式圖像採集卡。該圖像採集卡已成功應用於一個圖像處理和識別的項目中,由於圖像信號不經過壓縮處理,對後續處理沒有任何影響,因此圖像處理和識別的效果比一般的圖像採集卡要好,滿足了特殊場合的特殊需要。

1 外置式無損圖像採集卡的系統構成

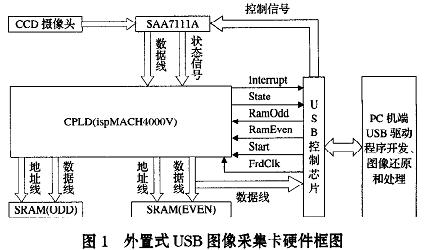

整個無損圖像採集卡由圖像採集、圖像信號的處理和控制、USB傳輸和控制、PC機端的圖像還原和存儲等幾部分組成。

本文介紹的圖像採集卡採集的一幀圖像是720×576象素,如果取彩色圖像,每象素用2個位元組表示,每幀圖像是720×576×16=6480kbps,分成奇數場和偶數場分別存儲在兩片SRAM中,則每片的SRAM存儲3240kbps的圖像數據,因此選用了256K×16=4M位的靜態存儲器(SRAM)。在圖像處理領域,通常只需要黑白圖像,可以只取圖像的黑白部分,每象素用1個位元組表示,每幀圖像是720×576×8=3240kbps,每片SRAM存儲1620kbps的圖像數據。所採用的EZ-USB晶元理論速率是12Mbps,實際測得的速率是8Mbps,因此圖像採集卡每秒傳輸約 1幀彩色圖像或2幀黑白圖像。

當插上圖像採集卡后,PC機會自動識別它。在PC機上,應用程序通過USB向 FPGA/CPLD發送圖像採集命令,CCD攝像頭輸出的PAL制式或NTSC制式的模擬視頻信號通過A/D轉換晶元轉換成數字視頻信號,用 FPGA/CPLD作為採樣控制器,將數字信號存入靜態存儲器(SRAM)中,當完成一幀圖像採集后,FPGA/CPLD向USB發送中斷信號,要求 USB進行圖像數據的傳輸,在PC機端接收USB送來的一幀圖像數據,並且顯示、存儲圖像。文本具體講述了用該採集卡進行黑白圖像的傳輸,整個硬體框圖如圖1所示。

2 外置式無損圖像採集卡的研製

2.1 圖像採集部分

圖像採集部分選用了Philips公司的視頻A/D轉換晶元SAA7111A (EVIP),對SAA7111A的初始化是通過EZ-USB所提供的一對I2C引腳SDA和SCL進行的,在USB固件程序(Firmware)中進行 I2C通信程序的編寫。本系統中SAA7111A的初始設定為:一路模擬視頻信號輸入、自動增益控制、625行50Hz PAL制式、YUV 422 16bits數字視頻信號輸出、設置默認的圖像對比度、亮度及飽和度。SAA7111A晶元產生的數字視頻信號、控制信號和狀態信號送入控制晶元 FPGA/CPLD中,即把場同步信號VREF、行同步信號HREF、奇偶場標誌信號RTS0、片選信號CE、垂直同步信號VS、象素時鐘信號LLC2以及數字視頻信號VPO[15:8]等管腳連接到FPGA/CPLD晶元LC4128V,以便LC4128V獲知各種採集信息。同時,SRAM晶元的讀寫信號、片選信號、高低位元組信號、數據線IO[7:0]和地睛線A[17:0]連接到LC4128V,整個採集過程由FPGA/CPLD晶元LC4128V控制。

在PC機端,通過USB發出圖像採集命令后,FPGA/CPLD進行圖像採集,由於CCD 攝像頭輸出模擬信號,需要經過視頻A/D轉化睛,把模擬視頻信號轉化成數字視頻信號,輸入進FPGA/CPLD晶元,FPGA/CPLD根據狀態信號 RTS0把奇偶場圖像信號分別存儲在SRAM(ODD)和SRAM(EVEN)中。

2.2 圖像信號的處理和控制

這部分是無損圖像採集卡的核心,需要對外圍的器件進行集中控制和處理。FPGA/CPLD 對圖像信號的採集、控制、存儲數據到SRAM以及從SRAM讀取數據都在這裡實現。選用了Lattice公司的新一代產品ispMACH4000V- LC4128V,採用Verilog HDL作為硬體描述語言,但是所編寫的Verilog源程序都適用於FPGA器件,又適用於CPLD器件。

FPGA/CPLD與USB介面部分由七個部分構成(如圖1所示):Start線是拍攝線,它可以向FPGA/CPLD發出圖像採集命令,FPGA/CPLD把當前的奇數場圖像存儲在SRAM(ODD)中,把當前的偶數場圖像存儲在SRAM (EVEN)中;當一幀數據全部存儲完后,發出中斷(Interrupt)信號通知USB晶元;同時用State線作為狀態線,當State線為低電平時,表明USB可以從SRAM讀數據,當State線為高電平時,表明FPGA/CPLD正在向SRAM寫數據;RamOdd用來選擇從SRAM (ODD)中讀取奇數場的數字視頻信號;RamEven用於選擇從SRAM(EVEN)中讀取偶數場的數字視頻信號;FPGA/CLPD輸出的數據線連接至USB和SRAM晶元,再通過USB傳送到PC機;FrdClk線是USB快速讀寫方式輸出的讀選通信號,作為SRAM的時鐘,每來一個時鐘脈衝,地址值就加1,然後將對應地址單元中存儲的數據通過USB傳輸到PC機上。

下面具體描述FPGA/CPLD內部時序控制(如圖2所示)。首先需要產生 FPGA/CPLD內部同步時鐘信號InClk,當FPGA/CPLD向SRAM存儲數字視頻信號時,用SAA7111A的LLC2作為內部同步時鐘信號;當FPGA/CPLD傳輸數字視頻信號時,用USB的讀選通信號FrdClk作為內部同步時鐘信號。當有VS上升沿時,如果RTS0為低電平,則表明是奇數場即將到來,產生LingPai高電平信號,對LingPai取反作用作SRAM(ODD)的寫信號WE1;如果RTS0為高電平,則表明偶數場即將到來,產生LingPaiEven高電平信號,對LingPaiEven取反後用作SRAM(Even)的寫信號WE2,WE1和WE2經過與門后產生圖2中的兩個SRAM的寫選通信號WE。此外,由LingRai和LingPaiEven產生LingPaiAll信號,作為選擇內部同步時鐘的控制信號。由USB晶元產生的Ramodd(OE1)和RamEven(OE2)信號,分別用作SRAM(ODD)和SRAM(EVEN)的讀信號,OE1和 OE2經過與門后產生圖2中的兩個SRAM讀選通信號OE。當LingPaiAll為高電平期間,表示FPGA/CPLD正在向SRAM存儲數據,此時用 WE1作為SRAM(ODD)的片選信號CE1,用WE2作為SRAM(EVEN)的片選信號CE2;當LingPai為低電平期間,表示USB正在從 SRAM讀取數據,此時用OE1作為SRAM(ODD)的片選信號CE1,用OE2作為SRAM(EVEN)的片選信號CE2。

下面闡述FPGA/CPLD如何對數據傳輸進行控制,這部分是個難點(如圖2所示)。這裡只討論如何對奇數場的數字視頻信號進行控制,對偶數場的控制類似於對奇數場的控制,本文不再多述。當LingPai為高電平時,表示FPGA/CPLD向SRAM存儲奇數場圖像數據,此時時鐘為LLC2。當場同步信號 VREF、行同步信號HREF、奇偶場標誌信號RTS0為高電平時,改變相應SRAM的地址信號,並且把數字視頻信號輸出以內部的緩衝器VI,當 LingPai為低電平時,表示USB正在從SRAM讀取奇數場圖像數據,此時時鐘為FrdClk。FPGA/CPLD內部用AddressChange 記錄LingPai的變化,當發現有LingPai變化時,表示讀取數據變成了存儲數據或者存儲數字變成了讀取數據,此時需要把SRAM的地址值變成0。成Verilog中靈活運用了非阻塞型過程賦值(參見下面的源程序),解決了這個技術難點。此外,需要把從SAA711A輸出的數字視頻信號先放在緩衝器 VI[7:0]中,在LingPaiAll為高電平時,通過VO[7:0]輸出到SRAM,保證存儲數據的可靠同步性。這部分Verilog源程序如下:

always @(posedge InCLK)

begin

AddressChange<=LingPai;

if(VREF && HREF && RTS0 && LingPai)

begin VI<=VPO;A<=A +1;end

if(!LingPai && !OE1) begin A <=A +1;

end

if(LingPai!=AddressChange) begin A <=0; end

end

2.3 USB的開發和數據傳輸

Cypress公司推出的帶有USB介面的EZ-USB系列處理器,實現了外圍設備通過 USB介面與PC機進行數據通信。它通過內部RAM編程和數據存儲,使得晶元具有軟特性。USB主機通過USB匯流排下載8051程序代碼和設備特徵到 RAM中,然後EZ-USB晶元作為一個由代碼定義的外圍設備重新連接到主機上(重枚舉)。

USB規範1.1版本定義了USB的四種數據傳輸模式:控制傳輸、同步傳輸、中斷傳輸和塊傳輸,以適應不同應用場合的需求。其中塊傳輸方式提供數據校驗,適用於無誤傳輸大指數據的場合。本課題選用USB的塊傳輸方式,同時採用了EZ-USB的快速傳輸模式,理論速率為12Mbps,實際最高速率能達到8Mbps。

當PC機檢測到USB圖像採集卡已經插上后,PC機可自動地將圖像採集卡的驅動程序裝入操作系統,同時PC機通過USB匯流排下載8051程序代碼和設備特片到USB的RAM中。

USB的開發包括USB的固件程序、Windows設備驅動程序和Windows主機應用程序的編製,限於篇幅,這裡只簡單介紹一下USB固件程序(Firmware)的編製。USB固件程序的具體流程如圖3所示,在源程序的TD_Poll ()中加入了對比度、亮度及飽和度的調節,以做到在硬體上對圖像處理中的上述重要參數的調節,在外部中斷1中完成一幀數據的快速傳輸。

由於採用了外部中斷1,為了避免與USB中斷的衝突,需要在工程中自己編寫一個彙編文件,內容如下:

cseg at 43h

ljmp 1800h

end

此外,在編寫的Keil C源程序中需要加兩句話,以解決USB中斷和外部中斷的地址重疊問題。

#pragma intvector (0x17FD)

#pragma interval(4)

為了增加USB傳輸數字視頻信號的速度,採用USB的快速讀寫模式,在Keil C源程序中內嵌對USB進行寄存器設置的彙編代碼。配置了USB的時鐘控制寄存器,採用全速訪問數據存儲器,MOVX指令在兩個機器周期內實行,時鐘頻率為24MHz,因此USB產生的讀選通寬度為83.3ns。配置埠A,使能PORTACFG(16進位地址為7F93H)寄存器中的快速讀FRD。配置快速傳輸控制寄存器FASTXFR(16進位地址為7FE2 H),採用快速塊傳輸,使能快速讀寫信號。為了將端點2緩衝匹配置成FIFO,增加讀寫速度,8051將端點2緩衝區(IN2)的首地址7E00H裝入自動指針AUTOPTRH(16進位地址為7FE3H)和AUTOPTRL(16進位地址為7FE4H),並且dptr指向AUTODATA(16進位地址為7FE5H),也就是指向了FIFO寄存器,這樣8051可以完全像FIFO一樣訪問端點2緩衝區。

2.4 PC機端的圖像還原

在PC機端,用Visual C++ 6.0編寫客戶應用程序,應用程序通過USB接收原始的奇數場和偶數場圖像數據,待接收完奇數場和偶數場圖像數據后,應用程序把它們組成完整的一幀圖像,並且把該幀圖像數據存儲到硬碟上,然後把這幀圖像轉化成BMP格式的圖像,以BMP格式再次在硬碟上存儲圖像數據,同時以BMP的形式顯示圖像。

3 應用前景

該無損圖像採集卡雖然是針對特殊的圖像處理應用而研發的,但它的作用很廣,能應用於嵌入式系統中的圖像傳輸、集成電路和精密機械領域中的器件定位等。此外,如果用USB2.0代替USB1.1,則能實時傳輸圖像數據到PC機或嵌入式系統,用軟體進行圖像數據的壓縮處理,這塊外置式圖像採集卡可以作為一個很好的實時監控設備,以降低硬體成本。

[admin via 研發互助社區 ] 外置式USB無損圖像採集卡的設計已經有9285次圍觀

http://cocdig.com/docs/show-post-45163.html