1 引言

在目前正進行的北京正負電子對撞機二期升級改造工程(BECPII) 中,北京譜儀(BESIII) 的飛行時間(Time of Flight ,簡稱:TOF) 讀出電子學需要對一種具有25ps 解析度的數據驅動型時間測量器件- HPTDC(High Performance TDC) 進行性能測試。為此,我們設計了一種具有更高精度的專用高精度信號發生器。由於時鐘電路是整個高速數字電路的核心部分,時鐘信號的質量直接影響整個數字電路邏輯的正確性以及整個電路的性能,因此,對信號發生器的時鐘電路進行了大量的PCB 模擬,來研究高速時鐘電路的設計,追求對於時鐘電路設計的最佳方案。

2 模擬工具的選擇

隨著電子線路設計複雜程度的增加,以及人們對於電路性能要求的不斷提高,越來越需要一定的工具對設計進行驗證和性能模擬。Candence 公司提供了一整套完整的電子線路模擬軟體,包括VHDL 模擬、原理圖模擬、PCB 模擬等等,對於電子工程師進行電路設計是十分有幫助的。這裡,利用Candence 提供的強大的PCB 模擬工具SigNoise 來對高速時鐘電路設計進行研究。

利用SigNoise 可以對PCB 設計的信號完整性(Signal integrity) 、電磁兼容性( Electro Magnetic Compatibility) 進行分析,幫助電子設計工程師分析電路的信號傳輸延遲(Delay) 、雜訊容限(Noise Margin) 、串擾(Cross talk) 、電磁兼容性等等,及時修改PCB 設計,以獲得最理想的信號完整性和電磁兼容性。

3 模擬模型的建立

SigNoise 是建立在DML 模型上的一種PCB 模擬工具。DML 模型是一種SigNoise 可以識別的含有晶元輸入輸出信息的模型,可以通過IBIS、QUAD 模型轉化而成。而Candence 本身提供了模型轉換工具Model integrity ,可以在DML、IBIS、QUAD、SPICE 模型之間進行轉換,只要我們獲得上面的一種模型,就可以方便地得到模擬中需要使用的DML 模型。

在這裡,首選IBIS 模型。雖然, IBIS 模型不像SPICE 模型那樣含有晶元的內部信息,但是該模型是目前大多數晶元供應商所普遍提供的,可以方便的從供應商的網站上獲得,而其他模型卻並不是可以容易獲得的。同時, IBIS 模型含有晶元輸入輸出性能的所有信息,完全滿足PCB 模擬的需要。

4 模擬電路的建立

對於時鐘信號達到幾百MHz 的高速電路,時鐘信號的傳輸一般採用ECL 邏輯電平,並通過ECL 器件、無源器件和差分線進行傳輸,所以本文中以信號發生器設計中使用的Motorola 公司的ECLinPS 系列晶元MC100LVEP111 (1:10 差分時鐘驅動器) 和MC100EP131(4 通道的D 觸發器) 為例來研究高速時鐘電路的設計。

模擬電路由MC100LVEP111、MC100EP131 以及一些匹配電阻組成。MC100LVEP111 將時鐘源提供的200MHz 系統時鐘進行1 :10 分配,驅動多個MC100EP131。PCB 上的差分線阻抗控制在100 歐。

5 時鐘傳輸的仿真

1) 輸線的長度對於高速時鐘信號的影響

如圖1 所示,MC100LVEP111 提供200MHz 的時鐘信號作為MC100EP131 的4 個通道D 觸發器的公用時鐘, 改變MC100LVEP111 與MC100EP131 之間傳輸線的長度,對於不同的情況進行模擬,研究傳輸線的長度對於高速時鐘信號傳輸的影響。

圖1 時鐘信號傳輸PCB圖

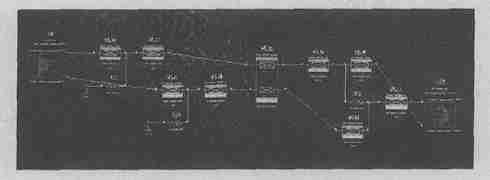

圖2 時鐘傳輸電路DML 拓撲圖

在SigNoise 中,可以得到以上電路的拓撲圖(圖2) ,拓撲圖含有晶元的IBIS 模型信息、傳輸線的長度和阻抗信息、匹配電阻的位置和阻值大小信息,可以對信號傳輸進行十分接近實際PCB 情況的模擬。該電路的模擬結果如圖3 所示。

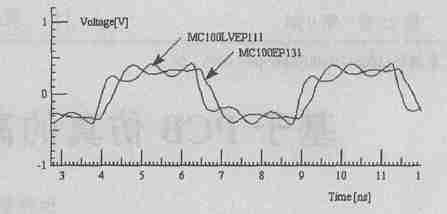

圖3 時鐘傳輸模擬波形

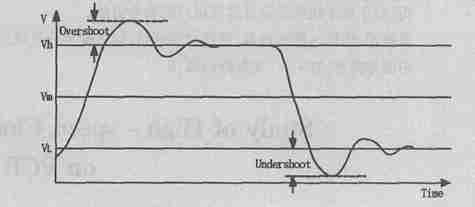

表1 中正向過沖(overshoot) 和負向過沖(undershoot) 的定義見圖4。

圖4 正向、負向過沖的定義

從表1 的數據可以明顯的看出,傳輸線的長度對於高速時鐘信號有很大的影響。傳輸線長度增加,信號的上沖、下沖都顯著增加,傳輸延遲更是大大增加,信號的幅度也有一定的損失。由於時鐘信號的頻率很高,較大的傳輸延遲容易導致時序上的錯誤,從而導致整個電路邏輯的錯誤。因此,在進行高速時鐘電路PCB 設計的時候,要儘可能的縮短時鐘信號的PCB 布線長度,以保證信號的完整性和整個電路的時序。

另外,對於要保證時鐘同步的高速數字電路,時鐘信號PCB 布線的長度更要嚴格控制,以免由於傳輸延遲造成各個時鐘之間的相位差。在信號發生器時鐘電路設計中,使用1 :N 時鐘驅動晶元MC100LVEP111 為多個晶元( 例如MC100EP131) 提供同步時鐘,需要將每個晶元接收到的時鐘信號相位差控制在時鐘周期的1 %以內,即相位差要小於50ps。MC100LVEP111 的各個輸出時鐘信號之間具有25ps 的相位差,所以在PCB 設計的時候,要保證各個時鐘線的長度差造成延遲小於25ps。根據模擬結果,要求各個時鐘線的長度差要小於166mils。由於各個晶元在板上的位置距離MC100LVEP111 各不相同,為了控制時鐘布線長度,使用布“蛇形線”的方式,如圖5 所示。在使用這種方式的情況下,設計的信號發生器時鐘電路中各個時鐘布線長度差最大為50mils。

2) 傳輸線形狀對於高速時鐘信號的影響

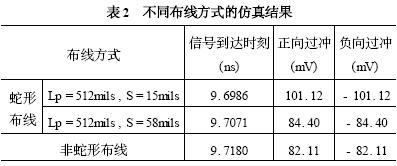

對於圖5 所示的“蛇形”布線方式“, 蛇形”線的間距S ,以及耦合長度Lp ,對於信號完整性有一定的影響,這可以從表2 的模擬結果得到說明。

根據以上的模擬,看到, “蛇形”線的間距越小、耦合長度越大,傳輸線上信號自身的串擾越大,導致信號具有較大的過沖。因此,為了保證信號完整性,在進行“蛇形”布線的時候,只要PCB 空間允許,應該儘可能的增加布線間距,同時減小耦合長度。根據模擬結果,當S > 4H(H 表示信號線距離參考地平面的高度) 時,這種“蛇形”布線帶來的信號串擾可以忽略。

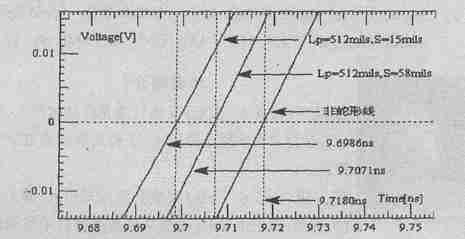

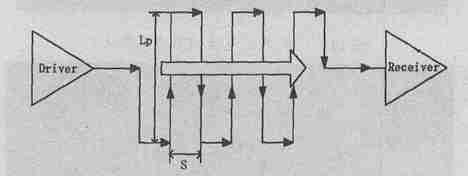

另外,這種“蛇形”布線方式會給信號的傳輸延遲時間帶來影響。圖6 顯示了在不同的布線方式下,信號的前沿到達傳輸線終端的時刻,所有這些時刻都是在差分信號的幅度半高寬處測得的。從這張局部放大圖,可以看到,“蛇形”布線方式時信號前沿比非“蛇形”布線方式時的信號前沿到達的早,同時“, 蛇形”線的間距越小,這個現象越明顯。這是由於在“蛇形”布線方式下,由於并行的距離較近的PCB 連線之間的串擾的影響,一部分信號會垂直的傳輸到接收端(如圖7) ,導致信號的傳輸延遲時間比不採用“蛇形”布線的時候小。“蛇形”線的間距越小,信號之間耦合越緊密,串擾越大,對信號的傳輸時間影響也越大。

圖6 “蛇形”布線對信號傳輸時間的影響

圖7 “蛇形”布線的信號傳輸

3) 匹配方式對於高速時鐘信號的影響

對於ECLinPS 系列的晶元,信號的上升和下降時間非常短,根據傳輸線理論,不加匹配所允許的最大傳輸長度為Lmax ≤tr/ 2td ,約7. 4mm ,所以對於這類高速電路,不加匹配是不可能的,否則就會由於反射導致時鐘信號完整性無法保證。由於ECL 電路為射極輸出電路,下拉電阻也是必不可少的。在PCB 上,下拉、匹配電阻的合理設置對於信號的質量也有很大的影響。下面就對常見的各種匹配方案進行具體的分析。

第一種匹配方式是最常見的標準匹配,即在信號的始端使用兩個510 歐的電阻作為下拉電阻,在信號終端用一個100 歐的電阻跨接在兩個差分線上。根據下拉、匹配電阻的位置,又可分為以下3 種情況:

1) 如圖1 所示。信號線通過始端510 歐下拉電阻的焊盤,終端也是如此。這樣,可以避免由於下拉、匹配電阻的接入而引起的信號線分叉。

2) 如圖8 所示。由於匹配電阻要放置在信號線的最末端,才能達到對整段傳輸線的匹配。所以,在信號線的末端打過孔,將匹配電阻放置在PCB 的另一個元件面,這樣,匹配電阻就可以位於信號線的最末端了。

圖8 下拉、匹配電阻PCB布局情況2

3) 如圖9 所示。有時候,由於PCB 布局緊張,下拉電阻無法與器件放置在同一元件面,這時,可以在信號線上打一個過孔,將下拉電阻放置在PCB 的另一面。

圖9 下拉、匹配電阻PCB布局情況3

第二種匹配方式稱為並聯匹配,電阻放置在信號線的終端,兼作下拉和匹配。這種方式也可以分為兩種情況:

1) 如圖10 所示。將50 歐的電阻放置在信號線的末端,接到VTT電源上。

圖10 下拉、匹配電阻PCB布局情況4

2) 如圖11 所示。這種匹配方式稱為戴維寧匹配,是上一種匹配方式的演變。在信號線的末端對差分線中的每一根分別加50 歐的匹配,上拉電阻130 歐,接到電源上,下拉電阻80 歐,接到地。

圖11 下拉、匹配電阻PCB布局情況5

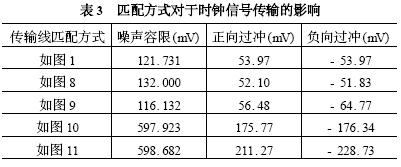

對於以上電路的模擬結果如表3 所示。

(在表3 的模擬中,除了匹配電阻以外,電路的其他部分參數,如信號線長度完全相同。)

比較以上幾種下拉、匹配電阻的設計,可以看到:對於標準匹配方式,圖8 所示的方法為最佳方案,但是若由於PCB 布局所限,不能採用這種方案,也可以用圖1、9 的方式來代替,但是要以損失雜訊容限,增大信號過沖為代價。對於並聯匹配方式,電路的雜訊容限較大,可以避免雜訊干擾而引起的誤觸發,如果電路的雜訊可能會很大,最好使用這種匹配方式。然而,在這種方式下,信號的過沖也很大。對比圖10、11 的匹配方式,圖10 這種方式使用的電阻較少,而且過沖也較小,在性能方面要好於圖11 的戴維寧匹配。但是,這種方案使用了一個額外的VTT電源,增加了電路中電源設計的複雜度。同時,這種匹配方式的功耗也很大,對於ECL 電路來說,功耗一直是一個很大的問題,因此這種方案的運用要根據實際電路的功耗要求以及電路中能夠提供的電源而定。對於戴維寧匹配,則會導致在信號線終端聚集了大量的電阻,對於PCB 上器件的布局和其他布線帶來了一定的困難。因此,對於以上匹配方式的選擇,要根據實際情況具體分析。

在信號發生器的實際設計中,為了追求信號完整性,同時考慮PCB 布局空間的限制,使用了如圖1、圖9、圖10 所示匹配方式。根據模擬(如圖3 所示) ,以及實際的測試結果,可以看到,即使在使用了匹配的情況下,還是會存在反射現象。這主要是由於各種匹配方式還不能夠達到完全的匹配。對於圖1、9、10、11 所示的匹配方式,由於PCB 布局的限制,終端的匹配電阻與晶元的管腳之間還是存在一定的PCB 引線,這就導致匹配並不是對整個傳輸線的完全匹配,帶來了一定的反射。對於圖8 所示的匹配方式,雖然不存在上述問題,但是在這種方式下,晶元管腳處阻抗的不連續性,也會帶來一定的反射。另外,由於電阻在高頻情況下,寄生電容和電感的效應會逐漸明顯,導致阻抗有較大的改變,使實際的信號含有一定的反射。

6 結論

通過SigNoise 的PCB 模擬結果,可以看到,設計高速時鐘電路的時候,由於電路的頻率很高,對於許多問題都要特別注意:

SigNoise 是一個非常有用的模擬工具,它對於PCB 的模擬結果非常接近實際電路的情況,對於電子工程師的電路設計是非常有幫助的。同時,利用這個模擬工具,還可以靈活、方便的研究PCB 設計的一些問題。SigNoise 軟體模擬結果形象直觀、模擬功能齊全、模型庫極易獲得,是一個不可多得的好軟體。

[admin via 研發互助社區 ] 基於PCB 模擬的高速時鐘電路設計研究已經有3841次圍觀

http://cocdig.com/docs/show-post-44243.html