原文作者:Mujtaba Hamid

註:

一個設計的測試驗證是非常重要的。有效的測試可以助我們快速的完成或改善設計。Testbenches建議編寫有效的測試代碼來通過軟體實現可靠的驗證。無意中發現,順手譯為中文,以備將來方便。也貼給沒有找到更好中文版本的同道人。

Testbenches本意應該是測試平台更合理,但是在中文中閱讀起來很不舒服。所以本文中有時譯為“測試設計”,“測試代碼”,有時乾脆是“測試”。

應用筆記為HDL驗證設計的新手,或者是沒有豐富的測試設計經驗的邏輯設計者而編寫。

測試設計是驗證HDL設計的主要手段。本應用筆記為創建或準備和構建有效的測試設計提供準則。它也提供一個為任何設計開發自較驗測的測試設計的一個代數方法。

涉及的所有設計文件可以從以下的站點獲得:

PC: ftp://ftp.xilinx.com/pub/applications/xapp/xapp199.zip

UNIX: ftp://ftp.xilinx.com/pub/applications/xapp/xapp199.tar.gz

由於設計的規模越來越大和越來越複雜,數字設計的驗證已經成為一個日益困難和繁瑣的事。面對挑戰,驗證工程師們依靠許多的驗證工具和方法。對於大的系統,如幾百萬門的設計,工程師們一般使用一套可靠的驗證工具。當然,對於一些小的設計,設計工程師常常發現帶有測試的hdl模擬器就可以做得很好。

測試設計已經成為一個驗證高級語言設計HLL (High-Level Language) 的標準方法。

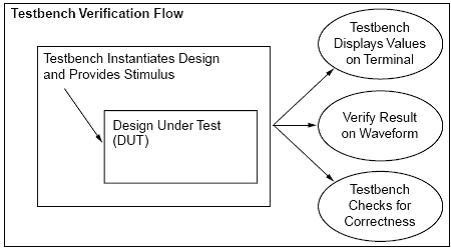

典型的,測試設計完成以下任務:

實現測試設計;

模擬通過使用模塊的測試向量來模擬測試設計;

輸出結果到終端或波形窗口以檢視;

可選擇的將實際結果和預期結果進行比較。

一般測試設計使用工業標準的VHDL或verilog硬體描述語言來編寫。測試設計調用功能設計,然後模擬。複雜的測試設計完成一些附加的功能----如它們包含邏輯來為設計決定適當的設計激勵或比較實際結果和預期結果。

後續的章節說明了一個非常穩定的測試設計的結構,並且提供了一個自較驗測例子----它將自動比較實際結果和測試設計的預期結果。

圖1說明一個基於以上基本要求的標準的hdl驗證流程。由於測試設計使用VHDL或verilogHDL來描述,測試設計的驗證過程可以在不同的平台或不同公司的軟體工具環境完成。另外,由於VHDL或verilogHDL是公開的通用標準語言,使用VHDL或verilogHDL來描述驗證設計可以毫無困難的在將來重用。

測試設計可以用VHDL或verilogHDL來描述.因為測試設計只用來進行模擬,它們沒有那些適應綜合中僅應用的rtl語言子集的語法約束的限制.而是所有的行為結構都可以使用。從而測試設計可以編寫的更為通用,使得它們可以更容易維護。

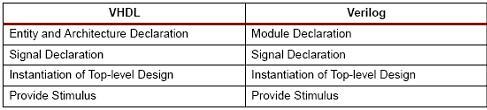

所有的測試設計包含了如表1的基本程序段塊。正如上面所提到的,測試設計一般包含更多的附加功能,如在終端上可視的結果和內建的錯誤檢測。

1 測試設計的基本程序段

下面的例子說明經常使用的測試設計的結構。

使用系統時鐘來的時序邏輯設計必須產生時鐘。重複的時鐘信號可以很容易的在vhdl或verilog源碼中實現。以下是vhdl和verilog的時鐘發生示例。

VHDL:

-- Declare a clock period constant.

Constant ClockPeriod : TIME := 10 ns;

-- Clock Generation method 1:

Clock <= not Clock after ClockPeriod / 2;

-- Clock Generation method 2:

GENERATE CLOCK: process

begin

wait for (ClockPeriod / 2)

Clock <= ’1’;

wait for (ClockPeriod / 2)

Clock <= ’0’;

end process;

Verilog:

// Declare a clock period constant.

Parameter ClockPeriod = 10;

// Clock Generation method 1:

initial begin

forever Clock = #(ClockPeriod / 2) ~ Clock;

end

// Clock Generation method 2:

initial begin

always #(ClockPeriod / 2) Clock = ~Clock;

end

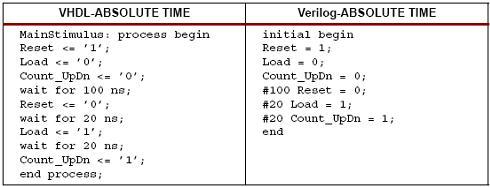

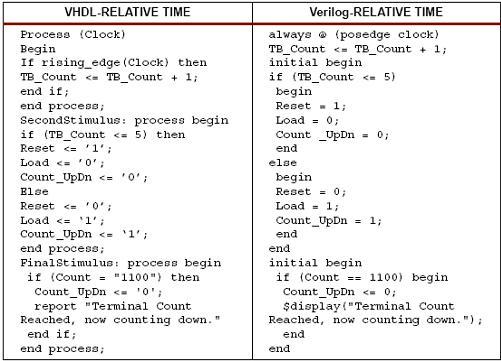

為了獲得測試設計的驗證結果,激勵必須在測試設計中提供。在測試設計中使用的并行激勵塊提供必要的激勵。兩個方法被考慮:絕對時間激勵和相對時間激勵。在第一個方法里,模擬變數被詳細描述為相對於模擬時間零點。通過比較,相對時間激勵提供初始值,然後在重觸發激勵前等待一個事件。根據設計者的需要,兩種方法可以在測試設計中組合使用。

表2絕對時間激勵

表2和表3分別以vhdl和verilog提供了一個絕對時間激勵和相對時間激勵的源代碼。

表3相對時間激勵

VHDL進程塊和Verilog初始塊與設計文件中的其他的進程塊或初始塊同時執行。然而,在每一個進程塊或初始塊中,事件是按照書寫的順序有序的規劃的。這說明在模擬時間零點併發的每一個塊激勵的順序。多模塊應該被用來將複雜的激勵順序分解為有更好的可讀性和方便維護的代碼。

在verilog中推薦使用關鍵字$display 和 $monitor 顯示結果。雖然vhdl沒有等效的顯示指令,它提供了std_textio標準文本輸入輸出程序包。它允許文件的i/o重定向到顯示終端窗口(作為這個技術的示例,參看下面的自較驗查驗證設計)

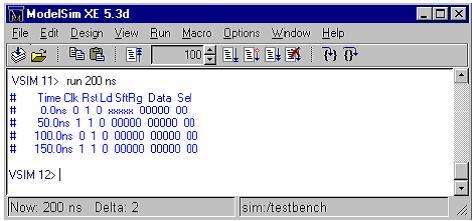

下面是verilog示例,它將在終端屏幕上顯示一些值。

// pipes the ASCII results to the terminal or text editor

initial begin

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

關鍵字 $display在終端屏幕上輸出引用的附加的說明文字(“。。。”).關鍵字$monitor操作不同。因為它的輸出是事件驅動的。例中的變數$realtime(由用戶賦值到當前的模擬時間)用於觸發信號列表中值的顯示。信號表由變數 $realtime開始,跟隨其他將要顯示的信號名(clock, reset, load等)。以%開始的關鍵字包含一個格式描述的表,用來控制如何格式化顯示信號列表中的每個信號的值。格式列表是位置確定的。每個格式說明有序地與信號列表中的信號順序相關。比如%t說明規定了$realtime的值是時間格式。並且第一個%b說明符格式化clock的值是二進位形式。verilog提供附加的格式說明,比如%h用於說明十六進位,%d說明十進位,%c說明顯示為八進位。(參見verilog準則了解完整的關鍵字及格式描述符)

簡單的測試設計實例化用戶設計,然後提供相應的激勵。測試輸出被圖形化顯示在模擬器的波形窗口裡或者作為文本發送到用戶的終端或者是管道輸出文本。

以下是一個簡單的用Verilog實現的設計,它實現了一個移位寄存器的功能。

module shift_reg (clock, reset, load, sel, data, shiftreg);

input clock;

input reset;

input load;

input [1:0] sel;

input [4:0] data;

output [4:0] shiftreg;

reg [4:0] shiftreg;

always @ (posedge clock)

begin

if (reset)

shiftreg = 0;

else if (load)

shiftreg = data;

else

case (sel)

2’b00 : shiftreg = shiftreg;

2’b01 : shiftreg = shiftreg << 1;

2’b10 : shiftreg = shiftreg >> 1;

default : shiftreg = shiftreg;

endcase

end

endmodule

以下是簡單的測試設計示例移位寄存器設計的例子,verilog描述。

module testbench; // declare testbench name

reg clock;

reg load;

reg reset; // declaration of signals

wire [4:0] shiftreg;

reg [4:0] data;

reg [1:0] sel;

// instantiation of the shift_reg design below

shift_reg dut(.clock (clock),

.load (load),

.reset (reset),

.shiftreg (shiftreg),

.data (data),

.sel (sel));

//this process block sets up the free running clock

initial begin

clock = 0;

forever #50 clock = ~clock;

end

initial begin// this process block specifies the stimulus.

reset = 1;

data = 5’b00000;

load = 0;

sel = 2’b00;

#200

reset = 0;

load = 1;

#200

data = 5’b00001;

#100

sel = 2’b01;

load = 0;

#200

sel = 2’b10;

#1000 $stop;

end

initial begin// this process block pipes the ASCII results to the

//terminal or text editor

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

endmodule

以上的測試設計實例化設計,設置時鐘,提供激勵信號。所有的進程塊在模擬時間零點開始。英鎊標記(#)說明下一個激勵作用前的延遲。$stop命令使模擬器停止測試模擬(所有測試設計中都應該包含一個停止命令)。最後,$monitor語句返回ascII格式的結果到屏幕或者管道輸出到一個文本編輯器。接后的是一個vhdl描述的的測試設計,它實例化設計並提供激勵到上述用verilog描述的移位寄存器.

[admin via 研發互助社區 ] 編寫高效的測試設計(testbenches)已經有9471次圍觀

http://cocdig.com/docs/show-post-43470.html