近年來,隨著集成電路技術的發展,用傳統的方法進行晶元或系統設計已不能滿足要求,迫切需要提高設計效率。在這樣的技術背景下,能大大降低設計難度的VHDL設計方法正越來越廣泛地被採用。但是VHDL設計是行為級的設計???帶來的問題是設計者的設計思考與電路結構相脫節。設計者主要是根據VHDL的語法規則??對系統目標的邏?行為進行描述??然後通?綜合工具進行電路結構的綜合、編譯、優化,通過模擬工具進行邏輯功能模擬和系統時延的模擬。實際設計過程中,由於每個工程師對語言規則、對電路行為的理解程度不同,每個人的編程風格不同,往往同樣的系統功能,描述的方式是不一樣的,綜合出來的電路結構更是大相徑庭。因此,即使最後綜合出的電路都能實現相同的邏輯功能,其電路的複雜程度和時延特性都會有很大的差別,甚至某些臃腫的電路還會產生難以預料的問題。從這個問題出發,我們就很有必要深入討論在VHDL設計中如何簡化電路結構,優化電路設計的問題。

1 描述方法對電路結構的影響

用VHDL進行設計,其最終綜合出的電路的複雜程度除取決於設計要求實現的功能的難度外,還受設計工程師對電路的描述方法和對設計的規劃水平的影響。最常見的使電路複雜化的原因之一是設計中存在許多本不必要的類似LATCH的結構。而且由於這些結構通常都由大量的觸發器組成,不僅使電路更複雜,工作速度降低,而且由於時序配合的原因而導致不可預料的結果。例如對於同一解碼電路有不同VHDL描述:

1: IF INDEX=″00000″ THEN

STEPSIZE<=″0000111″;??

WLSIF INDEX=″00001″ THEN

STEPSIZE<=″0001000″;??

LSIF INDEX=″00010″ THEN

STEPSIZE<=″0001001″;??

……

ELSE

STEPSIZE<=″0000000″;??

END IF;

2:STEPSIZE<=″0000111″ WHEN INDEX=″00000″ ELSE

″0001000″ WHEN INDEX=″00001″ELSE

″0001001″WHEN INDEX=″00010″ ELSE

……

″0000000″;??

以上兩段程序描述了同一個解碼電路。第二段程序由於WHEN......ELSE的語句不能生成鎖存器的結構且ELSE后一定要有結果,所以不會有問題,而第一個程序如果不加ELSE STEPSIZE〈=“0000000”這句,則會生成一個含有7位寄存器的結構,雖然都能實現相同的解碼功能。但是電路複雜度會大增。而由於每個工程師的寫作習慣不同,有的喜歡用IF....ELSE的語句,有的喜歡用WHEN....ELSE的方式,而用IF....ELSE時,如稍不注意,在描述不需要寄存器的電路時沒加ELSE,則會引起電路不必要的開銷。所以在VHDL設計中要慎用IF....ELSE這類能描述自身值代入的語句。

2 設計規劃的優劣直接影響電路結構

另一主要引起電路複雜化的原因是對設計規劃的不合理。雖然VHDL語言能從行為描述生成電路,但一個完整的設計一般來說都不可能由直接描述設計的目標功能來實現的。總要把設計分成若干部分,每一部分再分別描述其行為。這就涉及到如何劃分功能模塊的問題,要求對設計了解的較深入,才能使劃分更有效,才能降低電路的複雜程度。例如我們設計一個時鐘源為1kHz,每32秒發出一組信號(共八組)的簡單的控制器來說。下面有兩種實現方法:

(1)用15位的記數器實現把輸入1kHz的時鐘分頻為1/32Hz,然後用這個作為時鐘驅動一個3位的記數器,這個記數器的八個狀態分別通過一個3-8解碼器發出所要求的信號。

??2 直接?18位的記數器把輸入的1kHz時鐘進行分頻,再利用記數器的八個相距32秒的狀態來推動一個12-8解碼器來實現。

對於如此的設計要求,VHDL程序分別如下所示:

1. 第一種設計方法的VHDL源程序

process(clk,cclk,count2)

begin

if??(clk='1' and clk'event)then

count2<=count2 + 1;??

if(count2=″000000000000000″)then

cclk<='1';??

else

cclk<='0';??

end if;??

end if;??

end process;??

process(cclk,count3,ctemp)

begin

if(cclk='1' and cclk'event)then

count3<=count3 +1;??

if(count3=″000″)then

ctemp<=″00000001″;??

elsif(count3=″001″)then

ctemp<=″00000010″;??

elsif(count3=″010″)then

ctemp<=″00000100″;??

elsif(count3=″011″)then

ctemp<=″00001000″;??

elsif(count3=″100″)then

ctemp<=″00010000″;??

elsif(count3=″101″)then

ctemp<=″00100000″;??

elsif(count3=″110″)then

ctemp<=″01000000″;??

elsif(count3=″111″)then

ctemp<=″10000000″;??

else

ctemp<=″00000000″;??

end if;??

end if;??

end process;??

2. 第二種設計方法的VHDL源程序

process(clk,ctemp,count)

begin

if(clk='1' and clk'event)then

count<=count + 1;??

if(count=″00000000000000000″)then

ctemp<=″00000001″;??

elsif(count=″001000000000000000″)then

ctemp<=″00000010″;??

elsif(count=″010000000000000000″)then

ctemp<=″00000100″;??

elsif(count=″011000000000000000″)then

ctemp<=″00001000″;??

elsif(count=″100000000000000000″)then

ctemp<=″00010000″;??

elsif(count=″101000000000000000″)then

ctemp<=″00100000″;??

elsif(count=″110000000000000000″)then

ctemp<=″01000000″;??

elsif(count=″111000000000000000″)then

ctemp<=″10000000″;??

end if;??

end if;??

end peocess;??

對於第一種的程序可以綜合出的電路如圖1所示。

該電路用一個15位的加法器和寄存器組成一個15位的記數器。在記數器記完一周回到“000000000000000”時,通過後面的15輸入的與非門和一位的觸發器就可以實現同步的進行215次分頻,同步輸出32Hz的時鐘CCLK。CCLK再驅動一8位的移位寄存器,便可實現每32秒輸出一信號。

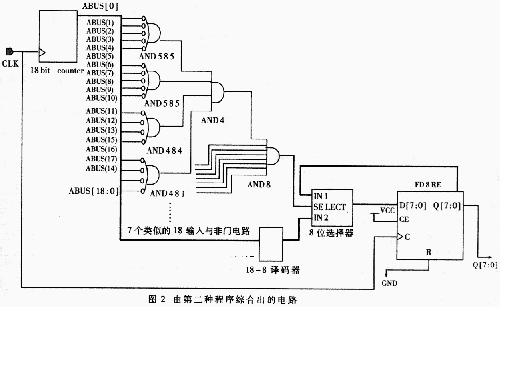

而用第二種的程序設計綜合出的電路如圖2所示。

圖片如下:

圖2所示的電路用一個18位的加法器和寄存器組成一個18位的記數器。後接了8個18輸入的邏輯門和8輸入的或門。輸入的1kHz時鐘經過記數器被分頻,其中有八個相隔32Hz的記數狀態,邏輯門就負責把這八狀態解碼成所需的八組信號。解碼后的數據通過選擇器輸出到8位的觸發器,以實現同步輸出。還有個鎖存器,是用來保持輸出信號不變,在八個狀態中的從一個狀態變到下一個之前,保持前一個的數值。選擇器當邏輯門輸出新的數據時讓其輸出數據通過,在新數據到來之前輸出鎖存器的數據。

以上兩種方法都能實現相同的邏輯功能,但圖2所示的方法由於運用了較少位數的記數器,所用的邏輯門也較簡單,而且還少用了多路選擇器和鎖存器資源,所以綜合出來的電路較簡單,以XILINX Spartan S05 -3 晶元為例。第一種方法佔用晶元CLB的12%,其中FMAPS為9%,最高工作速度為82Hz。而第二種方法佔用了15%的CLB,FMAPS佔用 15%,最高工作速度只有69.9MHz。在這一個簡單的設計之中就能省20%的電路,提高12.1MHz的工作速度,由此可見科學的劃分設計對降低電路複雜程度的重要意義。

3 邏輯設計對電路結構的影響

還有一個使電路複雜化的原因是邏輯電路的輸入項太多以致需佔用過多的面積。我們從圖3和圖4兩個相同功能的邏輯電路和他們對應的VHDL描述來分析。

比較兩圖可知,圖3是二級邏輯門,每個輸入信號與不只一個邏輯門相連,圖4是三級的邏輯門,每個輸入信號只與一邏輯門相連。由於級數少,延時也較少,因此圖3的速度要比圖4快。然而,由於圖3的輸入項要比圖4大的多(10:5),因此,佔用的面積必然也比圖3大。圖4是圖3通過提取公因數(例中是B和C)得來的,這是

把附加的中間項加到結構描述中去的一種過程,它使輸入到輸出中的邏輯級數增加,犧牲速度換來電路佔用面積的減少。對於對延時要求不高的情況下採用這種方法分解邏輯電路以達到減少電路複雜度的目的。

通過以上簡單、初步的探討,我們可以知道,用VHDL進行集成電路的設計,牽涉到對VHDL語言的使用方法和對設計的理解程度。本文討論了以下幾個簡化和優化電路設計的3個值得注意的方面:

[admin via 研發互助社區 ] VHDL設計中的電路簡化問題已經有14560次圍觀

http://cocdig.com/docs/show-post-43512.html