前言

在製程進入深次微米世代之後,晶片(IC)設計的高複雜度及系統單晶片(SOC)設計方式興起。此一趨勢使得如何確保IC品質成為今日所有設計從業人員不得不面臨之重大課題。靜態時序分析(Static Timing Analysis簡稱STA)經由完整的分析方式判斷IC是否能夠在使用者的時序環境下正常工作,對確保IC品質之課題,提供一個不錯的解決方案。然而,對於許多IC設計者而言,STA是個既熟悉卻又陌生的名詞。本文將力求以簡單敘述及圖例說明的方式,對STA的基礎概念及其在IC設計流程中的應用做詳盡的介紹。

什麼是STA?

STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設計者給定的時序限制(Timing Constraint)。以分析的方式區分,可分為Path-Based及Block-Based兩種。

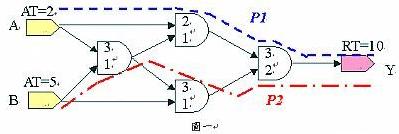

先來看看Path-Based這種分析方式。如圖一所示,訊號從A點及B點輸入,經由4個邏輯閘組成的電路到達輸出Y 點。套用的Timing Model標示在各邏輯閘上,對於所有輸入端到輸出端都可以找到相對應的延遲時間。而使用者給定的Timing Constraint為:

現在我們針對P1及P2兩條路徑(Path)來做分析。P1的起始點為A,訊號到達時間點為2。經過第1個邏輯閘之後,由於此閘有2單位的延遲時間,所以訊號到達此閘輸出的時間點為4(2+2)。依此類推,訊號經由P1到達輸出Y的時間點為7(2+2+3)。在和上述第三項Timing Constraint比對之後,我們可以得知對P1這個路徑而言,時序(Timing)是滿足使用者要求的。

按照同樣的方式可以得到訊號經由路徑B到達輸出Y的時間點為11(5+1+3+2),照樣和上述第三項Timing Constraint比對,我們可以得知對P2這個路徑而言,Timing是不滿足使用者要求的。

對圖一的設計而言,總共有6個訊號路徑。對於採用Path-Based分析方式的STA軟體來說,它會對這6個訊號路徑作逐一的分析,然後記錄下結果。IC設計者藉由檢視其分析報告的方式來判斷所設計的電路是否符合給定的Timing Constraint。由於最常用來做靜態時序分析驗證核可(STA Signoff)的EDA軟體PrimeTime?採用Path-Based的分析方式,所以本文將以Path-Based的分析方式介紹為主。

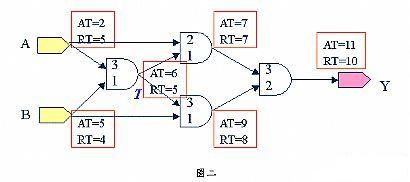

再來看看Block-Based的分析方式。此時時序資訊(Timing Information)的儲存不再是以路徑為單位,而是以電路節點(Node)為單位。由Timing Constraint我們僅能得知A節點的AT為2,B節點的AT為5以及Y節點的RT為10。Block-Based的分析方式會找出每個節點的AT和 RT,然後比對這兩個數值。當RT的值大於AT時表示訊號比Timing Constrain中要求的時間還早到達,如此則Timing是滿足的,反之則不滿足。

STA資料準備

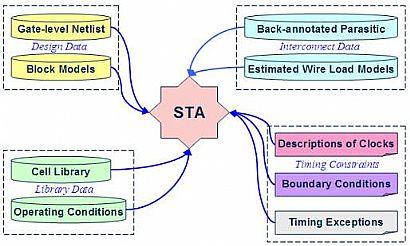

在做STA之前,我們必須對其準備工作有充分的了解。STA所需的資料如圖三所示,以下我們分項說明。其中Design Data部分,由於Block Model和STA軟體相關性太高,我們不在此加以說明,請直接參閱您STA軟體的使用手冊。

圖 三

Library Data:

STA所需要的Timing Model就存放在標準元件庫(Cell Library)中。這些必要的時序資訊是以Timing Arc的方式呈現在標準元件庫中。Timing Arc定義邏輯閘任兩個端點之間的時序關係,其種類有Combinational Timing Arc、Setup Timing Arc、Hold Timing Arc、Edge Timing Arc、Preset and Clear Timing Arc、Recovery Timing Arc、Removal Timing Arc、Three State Enable & Disable Timing Arc、Width Timing Arc。其中第1、4、5、8項定義時序延遲,其他各項則是定義時序檢查。

圖 四

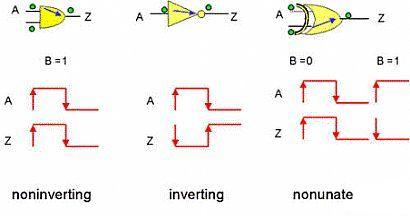

Combinational Timing Arc是最基本的Timing Arc。Timing Arc如果不特別宣告的話,就是屬於此類。如圖四所示,他定義了從特定輸入到特定輸出(A到Z)的延遲時間。Combinational Timing Arc的Sense有三種,分別是inverting(或 negative unate),non-inverting(或 positive unate)以及non-unate。當Timing Arc相關之特定輸出(圖四Z)訊號變化方向和特定輸入(圖四A)訊號變化方向相反(如輸入由0變1,輸出由1變0),則此Timing Arc為inverting sense。反之,輸出輸入訊號變化方向一致的話,則此Timing Arc為non-inverting sense。當特定輸出無法由特定輸入單獨決定時,此Timing Arc為non-unate。

圖 五

圖 六

圖 七

圖 八

圖 九

圖 十

圖 十一

圖 十二

其他的Timing Arc說明如下。

上文列出了標準元件庫內時序模型的項目,但對其量化的數據卻沒有加以說明。接下來,我們就來看看到底這些時序資訊的確實數值是如何定義在標準元件庫中的。

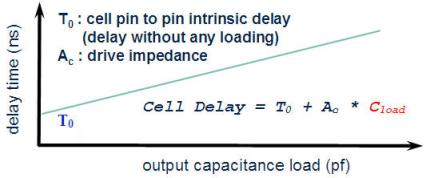

以Combinational Timing Arc為例,訊號從輸入到輸出的延遲時間可以描述成以輸入的轉換時間(Transition Time)和輸出的負載為變數的函數。描述的方式可以是線性的方式,如圖十三所示。也可以將這2個變數當成指標,建立時序表格(Timing Table),讓STA軟體可以查詢出正確的延遲時間。這種以表格描述的方式會比上述線性描述的方式準確許多,因此現今市面上大部分的標準元件庫皆採用產生時序表格的方式來建立Timing Model。

圖 十三

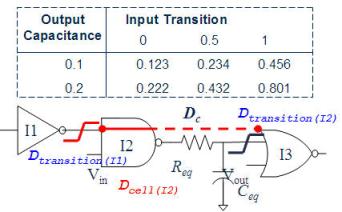

我們舉個簡單的例子來說明STA軟體如何從時序表格計算出元件延遲時間。(圖十四)

圖十四

當輸入的轉換時間為0.5,輸出負載為0.2時,可由圖十四的時序表格查得元件I2的延遲時間為0.432。而由於表格的大小有限,對於無法直接由表格查詢到的延遲時間(如輸入轉換時間0.25,輸出負載0.15),STA軟體會利用線性內插或外插的方式計算延遲時間。

對於其他的Timing Arc,不管是時序延遲或時序檢查,其相對應的時序數值計算和上例的計算方式是一樣的。

接下來我們說明操作環境(Operating Condition)對時序的影響。操作環境指的是製程(Process)、電壓(Voltage)、溫度(Temperature)三項因子。這三項因子通常會被簡稱為PVT,其對時序的影響可用下方線性方程式來描述。其中nom_process、nom_voltage及 nom_temperature會定義在標準元件庫中,代表建立時序表格時的操作環境。

Interconnect Data:

在「什麼是STA」段落的例子中,為了方便說明,我們並沒有把邏輯閘和邏輯閘間的連線延遲(Interconnect Delay)考慮在內。事實上,許多DSM IC設計之時序表現是由連線延遲主導的,其重要性不容我們忽視。

連線延遲依照布局與繞線(P&R)前後有不同的考量。在布局與繞線前,元件在晶片中擺放的位置尚未確定,所以連線延遲是一個預估值。而在布局與繞線之後,連線延遲則是根據實際繞線計算出來的。對布局與繞線之前的連線延遲,通常是用Wireload Model來預估。Wireload Model根據晶片面積的預估大小及連線驅動元件數目(Fan-out)的多寡來決定連線的電阻和電容值,STA軟體則利用這些電阻電容值計算出連線延遲。在布局與繞線之後,可以利用電阻電容萃取(RC Extraction)軟體將繞線圖形轉換成實際的電阻電容電路,然後貼回(Back-annotate)STA軟體計算連線延遲。

Timing Constraints:

Timing Constraint為使用者所給定,用來檢驗設計電路時序的準則。其中最重要的一項就是時脈(Clock)的描述。對於一個同步電路而言,暫存器和暫存器之間的路徑延遲時間必須小於一個Clock周期(Period),也就是說,當我們確認了Clock規格,所有暫存器間的路徑的Timing Constraint就會自動給定了。

圖十五

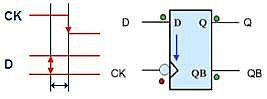

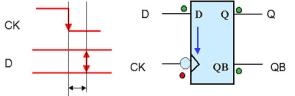

Clock規格包含波形、Latency及Uncertainty的定義。波形定義一個Clock的周期及訊號上升緣及下降緣的時間點。 Latency定義從Clock來源到序向元件Clock輸入端的延遲時間。Uncertainty則定義Clock訊號到序向元件Clock輸入端可能早到或晚到的時間。

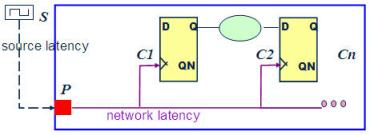

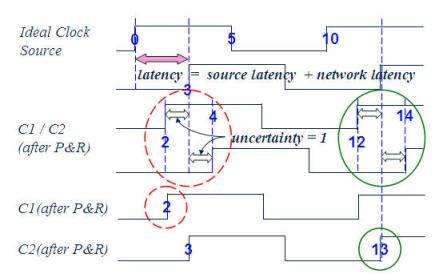

如果上面的文字讓你有不知所云的感覺,那底下看圖說故事的解說也許會讓你有比較清晰的概念。在圖十五的電路中,左邊的正反器(Flip-Flop)在第一個Clock上升緣時會丟出資料,此資料會在第二個Clock上升緣讓右邊的Flip-Flop擷取。要分析右邊的Flip-Flop能否正確擷取資料就必須知道第一個Clock上升緣到達節點C1的時間點和第二個上升緣到達節點C2的時間點。假設在時間點為0的時候,Clock訊號由S點出發,經過一段時間(source latency,1個時間單位,模擬晶片外的Clock延遲時間,例如板子上的繞線產生的訊號延遲時間)到達電路的Clock輸入端點P,接下來再經過一段時間(晶片內Clock繞線造成的訊號延遲時間),Clock訊號分別到達C1和C2節點。如果電路已經進行布局與繞線,輸入端點P到C1和C2的訊號延遲時間可由連線上的寄生電阻電容計算得來。比方說,經過計算髮現訊號由P傳遞到C1需要1個時間單位,由P傳遞到C2需2個時間單位,則Clock訊號第一個上升緣到達C1和第二個上升緣到達C2的時間點就會如圖十六下方兩列所示,分別為時間點2和13(因為加上了1個時間單位的source latency)。

圖十六

在布局與繞線之前,我們無法準確得知P到C1和C2的訊號延遲時間,僅能先做個預估。圖十五的network latency及上文提到的Uncertainty就是用來做此種預估的。先假設我們擁有某種完美的布局與繞線軟體可以讓Clock輸入端點P到所有 Flip-Flop的Clock輸入端的訊號延遲時間一模一樣,那麼我們只要知道這個訊號延遲時間就可以得到Clock訊號到達C1和C2的時間點了。這個訊號延遲時間可以藉由電路特性(如預估面積大小,Flip-Flop數目等)來做預估,而這個預估值就是所謂的network latency。如果這種完美的軟體存在的話,那Clock的上升緣到達C1和C2的時間點就可以由Latency(source latency + network latency)計算出來。

很不幸的,世界上沒有這麼完美的軟體,在布局與繞線后Clock輸入端點P到所有Flip-Flop的Clock輸入端的訊號延遲時間不會完全一樣。也就是說Clock的某個上升緣不會同時到達C1和C2。因此我們要對上述的預估值做些修正,加入Uncertainty的描述來定義Clock上升緣左右移動的可能範圍。在圖十六中,Uncertainty為1個時間單位,所以Clock第一個上升緣會在時間點3(因為 Latency為3)左右1時間單位範圍內(也就是時間點2到時間點4)到達C1,。第二個上升緣則會在時間點12到14的範圍內到達C2。

[admin via 研發互助社區 ] 靜態時序分析(Static Timing Analysis)基礎與應用(上)已經有24512次圍觀

http://cocdig.com/docs/show-post-43262.html