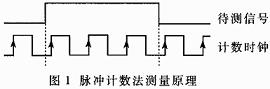

在測量與儀器儀錶領域,經常需要對數字信號的脈衝寬度進行測量。這種測量通常採用脈衝計數法,即在待測信號的高電平或低電平用一高頻時鐘脈衝進行計數,然後根據脈衝的個數計算待測信號寬度,如圖1所示。待測信號相對於計數時鐘通常是獨立的,其上升、下降沿不可能正好落在時鐘的邊沿上,因此該法的最大測量誤差為一個時鐘周期。例如採用80MHz的高頻時鐘,最大誤差為12.5ns。

提高脈衝計數法的精度通常有兩個思路:提高計數時鐘頻率和使用時幅轉換技術。時鐘頻率越高,測量誤差越小,但是頻率越高對晶元的性能要求也越高。例如要求1ns的測量誤差時,時鐘頻率就需要提高到1GHz,此時一般計數器晶元很難正常工作,同時也會帶來電路板的布線、材料選擇、加工等諸多問題。時幅轉換技術雖然對時鐘頻率不要求,但由於採用模擬電路,在待測信號頻率比較高的情況下容易受雜訊干擾,而且當要求連續測量信號的脈寬時,電路反應的快速性方面就存在一定問題。

區別於以上兩種方法,本文提出另一種利用數字移相技術提高脈寬測量精度的思路並使用FPGA晶元實現測試系統。

1 測量原理

所謂移相是指對於兩路同頻信號,以其中一路為參考信號,另一路相對於該參考信號做超前或滯后的移動形成相位差。數字移相通常採用延時方法,以延時的長短來決定兩數字信號間的相位差,本文提出的測量原理正是基於數字移相技術。如圖2所示。

原始計數時鐘信號CLK0通過移相后得到CLK90、CLK180、CLK270,相位依次相差90°,用這四路時鐘信號同時驅動四個相同的計數器對待測信號進行計數。設時鐘頻率為f,周期為T,四個計數器的計數個數分別為m1、m2、m3和m4,則最後脈寬測量值為:

w=[(m1+m2+m3+m4)/4]×T (1)

可以看到,這種方法實際等效於將原始計數時鐘四倍頻,以4f的時鐘頻率對待測信號進行計數測量,從而將測量精度提高到原來的4倍。例如原始計數時鐘為80MHz時,系統的等效計數頻率則為320MHz,如果不考慮各路計數時鐘間的相對延遲時間誤差,其測量的最大誤差將降為原來的四分之一,僅為3.125ns。同時,該法保證了整個電路的最大工作頻率仍為f,避免了時鐘頻率提高帶來的一系列問題。

2 系統實現

系統實現的最關鍵部分是保證送入各計數器的時鐘相對延遲精度,即要保證計數時鐘之間的相位差。由於通常原始時鐘頻率已經相對較高(通常接近100MHz),周期在10~20ns之間,因此對時鐘的延遲時間只有幾ns,使用普通的延遲線晶元無法達到精度要求;同時為了避免電路板內晶元間傳送延遲的影響,保證測試系統的精度、穩定性和柔性。本文採用現場可編程門陣列(FPGA)來實現所提出的測量方法。系統結構如圖3所示。

晶振產生原始輸入時鐘,通過移相計數模塊后得到脈寬的測量值,測量結果送入FIFO緩存中,以加快數據處理速度,最後通過PCI匯流排完成與計算機的數據傳輸。邏輯控制用來協調各模塊間的時序,保證系統的正常運行。為提高測試系統的靈活性和方便性,系統建立了內部寄存器,通過軟體修改寄存器的值可以控制測試系統的啟動停止,選擇測量高電平或低電平等。移相計數模塊、FIFO緩衝以及邏輯控制均在FPGA晶元內實現,晶元使用XILINX公司的SpartanII系列。

SpartanII系列是一款高性能、低價位的FPGA晶元,其最高運行頻率為200MHz,這裡選用其中的XC2S15-6(-6為速度等級)。晶元提供了四個高精度片內數字延遲鎖定環路(Delay-Locked Loop,即DLL),可以保證晶元內時鐘信號的零傳送延遲和低的時鐘歪斜(Clock Skew);同時可以方便地實現對時鐘信號的常用控制,如移相、倍頻、分頻等。在HDL程序設計中,可以使用符號CLKDLL調用片內DLL結構,其管腳圖如圖4所示。

主要管腳說明如下:

- CLKIN:時鐘源輸入,其頻率範圍為25~100MHz。

- CLKFB:反饋或參考時鐘信號,只能從CLK0或CLK2X反饋輸入。

- CLK [0|90|180|270] 時鐘輸出,與輸入時鐘同頻,但相位依次相差90°。其內部定義了屬性DUTY_CYCLE_CORRECTION,可以用來調整時鐘的占空比,值為FALSE時,輸出時鐘占空比和輸入時鐘一致,值為TRUE時將佔空比調整為50%。

- CLK2X:時鐘源倍頻輸出,且占空比自動調整為50%。

- CLKDV:時鐘源分頻輸出,由屬性 CLKDV_DIVIDE控制N分頻,N可以為1.5、2、2.5、3、4、5、8或16。

- LOCKED:該信號為低電平時,表示延遲鎖相環DLL還沒有鎖定信號,上述輸出時鐘信號未達到理想信號;當變為高電平時,表示鎖相環已經完成信號鎖定,輸出時鐘信號可用。若時鐘源輸入頻率大於60MHz,則系統鎖定時間大約需20μs。

利用DLL功能可以非常快速方便地構建移相計數模塊,實現本文前面介紹的測量方法。

原始時鐘通過CLKDLL處理后得到的相位依次相差90°的四路時鐘輸出為CLK0、CLK90、CLK180和CLK270,它們分別作為四個相同的16位計數器的計數時鐘,待測信號連接計數器的使能端,同時控制四個計數器的啟動和停止。有了各計數器的計數結果,再通過加法器得到累加的計數個數,最後計算出信號脈寬值。

3 模擬和精度分析

圖6給出了FPGA晶元內部布線後用Modelsim進行模擬的結果。在RESET后就啟動移相計數模塊,開始對待測信號進行測量,完成一次測量后產生READY信號,同時輸出測量結果,以供後續部分使用。模擬的結果證明測試系統達到設計目標。

下面進一步對系統做深入的誤差分析。造成系統測量脈寬誤差的來源主要有系統原理誤差TS、時鐘相移誤差TP和信號延遲誤差Td以及計數時鐘抖晃TC,如圖7所示。

由前所述,當80MHz晶振時鐘輸入時,系統原理誤差TS=3.125ns。時鐘相移誤差為從CLKDLL中出來的四路時鐘信號之間本身的相位偏移,根據晶元提供的參數,其最大TP為200ps。計數時鐘抖晃是指從CLKDLL中輸出的時鐘信號本身周期的偏差,其最大TC為60ps。由於計數的時鐘周期數較多,故平均后其對整個系統的測量誤差影響可以忽略不計。

信號延遲誤差即為由於晶元內部各信號傳輸延遲不一致而造成的四個計數器計數的同步誤差。為分析該誤差情況,用ISE 5.1提供的Timing Analyzer程序對關鍵路徑做進一步的時間分析。

表中第一欄為從CLKDLL中出來的計數時鐘到各自計數器的延遲時間,第二欄為用來控制計數器啟動停止的HF信號到四個計數器的時間。由於需要的是各計數時鐘間相對延遲時間,故第三欄給出時鐘相對於HF信號到計數器的延遲,即為第一欄和第二欄的差值。由此得出信號延遲誤差Td=0.950ns。

故有系統測量誤差Γ為:

Γ=TS+TP+Td=4.275ns (2)

即脈寬測量最大誤差為±4.275ns。與脈衝計數法比較,同樣的80MHz時鐘輸入,最大測量誤差減小到原來的34.2%。

本文在數字移相技術的基礎上設計了一種高精度的脈寬測量系統,使測量精度相對於脈衝計數法提高了多倍。若需進一步提高這種方法的測量精度,可以通過以下兩個方面進行改進:

(1)繼續提高晶振頻率,尋求速度更快的FPGA晶元。晶振頻率越高,系統原理誤差越小。

(2)減小信號延遲誤差。

由前面可以看到,信號的延遲誤差對系統精度的影響佔了很大的比例。減小各計數時鐘和待測信號到計數器的信號延遲的差異,可以有效地提高測量精度。由於FPGA內部信號延遲的時間均可以很方便地得到,因此在設計時可以通過調整內部各元件的放置位置以及連線來盡量減小延遲誤差,或者通過添加一些門電路來增加延時以使各信號延遲時間儘可能相同。