隨著信息技術的飛速發展,特別是在二十世紀90年代以後,美國在南斯拉夫戰爭和兩次海灣戰爭中成功地運用了電子戰、信息戰,以及近年來我國在航天航空事業方面的高速發展,使我國開始重視和發展信息技術。與此同時對高速、大容量、高可靠性的靜態存儲器的需求越來越多,對軍用的數據存儲器的設計也提出了更高的要求。目前軍用計算機傳輸數據的最快方式——DMA方式的傳輸速率最大也只是在5Mbps以下。對於幾十Mbps的超高速採樣速率,往往是上一次數據還沒有被計算機讀取,下一次的採集過程就結束了。因此採用傳統的計算機傳輸處理數據的方法,顯然會造成數據的丟失與混亂。所以對於快速採集,慢速處理的系統必然要用到緩存。本文就是針對數據存儲器FIFO解決亞穩態問題的設計,經過對不同方法的比較,設計了一種新型的邏輯標誌的同步電路。

1亞穩態問題的解決方案

1.1問題的產生

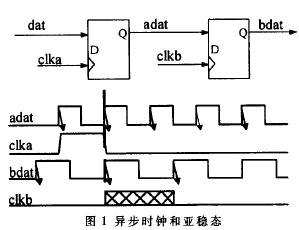

在數字集成電路中,觸發器要滿足setup/hold的時間要求。當一個信號被寄存器鎖存時,如果信號和時鐘之間不滿足這個要求,Q端的值是不確定的,並且在未知的時刻會固定到高電平或低電平,這個過程稱為亞穩態,如圖1所示。圖中clka和clkb即為非同步時鐘,亞穩態必定會發生在非同步時鐘電路中。在圖1的非同步電路中,電路外部的輸入和內部的時鐘之間是毫無時間關係的,因此setup/hold衝突是必然的;同在電路內部的兩個沒有關係的時鐘域之間的信號傳遞,也必然會導致setup/hold衝突。亞穩態雖然是不可避免的,但採用下面幾種設計方法可以將其發生的概率降低到一個可以接受的程度。

1.2 常見的解決方法

1.2.1格雷碼編碼法

寫地址/讀地址採用格雷碼。由實踐可知,同步多個非同步輸入信號出現亞穩態的概率遠遠大於同步一個非同步信號的概率。對於多個觸發器的輸出所組成的寫地址/讀地址可以採用格雷碼。由於格雷碼每次只變化一位,因此採用格雷碼可以很好地節約功耗,有效地減少亞穩態的產生,特別是在地址位比較多的情況下可以更好地解決亞穩態的問題。

格雷碼是對二進位地址輸出進行轉換,下面是四位代碼之間轉換的邏輯表達式:

B碼轉G碼的邏輯表達式:G碼轉B碼的邏輯表達式:

B4=G4 G4=B4

B3=B4⊕G3 G3=B4⊕B3

B2=B3⊕G2 G2=B3⊕B2

B1=B2⊕G1 G1=B2⊕B1

但採用格雷碼編碼法需要在地址位的每一位增加一級的異或門,這樣在計數比較前增大了延時和版圖面積。同時在地址分配到其他邏輯單元前要把格雷碼轉換成二進位代碼,這同樣也會增大版圖設計面積和延時。

1.2.2 雙觸發器法

採用觸發器來同步非同步輸入信號,如圖2中的兩級觸發器可以將出現亞穩態的概率降低到一個很小的程度。由於增加了一級觸發器,這樣在最後的輸出就延遲了一個時鐘,使前一個時鐘產生的數據被b_clk連續鎖存兩次。雖然第一次鎖存產生亞穩態,但經過一段時間的延時可以有效地解決這個問題。這種方法同時帶來了對輸入信號的一級延時,需要在設計時鐘的時候加以注意。

雖然兩級觸發器能有效地抑制亞穩態,但增加了一級的D觸發器,這和格雷碼編碼法一樣會增加版圖面積。這種方法在clka與clkb的採樣周期相差不大的情況下比較適合。

1.2.3 結繩法

如圖3所示,如果aclk的頻率比bclk頻率高,將可能會出現因為adat變化太快而使balk無法採到的問題,即在信號從快時鐘域向慢時鐘域過渡時,如果信號變化太快,慢時鐘將可能無法對該信號進行正確採樣,即採樣失敗。所以在使用雙鎖存器法時,應該使原始信號保持足夠長的時間,以便另一個時鐘域的鎖存器對其進行正確的採樣。

對上述問題,一般採用“結繩法”的設計方法,將慢時鐘周期信號通過分頻的方式將其周期增長,經過雙鎖存採樣以後再使其恢復原來的時鐘周期。即用“結繩”將信號延長,用“同步”實現雙latch採樣,用“解繩”還原為原來的時鐘,保證另一個時鐘域也可以正確採樣,而接收方用相反的流程送迴響應信號。

“結繩法” 可以解決快時鐘域向慢時鐘域過渡的問題,適用的範圍也很廣。但是“結繩法”實現較為複雜,特別是其頻率不高,所以在對設計性能要求較高的場合應該慎用。

2 基於非同步比較FIFO 邏輯標誌的產生

2.1 設計思想

非同步FIFO可以很好地解決時鐘速度相差懸殊的時鐘間的數據傳輸問題。非同步FIFO存儲器在結構上可劃分為存儲陣列和外圍電路兩大部分,它由幾個主要模塊組成:存儲單元RAM、寫控制邏輯、讀控制邏輯、標誌邏輯、擴展邏輯、複位邏輯以及並/串轉換邏輯。這裡主要考慮產生空、滿標誌的同步。

標誌邏輯是用以產生反映器件內部RAM 陣列佔用情況的狀態標誌信號,使系統可以及時採取措施以免數據溢出。在FIFO中標誌位的產生是關鍵的一步,如果能夠及時判斷出每一個時鐘下寫入和讀出的位置,就可以防止產生誤操作,做到寫滿不再寫、讀空則停止讀。在非同步FIFO中的標誌位主要包括空標誌、滿標誌、半滿標誌和將近滿、將近空標誌。非同步FIFO邏輯框圖如圖4所示。

2.2 標誌位的產生

2.2.1空、滿標誌位的產生標誌邏輯

滿標誌是為了防止FIFO在滿狀態時被寫,空標誌是為了防止FIFO在空狀態時被讀。對於非同步FIFO 而言,數據是由某一個時鐘域的控制信號寫入FIFO,而由另一個時鐘域的控制信號將數據讀出FIFO。也就是說,讀寫指針的變化動作是由不同的時鐘產生的。因此,對FIFO空或滿的判斷是跨時鐘域的。如何根據非同步的指針信號對FIFO的滿狀態或空狀態進行正確的判斷是研究的重點之一。

當讀指針和寫指針相等也就是指向同一個內存位置時,FIFO可能處於滿或空兩種狀態。可以通過不同的方法判斷或區分FIFO究竟是處於滿狀態還是空狀態,也就是說究竟是寫指針從后趕上了讀指針,還是讀指針從后趕上了寫指針。本文採用設置一個額外的狀態位的方法,即指針由它的地址位以及狀態位組成。地址位隨著相應的操作遞增,指針由內存的最後位置返回到初始位置時,狀態位取反。因此,當讀寫指針的地址位和狀態位全部吻合的時候,讀寫指針經歷了相同次數的循環移動,也就是說,FIFO處於空狀態;如果讀寫指針的地址位相同而狀態位相反,寫指針比讀指針多循環一次,標誌FIFO處於滿狀態。

2.2.2非同步比較FIFO邏輯標誌與時鐘的同步

一般的非同步FIFO是先將讀地址與寫地址同步以後(以上提到的方法)再進行比較,這種方法一般效率不高,不能很好地節省製版面積。本文採用一種非同步比較法。能夠有效地解決這一問題。目前IDT公司的系列產品一般都採用這種非同步比較法。

在非同步FIFO中,由FIFO讀時鐘產生讀地址rptr,寫時鐘產生寫地址wptr。當rptr與wptr進行非同步比較時,由於rptr的變化(assert)產生aempty_n(FIFO空標誌),即aempty_n的下降沿是與rptr同屬於一個時鐘域的;同理,由於wptr的變化(assert)使aempty_n無效(de-assert),即aempty_n的上升沿是與wptr同屬於一個時鐘域的。非同步比較的時鐘域如圖5所示。

因此可以利用上述的理論基礎來實現從aempty_n到empty的過渡。其中,empty是屬於rclk時鐘域的。由於aempty_n的下降沿是屬於rclk時鐘域的,所以可以用它來作為empty的複位信號;而aempty_n的上升沿是屬於welk時鐘域的,因此可以用雙鎖存器法將其過渡到relk時鐘域,最後得到的empty信號就屬於rclk時鐘域。同理可以得到full信號。控制信號同步如圖6所示。

如圖6所示,非同步比較法的關鍵是用非同步比較的結果—— 信號的下降沿作為最終比較結果的複位信號,而其上升沿則用傳統的雙鎖存器法進行同步,最終得到的信號的上升沿與下降沿都是屬於同一個時鐘域。同時增加的兩級鎖存器也增加了一個時鐘周期的延時輸出,這樣在滿有效狀態下,同時來自讀寫時鐘的讀寫指令存在潛在的亞穩態問題就可以避免。在與傳統的先將地址信號同步然後進行同步比較的方法相比,非同步比較法簡單、高效、節省版圖面積,而且實現起來更簡單。

2.2.3 半滿、將近滿、將近空的產生

半滿、將近滿和將近空是對FIFO晶元容量的一種提前判斷。半滿標誌是一個雙用輸出埠,在單片模式下,當擴展輸入端接地時,這個埠就作為半滿標誌。在字擴展模式下,該埠為擴展輸出端。

以2K字容量的FIFO為例來說明非同步FIFO的半滿與將近滿。如圖7所示:半滿是指當寫指針的位置與讀指針的位置相比較,如果w_point和r_point距離超過總容量的一半,那麼輸出半滿為有效輸出。當2K字的FIFO半滿有效時,標誌w_point地址減去r_point地址的範圍在1K~2K字之間。在具體電路實現上,2K字的FIFO計數器的輸出共有12個地址線,其中第12根是為了判斷滿和空標誌用的。所以判斷半滿主要是對第11根地址的讀和寫計數輸出相同情況和不同情況下進行判斷。

將近空和將近滿一般是讀和寫總容量相差在0~1/8和7/8~1之間,也有的設計是相差在幾個比特範圍之內。這個電路一般用的是比較器判斷。在2K字的FIFO中一般把后高4位放在一起,先判斷正在讀的高4位和寫的高4位的大小關係,再對應判斷其他低位的大小關係,看是否符合設計要求。當高4位寫地址減去讀地址小於1、其低位讀地址大於寫地址時,產生將近空。同樣,將近滿也是先判斷:若高4位寫地址減去讀地址大於15、低位讀地址大於寫地址時,將近滿輸出有效。圖7為設計2K字的FIFO將近空和半滿標誌位在Candenee軟體下的模擬結果圖。

對於標誌信號都是採用非同步比較輸出下降沿作為最終比較結果的複位信號,而其上升沿則採用傳統的雙鎖存器法進行同步的方法。此外,在FIFO 的設計中還要考慮寫入和讀出的位寬是否相等,在不相等的情況下要設計輸入輸出的自動匹配,使輸出位寬等於輸入位寬。同時為FIFO 的深度擴展和寬度擴展設計擴展邏輯,以適應多位寬和大容量的要求。

一般的非同步FIFO通常所採用的是先將讀、寫地址同步后比較的方法,而本文提出的非同步比較以後利用觸發器同步的方法相對前者可以減少延時,從而使系統有更充裕的時間去進行讀、寫操作,有利於提高時鐘頻率,減少邏輯器件個數,從根本上節約了版圖面積。因此在以面積決定成本的今天,對FIFO標誌位的產生採用非同步比較法具有極其重要的現實意義。

[admin via 研發互助社區 ] 非同步時鐘亞穩態及FIFO 標誌位的產生已經有4946次圍觀

http://cocdig.com/docs/show-post-43108.html