SOPC (片上可編程系統)是Altera公司提出的一種靈活、高效的SOC解決方案,能將處理器、存儲器、I/O 口等系統設計需要的功能模塊集成到一個PLD器件上,構建一個可編程的片上系統。本文介紹的面陣CCD採集系統,利用Altera的SOPC Builder定製的NIOS II軟核處理器及與採集相關功能的“軟” 硬體模塊來實現信號的採集。它與目前具有同樣功能的CCD採集系統相比,具有靈活、穩定、易升級、易維護等優點。本系統的實驗在現有的數碼相機平台上進行。

1 系統設計

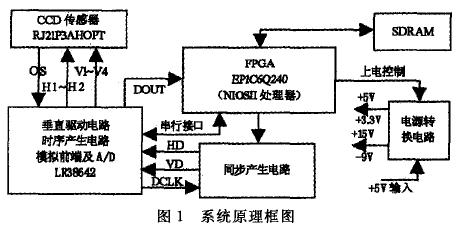

系統原理框圖如圖1所示。目標物經光學鏡頭成像於在RJ21P3AH0PT的光敏面上,產生電荷包強度分佈的圖像,RJ21P3AH0PT為隔列轉移面陣CCD,在四相垂直驅動脈衝和兩相水平驅動脈衝來驅動下,通過CCD內部將光信號轉化為電信號。當LR38642的時序發生器對其施加特定時序脈衝時,每個像素的電荷信號將被依次移出CCD,並經放大變成電壓幅度不等的模擬視頻信號OS。OS視頻信號送到LR38642的模擬前端電路並轉換為數字信號,在NIOS II處理器的控制下通過自定製的CCD採集控制介面以及NIOS II處理器的Avalon匯流排,將圖像數據高速地存儲到外部存儲器SDRAM中。

2 系統硬體及功能模塊

2.1 CCD晶元及專用控制晶元LR38642

本系統面陣CCD採用夏普公司的RJ21P3AH0PT 圖像感測器,如圖2所示,它為1/1.8英寸,330萬象素(2096*1560),有效象素為321萬(2080*1544)。它具有高感廣度,暗電流非常小,要求的水平驅動脈衝頻率為18MHz,需要4相垂直驅動脈衝和兩相水平驅動脈衝來驅動。對其驅動控制選用專用集成控制晶元LR38642,它集成了時序發生器(LR38617)、垂直驅動器電路(LR36685)以及模擬前端模塊(IR3Y48A1)等功能,如圖3所示。

2.2 NIOS II處理器

本系統中FPGA選用Altera Cyclone EP1C6Q240,在實現對NIOS II處理器硬體開發時,使用嵌入在QuartuslI中的SOPC Builder來創建相應“軟” 硬體,通過NIOS II Development Kit來實現相應模塊之間的開發,為實現面陣CCD的採集所選用的相應外設自己定製,其中CCD採集控制IP 自定製。具體外設架構及內核結構框圖如圖4所示。

2.3 外同步行、場信號控制模塊

CCD晶元驅動控制及ADC採集的關鍵在於對時序的控制,特別是外同步HD、VD的控制要求很高,我們的系統中,採用計數分頻方式實現HD、VD 信號的產生,考慮到EP1C6Q240本身資源有限,我們在NIOS處理器外用CPLDEPM7128AETC100-10來定製同步信號IP核,同時此晶元中還包含有自動(手動)變焦控制,CCD 加(掉) 電控制等模塊。該模塊的關鍵在於行、場消隱以及行、場信號之間的對應關係,如果HD、VD信號不精確,系統將無法控制得到CCD的正常輸出信號。該模塊的時鐘HVCLK信號為36MHz晶振信號CKI經LR38642內部的2分頻后而得到,控制採集時由NIOS II發送一啟動控制信號START來啟動外同步行、場信號控制電路。

2.4 SCCB控制模塊

SCCB匯流排控制是I2C匯流排的一種,僅靠兩根連線就能實現全雙工同步數據傳送:一根串列數據線(SDA),一根串列時鐘線(SCL),在數據傳輸過程中嚴格依I2C匯流排協議,在我們的系統中,考慮到SOPc Builder中通用橋模塊中沒有Avalon Wishbone橋,我們利用PIO口模擬I2C匯流排方式來傳送控制字。對於該面陣CCD採集控制時SCCB控制用兩次,

第一次:通過ED0~ED2來設置LR38642中相應的寄存器組來產生CCD所需要的驅動脈衝以及對控制電子快門等。這一過程在上電複位時進行,ED0為啟動控制信號,當ED0啟動有效后,由ED1傳送時鐘脈衝,由ED2傳送數據,當25位控制字元寫到LR38642中相應的寄存器后,時序發生器電路產生不同垂直驅動脈衝組合及相關功能。

第二次:在採集控制時,通過控制CSN、SCK 以及SDATA實現PGA 控制,雙相關採樣控制,黑電平補償以及ADC的轉換等功能。每次寫入之後,為驗證寫入正確與否,把相應寄存器的數據讀出並與寫入的數據比較,如果相同,說明寫入正確,否則寫入錯誤。圖5給出了上電複位時實際配置波形。

2.5 ADC採集控制及存儲模塊(以幀累積模式為例進行說明)

在幀累積方式下,採集控制時,先從CCD光電轉換器讀出模擬數據,通過VD 給CCD 一個長度為T1 (T1=9×55.7ns×2640,其中2640為一個HD的時鐘CLK數,每個CLK為1/18M=55.7ns,9為保持9個HD) 的低電平,在VD)變為高電平時,CCD 在CLK 的同步控制下,HD先維持260個行消隱時鐘的低電平,隨後HD變為高電平,經464個時鐘的積累時間,再經過24個時鐘啞元象素,2個時鐘黑電平象素輸出后,在CLK 的同步控制下輸出2096個有用象素,輸出完有用象素后,再次進入行消隱階段,(進入行消隱的前54個時鐘輸出的為黑電平象素) 為下次行輸出做準備。在幀累積模式下採用奇偶兩場分別輸出,每場848個HD,其中場消隱9個HD時間內VD為低電平,隨後VD變為高電平,經58個HD場累積時間,以及2個HD的黑電平象素后,在HD的同步控制下,輸出780行有用象素,后再次進入場消隱階段進入行消隱的前5個時鐘輸出的為黑電平象素),依據先奇行后偶行的順序串列輸出視頻OS信號。當傳輸完2096*1560個像素時表明當前一幅圖像傳輸完畢,對於判別是否開始傳輸以及是否傳輸完畢,在我們的系統中,通過自定義的CCD採集IP核來對數據作出判斷。

自定義的採集IP核依HD、VD信號確定什麼時間開始為有用信號、什麼時間為結束有用信號,什麼時間表示一場(一行)數據開始(結束)等功能,知道了開始傳輸、結束傳輸、行(場)開始與結束等信息后,在NIOS II處理器的控制下,可以依IORD宏指令很容易將數據寫到SDRAM中。在我們的系統中SDRAM 選用採用HYNIX公司的HY57V561620CT-H型SDRAM存儲器。它的容量是256Mbit(16M *16bit),速度可以達到133M赫茲。為便於開發系統中SDRAM 控制器選用SOPCBuilder中的IP核。

下面給出基於自定義採集IP核以及GPIO讀寫宏指令實現數據採集的部分程序代碼。

……

while (IORD_ALTERA_AVALON_PIO_DATA (CCD_VD_ADDR)== 0x00);//場消隱(場逆程)

while (IORD_ALTERA_AVALON_PIO_DATA (CCD_VD_ADDR)== 0x01);//場正程,開始新的場CCD_VD= IORD_ALTERA_AVALON_PIO_DATA (CCD_VD_ADDR);

while(CCD_VD ==0x00)//等待場消隱開始寫入SDRAM ,如為場正程則不寫入SDRAM

{

while ((uchar)(IORD_ALTERA_AVALON_PIO_DATA (CCD_CLK_ADDR))== 0x00);

*SDRAM_Point=IORD_ALTERA_AVALON_PIO_DATA (CCD_VD_ADDR);

SDRAM_Point++;

}

2.6 CCD智能電源控制模塊

由於面陣CCD正常工作有嚴格的加(掉)電順序,所以必須嚴格按技術文檔要求按規定加(掉)電,對於電源模塊,我們選用了MAXIM 公司的Max685,Max687分別提供+15V,-9V 和+3.3V。為確保加(掉) 電順序,EPM7128AETC100-10內設計的電源控制模塊(EPM7128供電+3.3V 與CCD供電模塊分開),在系統上電后,當按下POWER鍵時控制Max685的SEQ 為高電平時,隨後Max685在SHDN及SYNC的控制下先輸出+15V,后輸出-9V,而後控制Max687的SHDN 為高電平控制輸出+3.3V。關閉(掉電)時,按下POWER鍵先控制Max687的SHDN 為低電平,關斷+3.3V,後設Max685的SEQ 為低電平時,在SHDN及SYNC的控制下控制先關斷-9V,再關斷+15V。

3 系統軟體

本採集系統模塊的軟體主要有兩部分:一是基於NIOS II的PIO 口實現模擬I2C匯流排功能,一是圖像數據寫入到SDRAM。其程序流程圖分別如圖7、圖8所示。

4 結束語

該面陣CCD採集系統利用NIOS II作為FPGA 嵌入式處理器的解決方案,能較容易地實現面陣CCD圖像的採集,由於採用“軟”硬體實現面陣CCD的開發,調試過程中能不斷更改“軟體”就可達到改進硬體功能目的。經實驗測試,在幀累積模式下可實現1.6s採集一幅靜止圖像。同時由於面陣CCD採集系統本身是一個複雜系統,不確定因素較多,如變焦控制、電磁兼容性等,對該系統還有待作進一步的研究。

[admin via 研發互助社區 ] 基於NIOS II處理器的面陣CCD採集系統設計已經有1823次圍觀

http://cocdig.com/docs/show-post-43105.html