1. 引言

對於用於視頻圖像處理的DSP 來說,由於前端的A/D 採集速度較低,一般為了減少DSP 的開銷,在視頻採集A/D 和DSP之間接入先進先出存儲器(FIFO) 作為緩衝。基於先進先出存儲器(FIFO) 的多樣性,一般在視頻採集與微處理器模塊之間很少提供無縫介面。傳統的方法是用簡單的邏輯電路實現很少一部分介面控制,大多數是通過軟體來實現,雖然軟體設計靈活性比較大,但是對軟體設計者提出很高的要求; 一般來說使用的都是線存的FIFO,這種FIFO 的存儲量比較少,會花費CPU 很大的開銷。

本文實現了一種在採集A/D 模塊、專用視頻FIFO 以及DSP 微處理使用CPLD 作為純硬體控制的方案。使用這種方案的創新點是首先因為使用的是幀存儲器FIFO,存儲一幀或者一場視頻數據,這樣可以大大減輕DSP的開銷,提高DSP 的效率,從而更好的提高視頻處理的實時性;其次因為介面邏輯比較複雜,一般用軟體實現起來比較困難,使用可編程CPLD實現全部的硬體介面邏輯,減少軟體設計的難度,減少DSP 的開銷。同時可以發揮CPLD 現場可編程的特點,可以像軟體一樣更改; 最後可以作為一個集成的通用硬體採集模塊。

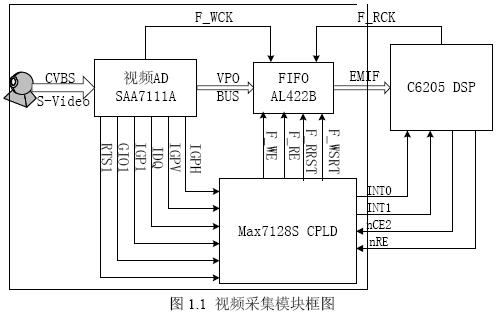

本文實現的是基於TI TMS320C6x 的DSP的視頻採集壓縮卡的A/D採集模塊以及介面控制模塊。在採集模塊主要功能是將從CCD 攝像頭輸入的模擬視頻信號轉換為數字信號,普通CCD攝像頭的輸出是NTSC 制式的複合全電視信號CVBS 信號,通過SAA7114H TV解碼晶元將模擬TV 信號解碼,轉換為符合ITU-R BT.601 標準的數字視頻信號,並且由CPLD 控制模塊將數據存儲到專用的視頻FIFO晶元,中斷DSP 讀取數據處理。具體的信號控制見圖1.1。

2. 模塊介紹

2.1. 視頻採集模塊

採集模塊採用PHILIPS 公司的視頻A/D 晶元SAA7114H,該專用視頻A/D 具有6 路模擬視頻輸入,兩個模擬預處理通道,並且抗混濾波、梳狀濾波都被集成到晶元內部,這樣對於硬體設計帶來了極大的方便。同時場同步信號IGPV,行同步信號IGPH,有效圖像數據輸出信號IDQ,時鐘輸出信號ICLK都有管腳直接引出,這樣省去了以往的時鐘同步電路的設計,可靠性也有所提高。系統內部鎖相環技術的集成使得可靠性和設計複雜度都有極大的降低。SAA7114H 的配置支持I2C,可以通過DSP的通用I/O 口軟體模擬I2C匯流排。

從圖2可以看出整個過程是在ICLK在上升沿觸發,在 IDQ 有效的情況下傳輸的數據有效,數據輸出的格式為(下為奇數場的一行數據掃描)

FF00 0080 U0Y0,V0Y1,U1Y2,V1Y3,…………,U319Y638,V320Y639

其中FF00 和0080 是奇數場標誌位。

當輸出IGPH 有效表明為一行數據的掃描,當IGPH無效的情況下,表明數據在回掃。從圖3可以看出當IGPV 有效說明是一場數據的掃描,當為無效時,說明為一場數據結束。通過這幾個狀態信號的輸出,以及其它標誌信號可以對行數據和場數據同步進行控制。具體見圖2.1(信號一行掃描輸出狀態) 和圖2.2(信號一場掃描輸出狀態)。

圖2.1 信號輸出狀態( 一行掃描)

圖2.2 信號輸出狀態( 一場掃描)

2.2. 視頻緩衝模塊FIFO

AL422B 是Averlogic 公司的專用視頻的FIFO,最大存儲為384K× 8bits,同時支持VGA,CCIR,NTSC,PAL 等視頻制式,兩端獨立的讀寫操作,支持不同速率的讀寫。根據CCIR.601協議,一場圖像數字化后最大的數據量是220K× 16bit,因此,採用的AL422B 足夠可以容納完整的一場視頻圖像的數據量。採用這種大的FIFO 的設計可以降低DSP 對視頻FIFO 讀寫控制時序的複雜度,使整個視頻圖像處理流程簡捷,同時減少控制信號。

2.3. CPLD控制模塊

該模塊的組成主要是一片Altera 公司的CPLD 晶元EPM7128STC100,其主要功能是提供DSP 的EMIF 介面與視頻FIFO 相連時所需的一些額外的輔助邏輯(glue logic)。另外一個重要的功能是通過檢測SAA7114H 輸出的同步信號來生成DSP 中斷,通知DSP 讀取視頻FIFO 中已滿的一場圖像數據。(視頻FIFO AL422B 的容量為384K× 8bits,系統中使用兩片並聯成16bits的介面寬度,整個視頻FIFO可以一次存放一幀的視頻數據。)

CPLD通過SAA7114H的輸出狀態信號以及TMS320C6x DSP的相應輸出控制信號生成FIFOAL422B 的控制信號。具體為:

3. 實驗結果:

圖3.1 是採用QCIF(176× 144) 格式的視頻圖像,壓縮編碼演算法採用M-JPEG2000標準。其中前一幅是無損壓縮恢復的結果圖,后一幅為有損壓縮。相應的壓縮編碼指標如表3.1 所示。

| 圖像格式 | 編碼后碼率 | 壓縮比 | 內存佔用 | 耗 時 |

| 176× 144 | 11.9KB/幀 | 2.074 | 801KByte | 0.05 秒 |

[admin via 研發互助社區 ] 基於CPLD控制的通用視頻採集模塊已經有2459次圍觀

http://cocdig.com/docs/show-post-43098.html