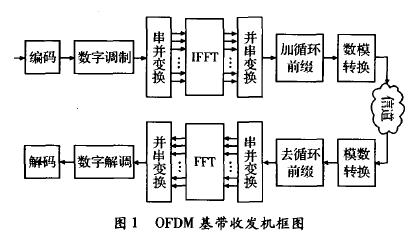

正交頻分復用(OFDM)是一種多載波調製技術,可以有效地對抗頻率選擇性衰落和窄帶干擾,並且有較高的頻譜利用率。OFDM技術已經成功地應用於非對稱數字用戶環路(ADSL)、數字音頻廣播(DAB)、高清晰度電視(HDTV)、電力線載波通信(PLC)、無線區域網(WLAN)等系統中。典型的OFDM基帶收發機如圖1所示,其中的多載波調製/解調由IFFT/FFT來實現。

對於FFT處理器的實現, 目前通用的方法是採用DSP、專用FFT處理晶元和FPGA。用DSP實現FFT的處理速度較慢,不能滿足某些高速信號實時處理的要求;專用的FFT處理晶元雖然速度較快,但外圍電路相對複雜,不易擴展,且價格昂貴。新一代FPGA資源豐富,易於組織流水和并行的結構,用其實現FFT,不僅可以提高處理速度,而且具有靈活性高,開發費用低的特點。

1 設計與實現

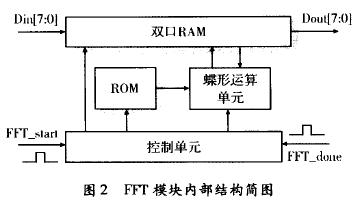

本設計為128點FFT,採用簡單實用的基2時間抽取(DIT)演算法。該模塊的FFT處理共需3個過程,即外部數據倒序輸入過程,FFT中間運算過程(128點的FFT運算可分解成7級運算,每級64個基2蝶形運算)和運算結果正序輸出過程。整個FFT模塊內部結構簡圖如圖2所示。該FFT模塊主要包括蝶形運算單元、控制單元和存儲單元(ROM和雙口RAM)。

1.1 蝶形運算單元

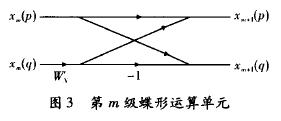

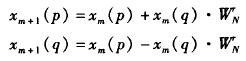

基2時間抽取蝶形運算信號流圖如圖3所示。

其中,括弧內的p和q表示數據的序號;xm(p),xm(q)是第m級蝶形運算的輸入,

由上述公式可以看出,一個基2蝶形運算要進行1次復乘、2次復加。若在一個時鐘周期內完成復乘,則需要4個實數乘法器和2個實數加法器。因為一個蝶形運算需要取兩個輸入數據,而只存在1次復乘,所以可以用2個時鐘周期來完成1次復乘,即可以對實數乘法器進行復用,從而減少乘法器的數目同時不降低處理速度。

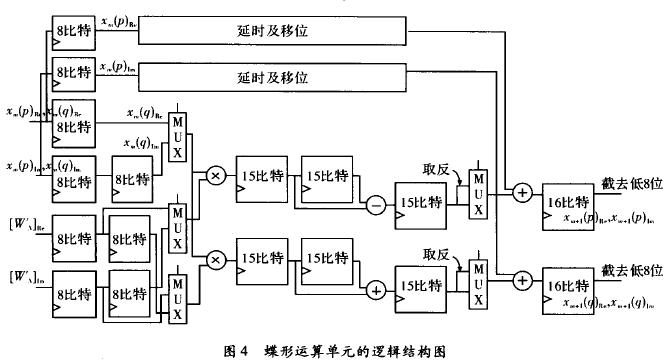

改進后的基2蝶形運算單元充分利用了FPGA片內的寄存器,採用流水和并行的結構將復乘所需的4個實數乘法器減少到2個,其邏輯結構如圖4。從中可以看出,蝶形運算單元主要由寄存器、選擇器、乘法器和加法器構成。左邊3個選擇器用來選擇做乘法的數據,右邊2個選擇器用來選擇加法器的加減功能。

該蝶形運算單元中的復乘運算是2個8比特的複數相乘得到15比特的複數。因為輸入數據和旋轉因子的8比特數據實際上表徵的是模值不大於“1”的復小數,所以復乘運算的輸出結果用15比特表示並不會產生溢出。2個15比特的數據進行復加運算得到16比特的結果。為便於下一級運算,將復加運算輸出的16比特數據截掉低8位(採用定點四舍五人的方法以減小誤差)。128點FFT的7級運算中每一級的數據都相當於先左移了7位(旋轉因子的模值為128),而後又截掉了低8位,所以每一級都相當於做了除2運算,故此128點FFT輸出結果是理論值的(1/2)7。

1.2 控制單元

控制單元是整個FFT模塊的核心。主要有以下兩個功能:

1)提供各個模塊的運算使能。

當檢測到輸入口的FFT_start信號后,立即開始接收數據,並反序存儲到RAM中。在128個時鐘周期之後,啟動各級的蝶形運算,並同時產生RAM的讀寫使能信號。在第7級運算結束時,提供數據輸出的標誌FFT_done,並控制RAM 同步正序輸出數據。

2)產生各級運算所需的地址

產生FFT輸入的倒序地址和輸出的正序地址(正序和倒序均用同步計數器實現,正序為當前計數器的輸出,倒序為當前計數器的高位與低位的對應位全部對調后的輸出);各級運算的地址(按照計數器的輸出,根據各級蝶形運算的規律產生。先產生蝶形運算第一個數據的RAM地址,再產生第二個數據的RAM地址;在產生以上兩個取數地址的同時,產生所對應的旋轉因子的ROM取數地址)。

1.3 存儲單元

該FFT模塊中的存儲單元(ROM和雙口RAM)由Xilinx ISE 6.2i的CORE Generator工具根據FPGA的型號生成。

本FFT設計中有2個ROM分別用來存儲旋轉因子,並以補碼的形式將它們按照*.mif格式文件輸出。用工具例化ROM,將*.mif文件寫入各自的ROM初始化文件中,完成對ROM的初始化。

通常的FFT設計採用的是有2塊(按實、虛部分開算是4塊)RAM的“乒乓”式結構,而在處理速度要求不太高的情況下,可以採用1塊(按實、虛部分開算是2塊)RAM來完成,進而節省RAM資源,便於以後的ASIC開發。在此FFT模塊的設計中,有2個分別用來存儲數據實部和虛部的雙口RAM(埠a只寫,埠b只讀)。RAM的兩埠可以在讀寫地址不同的情況下同時工作,即在通過埠b從RAM中讀取蝶形運算數據的同時,也在通過埠a往RAM 中寫入上幾次蝶形運算的結果。

2 模擬與分析

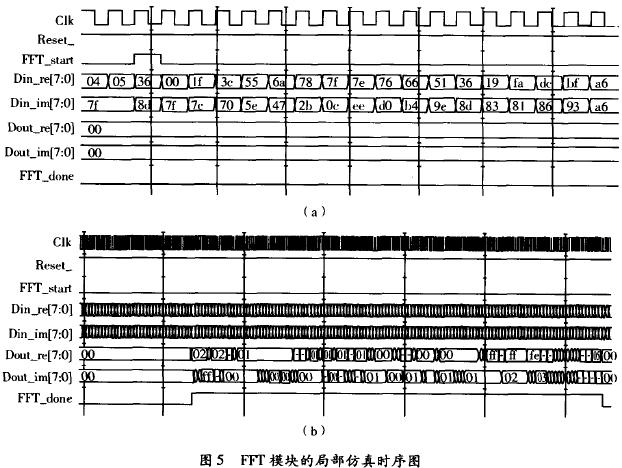

採用Verilog HDL對所設計的FFT模塊進行RTL描述。FFT處理點數為128,輸入輸出用8比特補碼錶示。採用MoldSim SE 5.8a對整個設計進行功能模擬,採用Synplify Pro 7.3.3進行綜合;使用Xilinx的ISE 6.2i工具配置比特流下載;FPGA選用Xilinx Spartan II系列中的xc2s200pq208-5。用MoldSim進行模擬的局部時序如圖5所示。

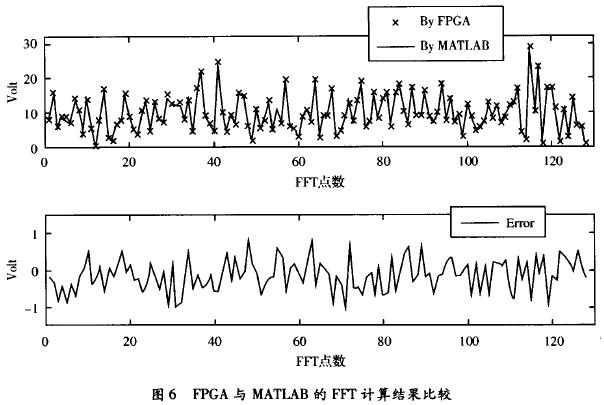

將MATLAB的計算結果與FPGA的模擬結果進行對比,如圖6所示。可見兩組結果能較好地吻合,從而驗證了所設計的FFT模塊的正確性。

整個FFT模塊在Spartan II的xc2s200pq208-5上共用去邏輯單元(LUTs)393,佔總資源的8%,這樣就為OFDM系統其他模塊的設計節省了大量資源。

128點FFT需要完成蝶形運算 (128/2)×log2128=448次,每個蝶形運算需要2個時鐘周期,蝶形運算需要7個時鐘周期的延時,收發外部數據需要128×2=256個時鐘周期,所以整個FFT運算共需要時鐘周期448×2+7+256=1159個,在處理速度上達到了預期的目標。

3 結論

本文中設計的FFT模塊採用基2時間抽取演算法,用verilog HDL對其進行了RTL描述,用MoldSim和Synplify工具進行了模擬和綜合,並在Xilinx Spartan II FPGA中進行了驗證。

此外,FFT運算結果的精度與輸入數據的位數及運算過程中的位數有關。在定點計算中,存儲器數據的位數越大,運算精度越高,使用的存儲單元和邏輯單元也越多。在OFDM系統的實際應用中,可以根據實際情況折衷選擇FFT模塊的精度和資源。

本文所設計的FFT模塊的輸入、輸出和旋轉因子為8比特數據,採用了1塊(按實、虛部分開算是2塊)雙口RAM和基2單蝶形流水運算的結構,達到了某些OFDM系統對FFT模塊的精度和資源的要求,為OFDM系統的ASIC的開發提供了很好的依據。

[admin via 研發互助社區 ] OFDM中的FFT模塊設計及其FPGA實現已經有4910次圍觀

http://cocdig.com/docs/show-post-43087.html