摘要:本文簡要的總結了在高速數字設計中串聯終端匹配和並聯終端匹配的優缺點,並對這兩種匹配方式的終端匹配電阻處於不同位置時的匹配效果做了相應的模擬和深入的分析,得出了串聯終端匹配電阻對位置的要求沒有終端匹配電阻嚴格這一結論,給出了一些關於終端匹配電阻擺放位置的建議。為在PCB 設計中如何放置終端匹配電阻提供了理論和實踐上的指導。

1 引言

隨著半導體工藝的快速發展,信號上升時間愈來愈短,導致信號完整性問題日益突出;另外,器件小型化趨勢也日益明顯,電路板的面積也越來越小,因此對PCB 板的布局要求也日益嚴格。這就要求高速PCB 設計工程師嚴格的去考慮各種器件的放置問題,包括濾波電容、匹配電阻等,在提高系統的信號完整性的同時節省印製板面積。本文利用Mentor 公司的Hyperlynx 模擬軟體對簡單並聯終端匹配和串聯終端匹配方式進行了模擬和分析,研究不同位置的匹配電阻對信號質量的影響。

2 並聯終端匹配和串聯終端匹配的優缺點

在高速數字設計中,電阻常被用來對傳輸線進行阻抗匹配,以消除傳輸線上的反射。最典型簡單的匹配方式有兩種:簡單並聯終端匹配和串聯終端匹配。簡單並聯終端匹配電阻與具有極高輸入阻抗的接收端並聯,並且接地或者電源,以消除接收端的反射,優缺點是能夠比較精確的選擇匹配電阻的阻值但是將消耗直流功率功耗。串聯源端匹配電阻與小輸出阻抗的驅動器串聯,以吸收接收端反射回來的信號,此方式的優缺點是不消耗功率但是由於許多驅動器都是非線性的,如TTL 器件,其輸出阻抗隨著器件邏輯狀態的變化而變化,從而導致匹配電阻的阻值難以確定。故在要求低功耗的數字設計中,串聯終端匹配方式更常用;並聯終端匹配方式更多的使用在模擬電路設計中,以犧牲功耗來滿足其高精度的要求。本文將總結出串聯終端匹配方式的另一優點即其匹配電阻在PCB 板中對位置的要求沒有簡單並聯終端匹配方式嚴格。

3 匹配電阻位置的變化對信號波形的影響

3.1 並聯終端匹配情況-匹配電阻位於接收端之前

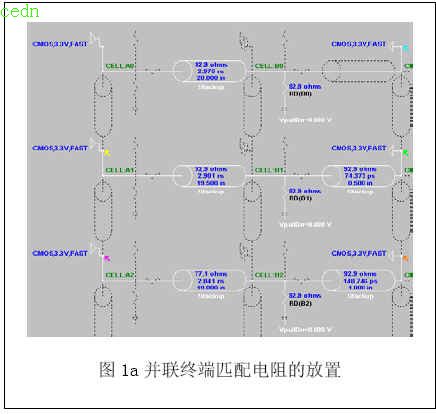

如圖1a 所示,我們構建了三組終端匹配的結構。第一組結構中終端匹配電阻直接與接收器相連(理想狀態,圖1a 上);第二組結構中終端匹配電阻位於距離終端0.5in.處(圖1a 中),即有0.5in.的傳輸線沒有被匹配;第三組結構中終端匹配電阻位於終端1in.處(圖1a 下)。驅動器和接收器模型選用Hyperlynx7.0 自帶的簡易IBIS 模型:CMOS,3.3V,FAST(該模型驅動波形的上升時間約為1.5ns)。傳輸線特徵阻抗為92.9 歐姆,傳輸線總長為20in.(約為0.5m 左右),總的延遲時間為2.975ns,線寬為6mil。驅動信號的頻率為100MHZ,

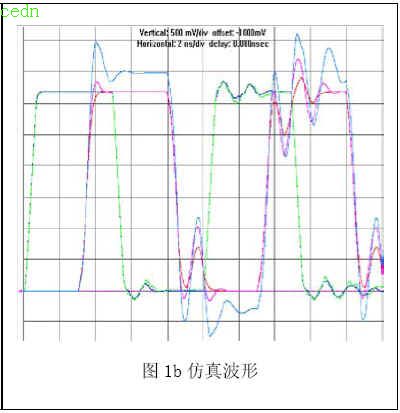

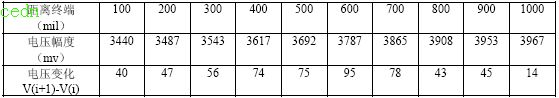

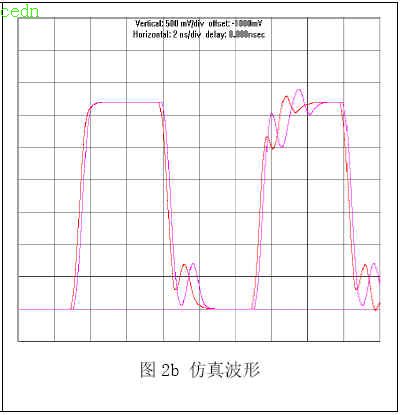

圖1b 為使用Hyperlynx7.0 模擬工具得到的模擬波形,如圖所示,有明顯延遲的三組波形為接收端波形,其中幅值最低的為匹配電阻位於理想狀態時的波形;幅值最高的為匹配電阻位於接收端前1in.處的波形;中間的為匹配電阻位於接收端前0.5in.處的波形。測得三種情況下接收端電平最大幅值分別為3.4V,3.7V,4.1V。從圖 1b 和表1 中可以看出終端匹配電阻與接收端之間的距離每增加100mil,信號過沖就將增加幾十毫伏,可見,改變終端匹配電阻的位置的確會給信號質量帶來很大的影響,原因是如果匹配電阻距離接收器很遠,將有一段可被視為傳輸線的PCB 連線得不到應有的阻抗匹配,從而導致信號在接收端產生反射現象,反射到驅動端的信號將再次反射回接收端,這樣就會大大降低了接收端信號的質量。因此在高速 PCB 設計中應設法使得這樣一個分支長不超過100mil。

表1 並聯終端匹配電阻位於接收端不同位置時測得的接收端信號最高電壓值

3.2 並聯終端匹配情況-匹配電阻位於接收端之後

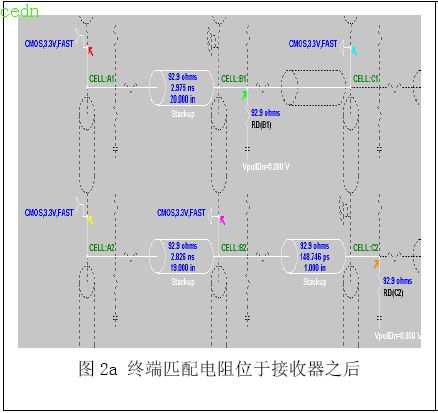

當然在具體的PCB 設計中,由於種種原因設計者也許無法將終端匹配電阻放置在接收端之前,那麼只能將其放置在接收端之後。在圖2a 中,上半部分為終端匹配電阻位於理想位置的情形(即直接與接收器相連),下半部分為終端匹配電阻位於接收器之後的情形,匹配電阻與接收器之間有一段 1in.長的傳輸線。圖2b 為圖2a 對應的模擬波形,可見,在匹配電阻位於接收器之後時,接收端的波形非常接近匹配電阻位於理想位置的波形,只是波形的延遲更大,經測量得到這個延遲近似等於這個電阻與接收器之間的傳輸線的延遲。

因此可以得出結論,將終端匹配電阻放置在傳輸線之後幾乎不會影響其匹配效果。在實際的PCB 設計中,完全可以採取這種做法以儘可能的使匹配電阻的位置接近理想的狀態,這是一種很好的選擇。

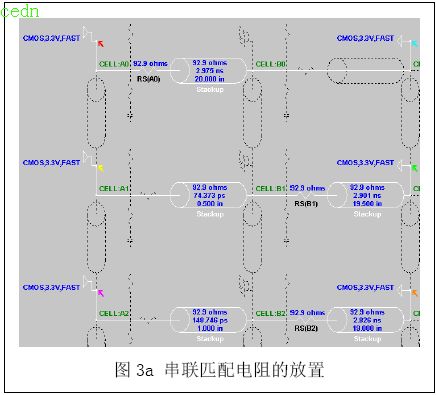

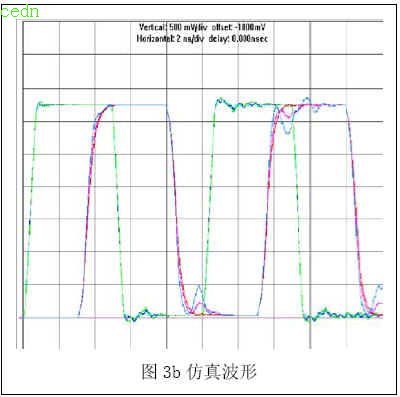

3.3 串聯終端匹配情況

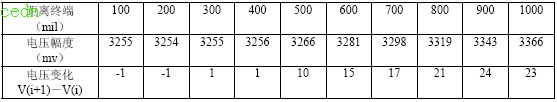

圖3a 構建了三種源端匹配結構,類似於終端匹配的情形,這三種結構分別為匹配電阻直接與接收器相連(理想情況);與接收器相距0.5in.;與接收器相距 1in.。圖3b 為圖3a相對應的模擬波形。從波形中可以看出,三種情況下的模擬波形變化不是太大,遠沒有終端匹配那樣劇烈。測得三種情況下接收端電平最大幅值分別為: 3.256V,3.266V,3.366V。

從下表2 也可以非常明顯的看出源端匹配電阻的位置變化並不會給信號質量帶來很大的影響。

表2 串聯終端匹配電阻位於驅動端不同位置時測得的接收端信號最高電壓值

從前面的分析可知,串聯終端匹配電阻主要用於吸收從接收端反射回來的信號,由於接收端輸入阻抗很大,可以視為開路,所以信號到達接收端時將產生全反射,反射回的信號能量大部分將被驅動端的匹配電阻和驅動器吸收,因而從驅動端二次反射回來的能量很少,故串聯終端匹配電阻適當的遠離接收端放置,不會嚴重的影響接收端的信號質量。但對於並聯終端匹配來說,如果匹配電阻遠離接收端放置,接收端之前將有一段傳輸線得不到匹配,而且驅動端沒有串聯終端電阻不會吸收掉從接收端全反射回來的能量,因而信號將來回反射,使得接收端信號的質量大大降低。這是串聯終端匹配電阻對位置的要求沒有並聯終端匹配要求嚴格的部分原因。

4 結論

通過上文對並聯終端匹配電阻和串聯終端匹配電阻處於不同位置情形的模擬和分析研究,可以得出結論即串聯終端匹配電阻對位置的要求沒有並聯終端匹配電阻嚴格,也就是在實際的PCB 設計中,可以適當的將串聯終端匹配電阻遠離驅動器放置而不必擔心這樣做會給系統的信號完整性帶來很大的問題。另外,模擬結果顯示使用並聯終端匹配方式時將匹配電阻放置在驅動器之後也不會對信號波形產生很大的影響。

[admin via 研發互助社區 ] 高速PCB 設計中終端匹配電阻的放置已經有14733次圍觀

http://cocdig.com/docs/show-post-44562.html