隨著電子技術的飛速發展,電子產品越來越來越趨向高速、寬頻、高靈敏度、高密集度和小型化, 這種趨勢導致了PCB電路板設計中電磁兼容(EMC)問題的嚴重化.特別是電源和地線的電磁干擾(EMI)問題,成為目前PCB電磁兼容設計中急待解決的技術難題和系統工程。

1、電源和接地在電磁兼容中的影響

電磁兼容性是指設備或者是系統在其電磁環境中能正常工作且不對該環境中任何事物構成不能承受的電磁干擾的能力。電磁兼容包括干擾源、耦合通路和敏感體三要素。隨著數字時代電子產品的發展,特別是高速PCB設計中,數字電路PCB使電子產品的電磁輻射加重,同時,信號線之間的串擾問題和電容耦合也大大增加。這種干擾主要是由於電源電網雜訊的污染以及地線存在阻抗不匹配造成的,包括來自變壓器的電源雜訊、電源匯流排電壓瞬變造成的電磁輻射、接地系統偏離零電位過大造成的干擾電壓、傳輸線路始端和終端的地線雜訊等。因此,在數字電子設備的抗干擾對策上,電源雜訊和接地阻抗成為電磁干擾主要的研究對象,合理進行電源和地線的設計和布局成為解決EMC問題的關鍵途徑。

2、電源和接地在電磁兼容中的干擾分析

2.1電源干擾分析

由於電子電路通過電源電路接到電網,所以電網的雜訊可以通過電源電路干擾電子線路。在PCB電路板設計中,由電源造成的電磁兼容問題主要是電源雜訊,主要表現在下面三個方面:

(1)眾多的電子產品大量應用數字器件、模擬器件及數字模擬混合器件,如DSP晶元、CPU、動態RAM、D/A 變換器和其他數字邏輯器件等.它們工作時會引起電路板內電源電壓和地電平波動,導致信號波形產生尖峰過沖或衰減震蕩,造成IC電路的雜訊容限下降,從而引起誤動作。

(2)大部分電子電路的供電系統是採用交流變壓→整流→濾波→穩壓得到. 因此變壓器的耦合成為電源雜訊傳播的主要途徑。變壓器的初次級線圈存在分佈電容,通常達幾百pF,對高頻雜訊有很低的阻抗,電網高頻尖峰脈衝能夠穿越變壓器而產生電源雜訊。

(3)由於輸電線存在電阻,當電源過壓、欠壓、斷電等故障均能產生雜訊干擾。這些干擾常常是緩慢變化,稱為電源的慢變化干擾。

2.2 地線干擾分析

地線不僅作為電位基準點的等電位點,還可以作為信號的低阻抗迴路。它的電位並不是恆定的,地線上最常見的干擾就是地環路電流導致的地環路干擾。

(1)地線電磁干擾

地線的實質是信號迴流源的低阻抗路徑。由於地線的阻抗不為零,引起地線各點電位差的形成。從而造成電路的誤動作,形成地線干擾。而地線阻抗主要是由導線的電感引起的,頻率越高,阻抗越大,這也是造成電磁干擾的主要因素。因此,減少這些干擾重點在於儘可能減小地線的阻抗。對於數字電路尤為重要。

(2)地環路干擾

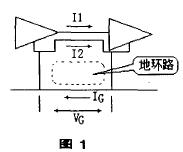

由於地線阻抗的存在,當大電流流過地線時,會產生很大地電位差。如圖1,兩大功率電器由於電路的不平衡性.每根導線電流不同,形成差模電壓。構成環路干擾。這種干擾主要是由電纜與地線構成的環路電流產生的。稱為地環路干擾。

(3)公共阻抗干擾

當多個電路共用一段地線時,由於地線阻抗的影響,一個電路的地電位會受另一個電路工作電流的限制,同時,一個電路的信號也會耦合進入另一個電路。形成公共阻抗干擾。如圖2所示。

由於電磁干擾主要是由電源線和地線的阻抗和分佈電感引起的, 按照Er=IR和EL=L(dI/dt),電流的變化率越快。分佈電感產生的感應電壓就越大。在高速PCB電路板設計中, 由於時鐘頻率很高。而且電流的變化很快,所以“dI/dt”很大,電磁干擾問題就更加明顯和突出。

3、電磁兼容設計處理

3.1 電源線的電磁兼容設計處理

(1)根據印製板PCB 電流的大小,盡量加大電源線寬度。減少環路電阻,同時,使電源線、地線的走向和數據傳遞的方向一致。有助於增強抗雜訊能力。

(2)盡量選用貼片元件,縮短引腳長度,減少去耦電容供電迴路面積,減少元件分佈電感的影響,有利於實現電磁兼容。

(3)在電源變壓器前端加裝電源濾波器,抑制共模雜訊和串模雜訊,隔離外部和內部脈衝雜訊的干擾。

(4) 印製電路板的供電線路應加上濾波器和去耦電容。在板的電源引入端加上較大容量的電解電容作低頻濾波. 再並聯一隻容量較小的瓷片電容作高頻濾波。

(5) 不要把模擬電源和數字電源重疊放置避免產生耦合電容,造成相互干擾。

3.2 地線的電磁兼容設計處理

(1)為了減少地環路干擾.必須想辦法消除環路電流的形成,具體可以採用光隔離器、變壓器、共模扼流圈切斷地環路電流的形成或者採用平衡電路消除環路電流等。

(2)為了消除公共阻抗的耦合,可減小公共地線部分的阻抗,加粗地線或對地鋪銅處理;另一方面可以通過適當的接地方式避免相互干擾,比如並聯單點接地(圖3)或串並聯混合單點接地(圖4),徹底消除公共阻抗。

(3)數字地和模擬地要分開,並單獨設置模擬地和數字地。低頻電路為防止串擾,地線應盡量採用單點並聯接地,高頻電路宜採用多點串聯接地,地線要短而粗,高頻元件周圍盡量用柵格狀大面積鋪銅加以屏蔽。

(4)對於多層扳,應專門設置地線層。

(5)印製板導線的電感與長度和長度的對數成正比,與寬度的對數成反比,為減少地線的電感,應盡量減小導線的長度。

4 結束語

電源和地線的干擾問題是電磁兼容設計中必須慎重考慮並解決的關鍵一環。它與PCB電路板的性能有著密切的聯繫.但它只是電磁兼容設計中的一部分。在EMC設計中,還要考慮反射雜訊、串擾雜訊、輻射發射雜訊、退耦電容、元件布局和其他工藝技術問題等因素的影響和干擾。通常,採用以上的抗干擾措施,可大大地消除電源和地線的電磁干擾,但過多的採用抗干擾措施,也會產生新的干擾,導致系統成本的增加,系統可靠性下降。所以應根據設計條件和目標要求,合理採用抗EM[措施,設計出具備良好EMC 性能的PCB 電路板。

[admin via 研發互助社區 ] PCB電磁兼容設計中的電源和接地研究已經有4912次圍觀

http://cocdig.com/docs/show-post-44280.html