概述

隨著數字電子產品小型化、高速化的市場需求,數字電路板的設計日益受到重視。由於高速數字電路大多是小型CMOS組件所構成,因此本文以FR-4電路板為前提,深入探討有關高……

隨著數字電子產品小型化、高速化的市場需求,數字電路板的設計日益受到重視。由於高速數字電路大多是小型CMOS組件所構成,因此本文以FR-4電路板為前提,深入探討有關高速數字電路板的設計技巧。

設計高速數字電路板的20項要訣

- 使用低誘電率與低誘電正接的電路板

高誘電率的電路板容易導通電磁界,因此極易受到噪訊干擾,一般RF-4的誘電率為4.8,誘電正接為0.015左右;低誘電率的電路板為3.5,誘電正接為0.010左右。由於低誘電率電路板的價格比一般電路板高,因此選用上必需作全盤性檢討。 - RF-4的頻率極限為2.5G~5.0GHz

以往認為60MHz是電路板上的信號傳輸速度極限,不過事實上目前PC主板的bus信號傳輸速度大多超過400MHz,若以主板的現況而言,能夠作如此高速的信號傳輸,主要原因是利用shield將阻抗(impedance)為60Ω左右的pattern包覆,使其特性等同於一般pattern長度,也就是說實際上電路板並未超過2.5~5.0GHz的信號傳輸物理極限。 - 盡量使用多層電路板

使用內層為電源層的多層電路板具有下列優點:

*電源非常穩定。

*電路阻抗(impedance)大幅降低。

*配線長度大幅縮短。

相同面積作成本比較時,雖然多層電路板的成本比單層電路板高,不過如果將電路板小型化、噪訊對策的方便性等其它因素納入考慮時,多層電路板與單層電路板兩者的成本差異並不如預期中的高。例如小型高密度配的場合,一般認為使用4層電路板可獲得良好的電路特性。表1是日本國內雙面電路板與4層電路板成本比較實例。 | 電路板尺寸 (mm) | 每片單價(日圓) |

| 雙面電路板 | 4層電路板 |

| 59×22×0.8 | 30(1萬片order) | --- |

| 48×42×1.2 | 80(500片order) | --- |

| 150×130×1.6 | 680(100片order) | 1200(100片order) |

| 230×130×1.6 | 940(100片order) | 2000(100片order) |

| 299×178×1.6 | --- | 1540(100片order) |

根據表1的數據單純計算電路板的面積成本時,每一日圓的面積雙面電路板約為28左右,4層電路板則為16,也就是說4層電路板的使用面積若能降低1/2,面積成本就與雙面電路板相同。雖然批量多寡會影響電路板的單位面積成本,不過尚不致有4倍的價差,如果發生4倍以上的價差時,?要設法縮減電路板的使用面積,並設法降至1/4以下即可。 - 盡量使用micro strip line與strip line

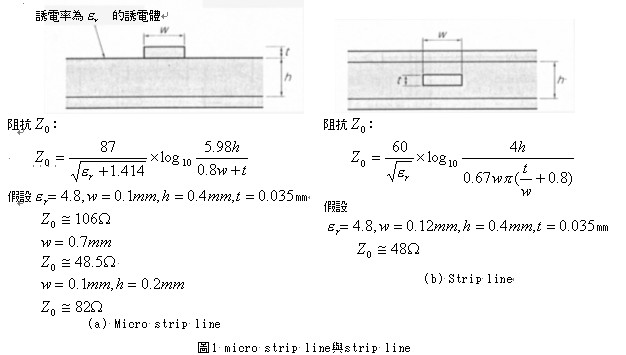

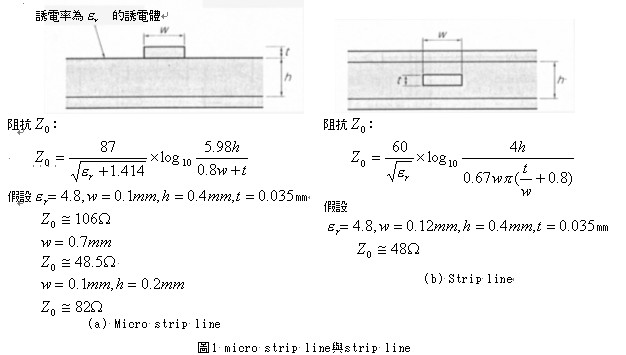

CMOS的輸出阻抗(impedance)為50~100Ω左右,如圖1所示micro strip line與strip line,可使pattern impedance收斂在50~100Ω範圍內

阻抗的計算方法

如果直接使用電路板製作廠商提供的阻抗(impedance)layout電路,極易招致成本上揚的窘境,為了能在設計時間使阻抗維持在50~100Ω範圍內,除了確認電路板的標準厚度,再決定pattern寬度之外,亦可直接指定電路板的厚度要求廠商製作,因為事前嚴謹的電路板選定作業,可使電路獲得預期性的效果。根據圖1的計算式,假設micro strip line的場合,pattern寬度為0.1mm,絕緣層厚度為0.2mm時,阻抗則為80Ω;如果絕緣層厚度為0.4mm時,配線阻抗可收斂至100Ω範圍內。值得一提的是實際上pattern的寬度經過整修後會變得更細窄,例如寬度為0.15mm的pattern,經過蝕刻整修後會變成0.1mm。

雖然信號pattern如果設有ground shield時,必需使用其它的計算公式計算,不過基本上阻抗(impedance)卻不會有太大改變。此外雙面電路板的其中一面如果設置ground的better pattern,便可獲得某種程度的改善。

strip line對噪訊對策具有極佳效果

雖然電路板若未超過8層以上,無法發揮噪訊對策效果,不過8層以上電路板的配線容量高達 並不適合高速信號傳輸,然而噪訊對策上卻具有極佳的效果。 - 4層電路板的第2層作接地層(ground)

若與電源層比較,ground具有很好的噪訊低減效果。如圖2所示將ground設於第2層,再以組件信號層為中心作高速配線,換言之高速配線必需全部設於組件面上。

- 利用終端電阻作阻抗(impedance)整合

一般阻抗(impedance)整合

一般IC的輸出阻抗都很小,輸入阻抗卻很大,因此多餘的input電流會跳返引發反射。由於ECL與clock drive的輸出阻抗被設計整合成50Ω,因此通常會使用圖3(a)的整合電路;相較之下一般CMOS邏輯IC的輸出阻抗為50~100Ω左右,如果用100Ω作整合,勢必形成圖3(b)的結構,造成clock drive等高輸出組件除外的輸出產生不足現象,因此設計上必需設法滿足消耗電流增大的需求。

直列終端可降低消耗電流

由於上述圖3的方法不但會使消耗電流增大,同時還會造成傳輸特性惡化,傳輸速度減緩等問題,如果改用圖4所示增加直列終端電阻法,便可可獲得很好的效果,這種方法稱為「直列終端電阻法」或是「damping電阻法」。具體而言這種直列終端電阻方法?需準備pad,必要時可作0Ω阻抗跳線(jumper)或是添加ferrite core即可。此外如果使用站立與下降時間很長的低速組件,對降低電源電壓與消耗電流具有極佳的效果。

- 表面信號層作better pattern處理

若無法確保return電流路徑,會有噪訊外漏之虞

字如果電流從IC流至IC,該return電流會折返原IC,也就是說若無法確保return電流路徑,電流會迴繞變成噪訊。雖然多層電路板內層的ground可用shield保護,不過via等孔穴會使return電流散亂,為了迴避其它信號的via,所以往往會在better作slit。

ground shield

為了確保return電流的shield,同時防止return電流與鄰接信號線發生cross talk現象,因此在表面層設置ground的better pattern(圖5(a)),類似這種利用ground將信號包覆方法稱為「ground shield法」。

clock line或是高速line如果能在各line上設置ground shield,便可獲得很好的效果,如果情況不允許時可參考圖5(b)的方法,以數條line為block,再用gro und line將信號包覆,需注意的是採用此種方法的ground shield,必需確認數量眾多的via是否與內層的ground層連接。此外ground shield與信號線之間若有0.1m m左右的間隙,配線容量便會高達 。雖然上述方法具有很好的噪訊對策效果,不過如果信號傳輸延遲成為主要問題或是信號線很長時,就需將gro und shield與信號線之間的間隙加大。 - LSI下方設置better pattern

由於LSI本身就是噪訊發生源,所以噪訊很嚴重時必需用鋁質case將package包覆,雖然任意使用via會造成預期外的傷害,不過適時利用如圖6的結構,建立有效的better pattern可以很容易吸收噪訊。

- 配線彎曲 減少via的使用,盡量作同層配線

如圖7(a)所示pattern直角彎曲后,會改變pattern的寬度,造成阻抗(impedance)發生變化極易引起反射;圖7(b)的via如果也作直角彎曲,同樣會造成阻抗發生變化並引起反射,換句話說不論是pattern或是bare彎曲,設於組件面上而且是圓弧狀乃是最高理想,不過實際上圓弧配線非常困難,所以改采如圖7(c)所示的 彎曲,進而減少pattern的寬度變化,此外必需注意的是減少via的使用,同時必需盡量設法作同層配線。

- 不可用via內層逃孔在內層作slit

如圖8(a)所示land直徑為0.66mm,drill直徑為0.35mm小孔徑的內層逃孔,孔徑為1.0~1.2mm。為了配合SOP-IC的腳架間距,因此將via以1.27mm的間距作直線狀排列(圖8(b)),卻因此在內層造成slit進而導致部份better pattern分離。為避免產生slit所以將via改成如圖8(c)的排列方式。用直徑為0.35mm的鑽頭(dri ll)在直徑為1.0 mm範圍內貫穿,對電路板製造廠商而言是相當嚴苛的要求,因此事後的尺寸確認非常重要。

- 盡量降低配線長度

根據實驗數據與模擬分析結果顯示,配線長度低於100mm時可獲得極佳的噪訊對效果,也就是說利用多層板並降低配線長度,或是使FPGA的腳架排列優化對配線長度具有重大意義。此外clock line的配線,盡量利用FPGA/PLD或是clock dri ve,設法獲得長度為1:1的配線。

- 配線直線化

文連接bus時配線配線直線化乃是最基本的設計,如圖10 (a)的T型配線極易在連接部位產生反射,因此必需改成圖10(b)直線化配線。

圖10 直線狀配線實例 - 非高速性電路盡量使用低速組件

由於高速電子組件的信號變化速度非常快,使得電路的電感(inductance)具有很大的影響力。如果不是高速電路盡量使用類似HC-CMOS低速電子組件。 - 盡量使用表面封裝電子組件

lead組件的導線(lead)會變成具有電感的成份,進而對電路造成不良影響,所以高速數字電路盡量使用表面封裝電子組件,必需注意的是socket組件極易招致不良結果,因此設計上非必要時應該盡量避免使用socket組件。 - damping阻抗與ferrite core對clock line與bus line具有極佳效應

如以上的說明damping阻抗與ferrite core對clock line與bus line具有極佳效應,而且是低成本高效益的終端方法。

在line準備pad,可邊量測噪訊邊作調整

如圖11所示一般會在clock line上設置1608等級的電阻pad,接著邊量測噪訊邊更換數十Ω的電阻作調整,此外也可以使用具備合適頻率特性的ferrite core。若不需使用電阻或是filter core時,量產前?需委託電路板廠商在pad之間作短路即可。

輸出端子附近設置damping電阻

輸出端子附近設置damping電阻乃是設計上基本要求,不過data bus等雙向配線的場合,則需在所有端子附近設置10Ω左右的電阻。雖然它的動作原理與上述終端阻抗相同,不過插入damping電阻會降低數據傳輸特性與傳輸速度,因此若有skew的考慮時,必需注意電阻值與配線長度的匹配性。 - 與外部作In/Out的部位,需使用ferrite core

如圖12所示儘可能在input部位插入1k~10kΩ直列電阻,藉此保護電子組件不會受到靜電噪訊干擾,同時還可以防止噪訊流出。此外使用大電流容量的ferrite core,防止噪訊從output部位流出。值得一提的是電源層、其它配線與connector之間若無充裕的空間時,允許利用C結合的噪訊進入。

- bus line與其它信號線必需相隔1mm以上

CPU控制的bus line是等信號穩定后才開始讀取信號,因此相互的cross talk尚不致構成問題,不過CPU與tinning有可能會在無關係的信號線與bus line之間造成不良影響,所以必需避免bus line與其它信號線并行配線,而且bus line與其它信號線必需相隔1mm以上。 - 等長配線

clock的分配或是CPU之類的控制信號儘可能作等長配線,如果配線長度相差100m m,信號傳輸速度會產生0.6ns的差異。此外上述的直列終端電阻作50~100Ω調整,亦可獲得1ns skew的補正。 - 不可省略pass control

儘可能在各IC的電源端子設置pass control。 - 必需熟記的基本數據

micro strip line的信號速度

micro strip line的信號以每6ns前進1m。

pattern修正的幅寬

幅寬0.15mm的pattern,蝕刻後會降至0.10mm左右。

micro strip line的阻抗(impedance)

絕緣層的誘電率為4.8,絕緣層的厚度為0.4mm時,pattern幅寬為0.1mm的阻

抗(impedance)約為100Ω;pattern幅寬為0.7mm時,阻抗約為50Ω;絕緣層的厚度為0.2mm,pattern幅寬為0.1mm的阻抗約為80Ω。

cross talk與pattern的間隔/絕緣層厚度的關係

pattern間隔為1mm時的cross talk是間隔為0.15mm的1/10以下,pattern間隔超過1mm反而效果不彰。此外micro strip line的絕緣層厚度從1.5mm變成0.2mm時,cross talk可降至1/10以下。

配線容量

字pattern幅寬0.1mm,絕緣層厚度0.2mm的micro strip line配線容量為 0.3PF/cm。

pattern幅寬0.1mm,絕緣層厚度0.24mm的strip line配線容量為2.0pF/cm。

pattern幅寬0.1mm,pattern間隔為0.2mm的配線容量為0.3pF/CM。

pattern間隔為1mm的配線容量為0.01pF/CM。

自我阻抗(impedance)與相互阻抗

pattern幅寬0.1mm的自我阻抗為8~16mH/cm。

pattern間隔為0.2mm時,配線之間的相互阻抗為 6mH/cm。

[admin

via

研發互助社區 ]

高速數字電路板設計技術探索已經有3915次圍觀

http://cocdig.com/docs/show-post-44276.html