14.1. 簡介

14.2 SI 問題

14.2.1. 典型 SI 問題

14.2.2. SI產生的地方

14.2.3. 電氣封裝中的SI

14.3. SI 分析

14.3.1. 設計流程中的SI分析

14.3.2. SI 分析原則

14.4. 設計中的SI問題

14.4.1. 上升時間與SI之關係

14.4.2. 傳輸線效應、反射及串擾

14.4.3. 電地雜訊

14.5. 建模與模擬

14.5.1. 電磁建模方法

14.5.2. SI 分析工具

14.5.3. IBIS

14.6. SI 範例

* “This chapter is contributed by Raymond Y. Chen, Sigrity, Inc., Santa Clara, California. E-mail:chen@sigrity.com”

14.1.簡介

在高速數字設計的領域裡,信號完整性已經變成了一個關鍵的問題,給設計工程師帶來了越來越嚴峻的考驗。許多信號完整性問題本質上來說是電磁現象,和本書前面章節中討論的EMI/EMC 部分相關。本章我們將要討論典型的信號完整性問題及其成因,為什麼我們要理解它們以及我們如何來分析和解決這些問題。同時介紹幾個目前有效的信號完整性分析工具及當前的趨勢。

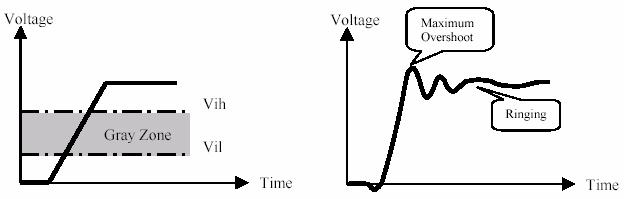

SI 在電子設計方面包括了兩層意思-時序和信號質量。信號抵達目的地的時間是否和期望的一樣?同時到達的情況如何?信號完整性分析的目的是保證可靠的高速數據傳輸。在一個數字設計中,信號從一個器件以邏輯電平1 或者0 的形式傳遞到另外一個器件,而邏輯的判斷實際上以一定的電平為參考的。在接收端的輸入門,參考值Vih 以上的電壓被認為是邏輯高電平,Vil 以下的被認為是邏輯低電平。圖14-1 表明在完美邏輯世界中理想電壓波形,圖14-2 表明的是實際系統中信號的情況。一連串1 和0 組成的複雜數據就構成了實際的連續電壓波形。接收器件為了得到二進位編碼信息需要對波形進行採樣。數據採樣過程通常是由時鐘信號的上升或者下降沿來觸發如圖14-3。從圖形中很清楚數據必須及時的到達接收端並且在接收器件開始鎖存的之前穩定為一個非模糊的邏輯狀態。任何數據的延遲或者波形的畸變將導致數據傳輸的失敗。想象一下一個如圖14-2 的信號波形,當信號採樣時,由於過量的振鈴在邏輯灰區域,導致邏輯電平不能被可靠的識別。

圖14-1 理想信號波形 圖14-2 實際信號波形

圖14-3 數據採樣過程和時序轉變

14.2 SI 問題

14.2.1 典型的SI 問題

時序是高速系統的一切。信號時序取決於信號傳播的物理長度引起的延遲。同時取決於抵達閥值時波形的形狀。信號波形畸變的原因可能有很多的不同原因。但是針對雜訊來說我們最關心的有以下3 個方面:

除了以上三種SI問題之外,還有其它的電磁兼容性或者電磁干擾(EMC/EMI)方面的問題也可能會導致信號波形的畸變。當SI問題發生或者滿足不了系統雜訊容限時-比如說開關接收端產生反射使得信號低於Vih電平或者高於Vil電平;或者靜態接收端的信號電平大於Vil最大值或者低於Vih最小值;電源/地電壓波動干擾鎖存數據,然後導致邏輯錯誤,數據丟失,誤碼甚至發生系統癱瘓。在系統建立或者樣機調試時對這些類型的雜訊錯誤做出判斷和解決都顯得尤其困難。但是如果在發生之前理解並解決這些問題將減少開發周期和降低成本[1]。在本章地後面部分,我們將進一步探討這些雜訊現象的物理行為,起因,分析和模擬的電氣模型,以及避免的方法。

14.2.2 SI問題產生的地方

由於信號在系統中的傳播由各種各樣的互連來完成,在源端,沿路或者在接收端產生的任何電氣衝擊都將對信號的時序和質量產生顯著的影響。在一個典型的數字系統環境下,來自晶元內部驅動器端的信號通過C4或者邦定線連接到晶元封裝(晶元封裝可以是單晶元或者是多晶元模塊)通過晶元封裝的焊球,信號進入PCB級。在這一級,典型的結構包括子卡,母板,或者是背板。然後信號繼續前進進入到系統的其它組件中,如ASIC晶元,存儲器模塊等。如圖14-4所示晶元封裝,印製電路板,以及電纜和連接器形成了電子封裝系統的各個級別。在系統中的每一級,都有典型的互連如金屬線,過孔,和電源地平面等,它們組成了信號連接的電氣路徑。封裝互連結構最終會影響到系統的信號質量。

圖14-4 IC封裝和PCB中出現的信號完整性挑戰

14.2.3 電氣封裝中的SI

高速,高密器件的技術趨勢使得封裝性能趨於極限。目前個人計算機的時鐘頻率已經達到了GHz。當信號上升時間低於200ps,信號的有效高頻分量超越了10GHz。這就使得互連和封裝必須能夠支持信號快速變化和寬頻,而在信號波形質量的下降仍然在可以接收的範圍之內。

同時晶元設計和製造工藝處於顯著革命之中:門長度,從60年代的50微米到現在的0.18微米,甚至期望在今後幾年突破0.1微米;片上時鐘每18個月翻一翻;門級固有延遲在指數下降,已經到達了幾個皮秒。然而,物理設計明顯相對滯后。目前的工藝,封裝互連延遲佔據了系統時序的主體,成為高速系統設計的瓶頸。封裝性能已經成為了限制系統整體性能的一個主要因素。

高性能亞微米處理器的出現,G兆位網路以及寬頻互連接入,要想可靠把高速數據傳輸到每一個電子系統必須要有高性能的封裝互連結構。在設計這些封裝(晶元和PCB)及其集成系統的時候,信號質量是需要考慮的一個最重要的因素。

[admin via 研發互助社區 ] 電地完整性、信號完整性分析導論已經有3489次圍觀

http://cocdig.com/docs/show-post-44236.html