IP核生成文件:(Xilinx/Altera 同)

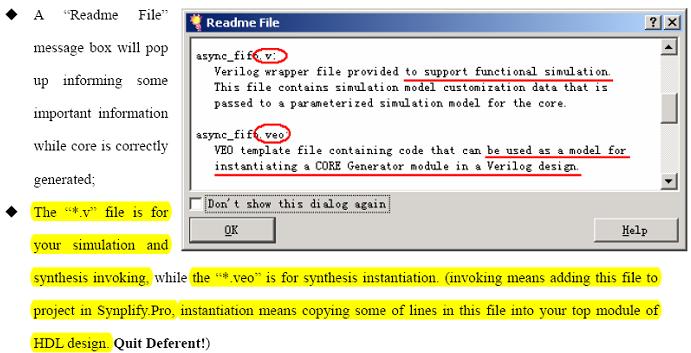

IP核生成器生成 ip 後有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則asyn_fifo.veo 給出了例化該核方式(或者在 Edit->Language Template->COREGEN 中找到verilog/VHDL 的例化方式)。asyn_fifo.v 是該核的行為模型,主要調用了 xilinx 行為模型庫的模塊,模擬時該文件也要加入工程。(在 ISE中點中該核,在對應的 processes 窗口中運行“ View Verilog Functional Model ”即可查看該 .v 文件)。如下圖所示。

1. 在 ISE 集成環境中模擬 IP核

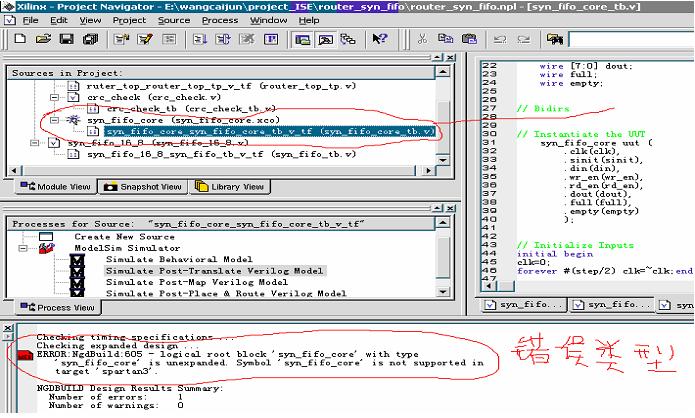

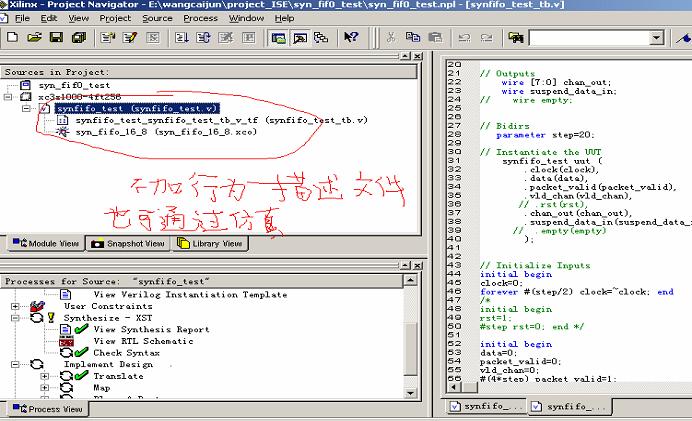

IP 核應該在新建的工程中進行模擬與例化;在原工程中可以例化使用,但好像不能直接對它加 testbench 後進行模擬。如下兩圖所示。

圖 1:直接在工程中對 ip核加 testbench 模擬時出錯

圖 2:新建工程單獨對 ip核模擬

2.在 modelsim中模擬 ip 核

a.在 modelsim中編譯庫(Xiliinx)

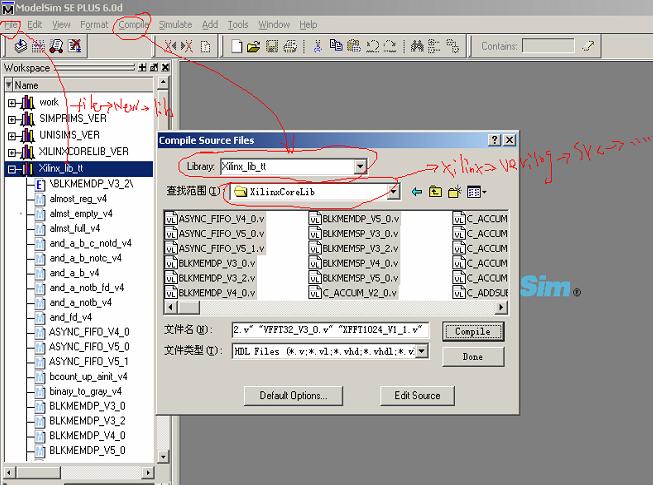

(1)在$Modeltech_6.0d/Xilinx_lib_tt下新建文件夾 Xilinx_lib($代表安裝盤符)

(2)打開 Modelsim->File->Change Diriectory,將路徑指向剛才新建的文件夾 Xilinx_lib,這樣 Xilinx 編譯的所有庫都將會在該文件夾下。

(3)編譯 Xilinx 庫。在$Xilinx->verilog->src 下有三個庫“simprims”,“unisims”和“xilinxcorelib”。在 modelsim 的 workpace 窗口 Library 屬性中點右鍵->new->library(或在File 菜單下 new->libary),輸入庫名(自定義)如 Xilinx_lib_tt,這樣在 workpace library 屬性下就可看到 Xilinx_lib_tt 了。

(4)modelsim 中選中 compile,在彈出的對話框中,library 選擇剛才新建的 xilinx_lib_tt,查找範圍為 xilinx 庫($Xilinx/verilog/src/),如 XilinxCoreLib,選中文件編譯即可。

b. 在 modelsim中載入已編譯的庫

當要在 modelsim 中模擬帶有 ip 核的設計時,需要載入對應公司的庫才能模擬。模擬Xilinx 公司ip 核時需要在原工程文件中加入 ip 核的行為描述文件(<核名>.v)。

如果工程文件直接包含在 xilinx“ XilinxCoreLib” library中,則可直接進行模擬。

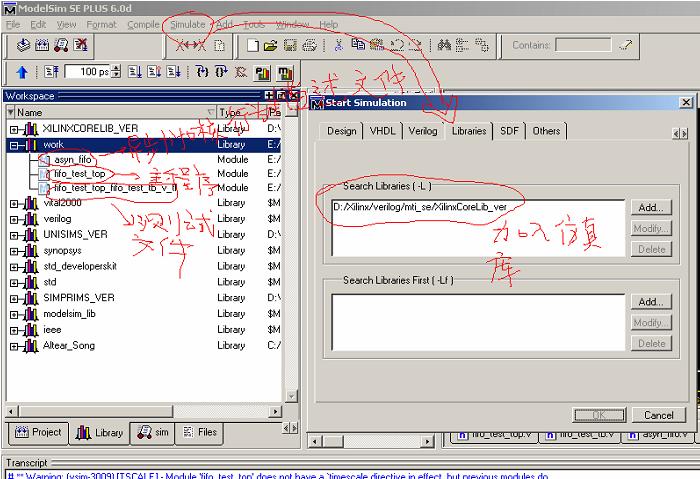

如果工程文件開始默認包含在“work”library 中,則需要在 Simulation->Start Simulation->library 中添加已編譯的庫,如圖示。這樣就可以對 ip 核進行模擬了。

aa.在 modelsim中編譯 Altera 的庫與 Xilinx方法一樣

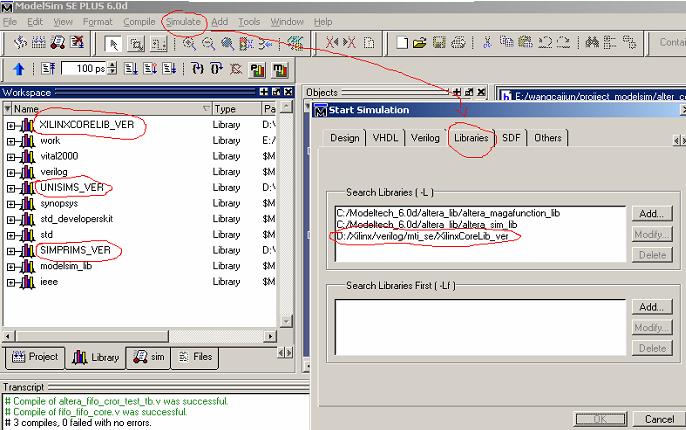

bb.在 modelsim中對 ip 核進行模擬,與 xilinx 一致;首先需要在 modelsim工程中加入設計文件,testbench 文件以及核的行為描述文件(<核名>.v);其次,自 File 菜單中更改庫路徑指向已編譯的 altera庫路徑(否則原先編譯的 altera 庫將變為不可用,unavailable),這

時原先編譯的庫將變為可用,然後在 Simulation->Start Simulation->library中添加庫路徑(同Xilinx,圖4,圖附 3)。

圖 3:編譯xilinx 庫

圖 4:加入庫進行核模擬

使用 modelsim 進行模擬,相對在 ISE 或 Quartus 中直接調用 modelsim,至少有三個好處:

附 A:在 ISE/Quartus中直接調用 modelsim。

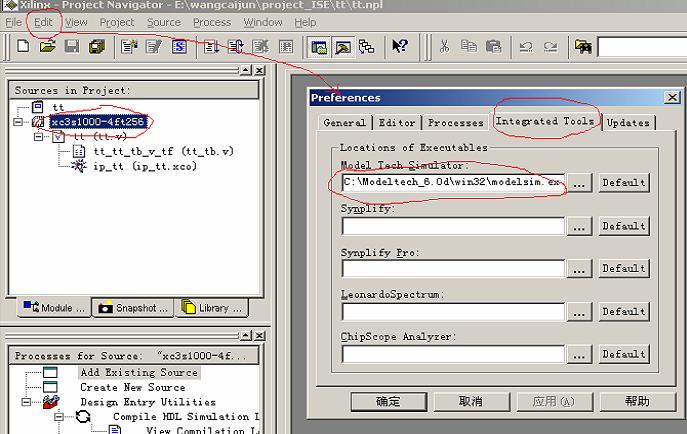

a.先安裝 ISE,再安裝 modelsim,則 modelsim會自動嵌入到 ISE 中去,如圖附 1。ISE集成環境下:Edit->Preferences->Integrated Tools可以設置常用的第三方模擬,綜合工具。

圖附 A1:ISE 中調用 modelsim

b.直接在 ISE 中編譯庫

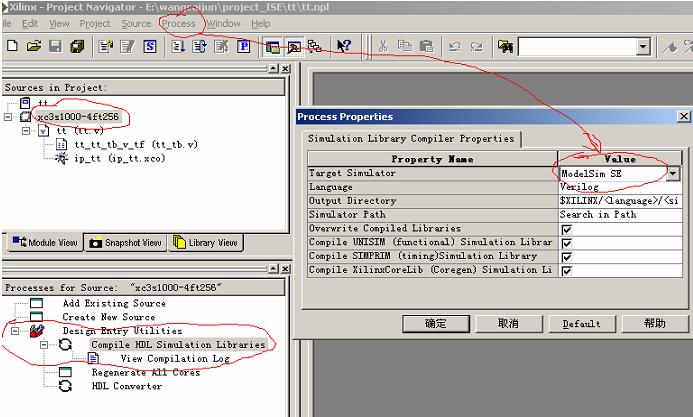

除了可以用前面介紹的方法自己編譯ISE的庫外,還可以在ISE環境下自動編譯庫,編譯完成之後將會自動嵌入到 modelsim的 libarary中去,非常方便。

編譯之前,首先把modelsim的屬性文件 modelsim.ini($Modeltech_6.0d/modelsim.ini)的“只讀”屬性去掉,否則每次都要重新編譯。然後在 ISE 環境下新建一個工程,選中晶元型號,在出現的 process 窗口中可以看到“Desin Entry Utilities”,展開它可以看到“Compile HDL Simulation Libraries”,雙擊它即可自動編譯 ISE 的庫(要確保 Process屬性窗口中“Target Simulator”正確設置為“Modelsim SE”,如圖附 2);編譯好的庫放在$Xilinx/Verilog/mti_se/ 下(在 modelsim中模擬 ip 核需添加庫時指向該路徑即可,如圖附 3)。

圖附 2:ISE中編譯庫

圖附 3:ISE中編譯庫后自動在 modelsim里載入

aa.在 Quartus 中設置第三方工具

在 Quartus 環境下:Assignment->EDA Tool Settings->….如圖附 3 所示,在“EDA Tool Settings”下拉框中選擇“Simulation”窗口,設置“Tool name”(如 Modelsim(verilog)),並選中下面的“Run this tool automatically after compliation”。這樣每次 Quartus 綜合完之後將會自動調用 modelsim模擬了。同時要注意,在“More Setting”中“command/macro file”應選為“None”,否則當你使用別的 testbench 時,調用將會出錯。

bb.在 Quartus 中自動編譯庫: 尚未發現有此方法,暫時只能由用戶自己編譯。

附 B:Xilinx/Altera 庫文件

a. 與 Xilinx 相關的庫有三個:

(編譯路徑:$Xilinx/Verilog/src/(XilinxCoreLib, unisims,simprims),編譯時可改名)

-L 表示模擬時需要的庫文件。(下面的命名方式可以使 Modelsim對庫進行準確映射)

Xilinxcorelib_ver 對應 Xilinx 提供的軟核的功能模擬庫;

Unisims_ver 對應使用 ECS所做的原理圖的功能模擬庫;

Simprims_ver 對應項目布局布線以後的時序模擬庫。

b. 與 Altera 相關的庫暫時只用到一個(Altera 的用的還不熟哦^_^):

(編譯路徑:$Quartus50/eda/sim_lib)

命名方式可以任意

[admin via 研發互助社區 ] 如何模擬IP核(建立modelsim模擬庫完整解析)已經有8648次圍觀

http://cocdig.com/docs/show-post-43274.html