前言

在製程進入深次微米世代之後,晶片(IC)設計的高複雜度及系統單晶片(SOC)設計方式興起。此一趨勢使得如何確保IC品質成?榻袢賬?猩杓拼右等嗽輩壞貌幻媼僦?卮罌翁狻>蔡?斃蚍治觶?tatic Timing Analysis簡稱STA)經由完整的分析方式判斷IC是否能夠在使用者指定的時序下正常工作,對確保IC品質之課題,提供一個不錯的解決方案。在「靜態時序分析(Static Timing Analysis)基礎及應用(上)」一文中筆者以簡單敘述及圖例說明的方式,對STA的基礎概念做了詳盡的說明。接下來,就讓我們藉由實際設計範例來?解STA在設計流程的應用。

設計範例說明

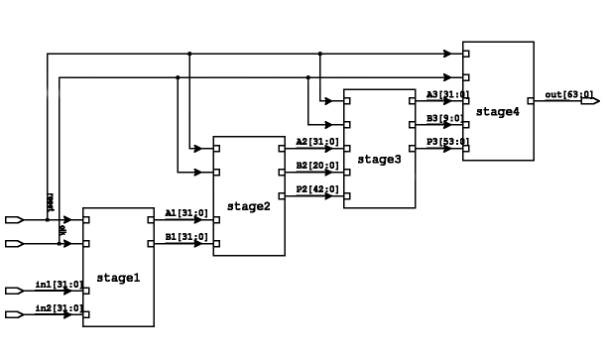

設計範例為一個32bit x 32bit的Pipeline乘法器,其架構如圖一所示。Pipeline共分3級,電路之輸出輸入端皆有暫存器儲存運算數值。

圖一

依據Cell-based設計的方式,首先以硬體描述語言設計圖一之電路。接下來實作此電路,進行合成(Synthesis)及布局與繞線(P&R)。並在實作的各步驟後進行靜態時序分析,確認時序規格是否滿足。實作及驗證所用到的軟體及設計資料庫如下所示:

在接下來的文章中,各位將會看到靜態時序分析在實作過程中的應用。藉由實際產生的數據?解在不同實做步驟上時序分析的差異。

時序限制(Timing Constraint)

要作靜態時序分析,首先要有時序限制。此設計範例的時序限制如下所述。(à后?檣瓚ㄊ斃螄拗浦?DC指令)

1 時脈規格(Clock Specification)

1.1 ?期:6ns à create_clock -name "MY_CLOCK" -period 6 -waveform {0 3} [get_ports {clk}]

1.2 Source Latency:1ns à set_clock_latency -source 1 [get_clocks {MY_CLOCK}]

1.3 Network Latency:1ns à set_clock_latency 1 [get_clocks {MY_CLOCK}]

1.4 Skew:0.5ns à set_clock_uncertainty 0.5 [get_clocks {MY_CLOCK}]

2 周邊狀況(Boundary Condition)

2.1 輸入延遲(Input Delay):1.2ns à set allin_except_CLK [remove_from_collection [all_inputs] [get_ports clk] ]

set_input_delay $I_DELAY -clock MY_CLOCK $allin_except_CLK

2.2 輸出延遲(Output Delay):1.2ns à set_output_delay $O_DELAY -clock MY_CLOCK [all_outputs]

2.3 輸出負載(Output Loading):0.5pF à set_load $O_LOAD 0.5 [all_outputs]

3 時序例外(Timing Exception):無

合成軟體之時序報告

當Synopsys Design Compiler將電路合成完畢后,執行下面指令可以?生時序報告:

report_timing -path full -delay max -max_paths 10 -input_pins \

-nets -transition_time -capacitance > timing_syn.txt

時序報告會儲存在timing_syn.txt此檔案中。在檔案的開頭不遠處,會列出此電路最有可能不符合時序規格的路徑(Critical Path)。例如:

Startpoint: S2/B2_reg_0_

(rising edge-triggered flip-flop clocked by MY_CLOCK)

Endpoint: S3/P3_reg_47_

(rising edge-triggered flip-flop clocked by MY_CLOCK)

Path Group: MY_CLOCK

Path Type: max

在這個例子中,Critical Path的起點Flip-Flop是第2個Pipeline Stage內的B2暫存器的第0個位元,終點Flip-Flop則是第3個Pipeline Stage內的P3暫存器的第47個位元(圖二)。

在Critical Path報告的下方會有Wire Load Model的資訊,此範例使用的是UMC18_Conservative Model。這個Model會以較悲觀的方式預估連線的延遲時間(Interconnect Delay)。

圖二

繼續往下檢視檔案,你會看到Critical Path的詳細時序資訊。例如:

Point Fanout Cap Trans Incr Path

-------------------------------------------------------------------------------

clock MY_CLOCK (rise edge) 0.00 0.00

clock network delay (ideal) 2.00 2.00

S2/B2_reg_0_/CK (DFFHQX4) 0.00 0.00 2.00r

S2/B2_reg_0_/Q (DFFHQX4) 0.16 0.30 2.30r

S2/n36 (net) 1 0.03 0.00 2.30r

S2/U10/A (BUFX20) 0.16 0.00 2.30r

S2/U10/Y (BUFX20) 0.23 0.21 2.51r

...

...

S3/add_106/U0_5_47/A (XNOR2X2) 0.18 0.00 7.74f

S3/add_106/U0_5_47/Y (XNOR2X2) 0.12 0.22 7.96f

S3/add_106/SUM[47] (net) 1 0.01 0.00 7.96f

S3/add_106/SUM[47] (stage3_DW01_add_54_0) 0.00 7.96f

S3/N94 (net) 0.01 0.00 7.96f

S3/P3_reg_47_/D (DFFTRXL) 0.12 0.00 7.96f

data arrival time 7.96

clock MY_CLOCK (rise edge) 6.00 6.00

clock network delay (ideal) 2.00 8.00

clock uncertainty -0.50 7.50

S3/P3_reg_47_/CK (DFFTRXL) 0.00 7.50r

library setup time -0.28 7.22

data required time 7.22

--------------------------------------------------------------------------------

data required time 7.22

data arrival time -7.96

--------------------------------------------------------------------------------

slack (VIOLATED) -0.74

先由左往右看,第一個直行Point標示出路徑中的節點,節點可以是元件的輸出入端點,也可以是元件間的連線(Net)。第二個直行Fanout標示節點推動的元件個數。第三個直行Cap標示出節點推動的負載。第四個直行Trans標示出節點上信號的轉換時間(Transition Time)。第五個直行Incr標示出節點造成的延遲時間。最後一個直行Path則是自路徑起點到到此節點?櫓溝淖苧映偈奔洹

再來我們由上往下檢視Critical Path的時序資訊。

clock network delay (ideal) 2.00 2.00

此處的2ns的clock network delay是由我們給定的時序限制計算而來的,因?槲頤歉??爍?ns的source latency及network latency,加起來共有2ns。

S2/B2_reg_0_/CK (DFFHQX4) 0.00 0.00 2.00 r

此行表示Critical Path的起點??2 Instance下的B2_reg_0_這個instance的CK端點。由於有2ns的network delay,所以時脈信號到達此節點的時間??ns(圖三)。至於0ns的Transition Time則是因?槲頤敲揮性謔甭齬娓裰卸ㄒ迤涫?擔?銑扇硤宓幕峒偕枋且桓?ns Transition Time的理想波形。最右邊的r是因?檎飧?lip-Flop是正緣觸發,所以以r表示。如果是f就是負緣觸發。

圖三

S2/B2_reg_0_/Q (DFFHQX4) 0.16 0.30 2.30 r

接著信號自起點開始向終點傳遞,這一行表示路徑起點的Flip-Flop從CK端點到Q端點的時間延遲??.3ns,且在此節點的Transition Time??.16ns。所以信號到達此節點的時間??+0.3=2.3ns(圖四)。最右邊顯示r是因??端點從0變化到1時的延遲時間比1變化到0時的延遲時間還長,如果狀況相反的話,最右邊會標示f。以上數值是由元件庫(Cell Library)?的時序表(Timing Table)查出來的,其計算的方式請參照「靜態時序分析(Static Timing Analysis)基礎及應用(上)」。

S2/n36 (net) 1 0.03 0.00 2.30 r

S2/U10/A (BUFX20) 0.16 0.00 2.30 r

這兩行和上一行最右邊的Path欄位都一樣,這是因?櫧涫鄧?鞘峭?桓黿詰悖??孕藕諾醬鍤奔湟謊?W邢傅畝琳噠饈焙蚩贍芑嵊懈鮃晌剩?lip-Flop的Q輸出端和後面Buffer的輸入端A信號到達時間應該有一個連線延遲(Interconnect Delay)的差距吧?想法上是沒錯,但因??esign Compiler這個合成器將連線延遲的時間合?愕皆??映伲?ell Dealy)的時間內計算,所以從時序報告中看不到延遲時間的資訊。也就是說,如果Point欄是net的話,各位只需去檢視Fanout和Cap欄位即可。S2/n36這個net只有推動一個Buffer,其Fanout??。負載則是Buffer的輸入負載和預估連線負載的總和,其值??.03pF。

圖四

[admin via 研發互助社區 ] 靜態時序分析(Static Timing Analysis)基礎及應用(下)已經有16774次圍觀

http://cocdig.com/docs/show-post-43261.html