第一章 Modelsim編譯Xilinx庫

本章介紹如何編譯HDL必須的Xilinx庫和結構模擬。

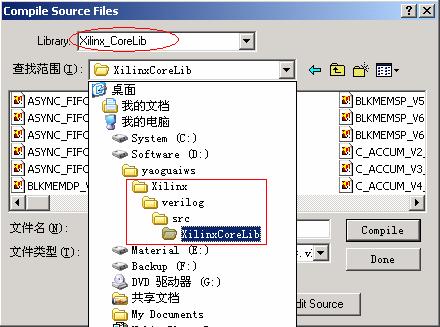

創建將被編譯庫的目錄

在編譯庫之前,最好先建立一個目錄(事實上必須建立一個目錄),步驟如下。(假設Modelsim的安裝目錄是“$Modeltech_6.0”,ISE的安裝目錄是“$Xilinx”)

二、調用Xilinx CORE-Generator

當需要在設計中生成參數化和免費的IP內核(黑箱子)時,無論是通過原理圖方式還是HDL方式,CORE-Generator都是一個非常有用的程序。

利用CORE-Generator創建一個IP核

利用Xilinx提供的CORE-Generator來生成IP核是非常簡單的。內核是全參數化的,這就意味著你只需要在空白處填入幾個數字和參數,然後程序就會自動產生一個你所需要的

內核。(有些內核是全免費的,有些則沒有這麼慷慨)

利用CORE-Generator來生成IP核的步驟如下:

第三章 使用Synplify.Pro綜合HDL和內核

綜合是將設計好的HDL代碼,圖形代碼和原理圖轉變成邏輯單元的技術。同與硬體執行和物理布線非常接近的物理綜合相比,邏輯綜合是更高層次的綜合技術。

利用Synplify.Pro進行邏輯綜合

Synplify.Pro對於大容量低價格的Xilinx Spartan系列FPGA而言,有著非常好的綜合能力。

具體步驟如下:

[admin via 研發互助社區 ] Modelsim、Synplify.Pro、ISE設計全流程已經有2814次圍觀

http://cocdig.com/docs/show-post-43126.html