作者:chenhongyi

軟體要求:ModelSimSE、Synplify Pro、Quartus II

適用人群:初學者

源 代 碼:mux4_to_1.v

工作內容:

1、設計一個多路選擇器,利用ModelSimSE做功能模擬;

2、利用Synplify Pro進行綜合,生成xxx.vqm文件;

3、利用Quartus II導入xxx.vqm進行自動布局布線,並生成xxx.vo(Verilog

4、利用ModelSimSE做后模擬,看是否滿足要求。

註:

1. 模擬器(Simulator)是用來模擬電路的波形。

2. 綜合工具(Synthesizer)的功能是將HDL轉換成由電路所組成的Netlist。

3. 一般而言,在電路設計的模擬上可分為Pre-Sim 和Post-Sim。Pre-Sim 是針而Post-Sim則是針對綜合過且做完成了Auto Place and Route(APR)的電路進行模擬,以確保所設計的電路實現在FPGA上時,與Pre-Sim 的功能一樣。

1、前模擬(Pre-Sim)

步驟一:打開ModelSimSE,然後建立一個Project;

※建立Project的方式為點選File → New → Project…;

※設定Project Name 與Project location,按OK 即可建立Project。

步驟二:新增設計文檔或加入文檔。

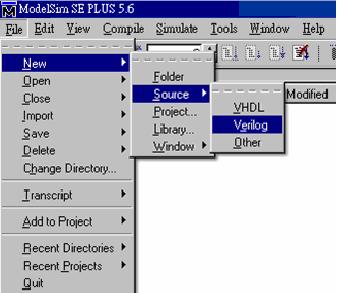

※新增文檔的方式為點選File → New → Source → Verilog,然後對文檔進行編輯並儲存為xxx.v;

※ 加入文檔的方式為點選File → Add to Project → File...,然後點選xxx.v;

步驟三:編譯(Compile)。

※編譯文檔的方式為點選Compile → Compile All,即可編譯所有的文檔。

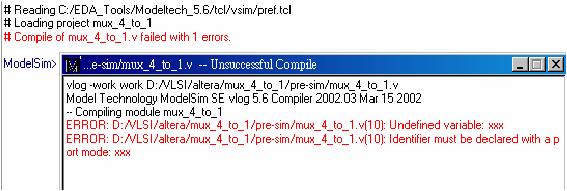

※如果編譯時發生錯誤,在顯示錯誤的地方(紅字)點兩下,即可跳到錯誤。

步驟四:新增或加入測試平台(Testbench)。

※當設計完電路后,為了確定所設計的電路是否符合要求,我們會寫一個測 試平台(Testbench);

※ 新增或加入測試平台,然後編譯它。

步驟五:模擬(Simulate)。

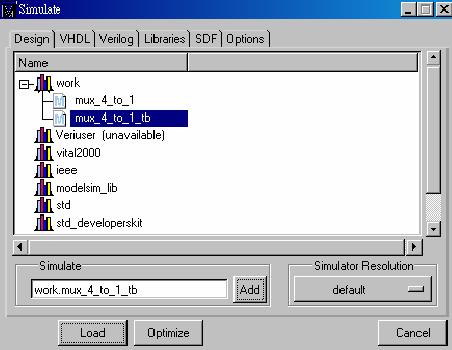

※模擬的方式為點選Simulate → Simulate…;

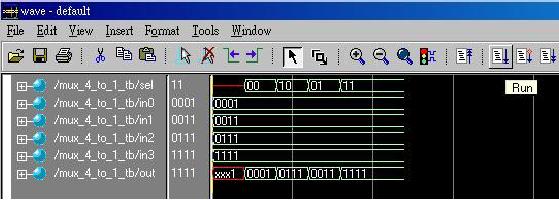

※打開Design裡面的work,然後點選mux_4_to_1_tb 並Add 它,最後按Load 即可跳到模擬窗口。

步驟六:加入信號線。

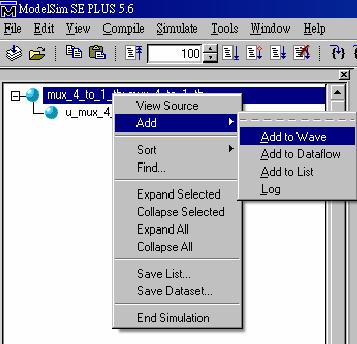

※ 在窗口上按右鍵,然後點選Add → Add to Wave;

步驟七:看波形。

※在工具列上按Run,然後就會顯示波形;

※慢慢看波形吧,沒有波形就沒有真相!

以上就是使用ModelSim做Pre-Sim的基本流程,在此要特彆強調的是,ModelSim所有的功能並不僅僅於此,如果你想要了解更多的話,一切都要靠自己花時間去問去試,只有努力的人才能有豐富的收穫,加油!

[admin via 研發互助社區 ] ModelSim+Synplify+Quartus的Altera FPGA的模擬與驗證已經有8668次圍觀

http://cocdig.com/docs/show-post-42966.html