1. 實驗要求及目的:

這次的實驗我們要做的是流水燈,顧名思義就是要LED象水一樣的點亮(好像有點不怎麼顧名思義啊),這樣說吧,就是先單獨點亮第一個,然後點亮第二個(這個時候有兩個燈亮了),然後……

這一個實驗主要教會大家一個比較方便的鎖定引腳的辦法,另外就是使用移位運算符。

使用軟體:Quartus II 5.0。

2. 硬體原理圖:

這個是我自己製作的開發板上的LED的原理圖,一共有8個,IO和別的共用的,使用八個LED的時候板上的JP1和JP5全部戴上短接帽,JP2則空出。如果要點亮這些LED,只需要把與其相連接的FPGA管腳輸出低電平“0”就可以實現這個功能了。(我焊板子的時候把LED1弄壞了,不能用。)

LED管腳對應的情況如下:

D1------PIN_97

D2------PIN_94

D3------PIN_91

D4------PIN_84

D5------PIN_82

D6------PIN_78

D7------PIN_76

D8------PIN_74

另外,本實驗需要用到時鐘計數,時鐘對應的引腳為PIN_16。

本文均採用輸出“0”點亮的模式,以下就不再另外再說明了。

——這幾句話我直接抄襲上第一個實驗的了,因為是一樣的。

3. 程序設計

(1)設計分析:我們要求這次8個燈流水一樣的點亮(如果實在我講解的不清楚,可以先看看最後的實驗錄像)。

具體分析一下,我們需要每個1秒鐘的時間點亮一個燈,從D1開始,然後點亮D2(這個時候點亮了D1和D2),依此類推,直到點亮八個燈,然後熄滅;然後又從頭開始……

FPGA輸出的數據就應該首先是11111110,隔1秒鐘變成11111100……一直變化到00000000,這就可以實現流水燈了。

基本上看明白了吧,那就來看看源程序吧。

(2)源程序 exp2.v

程序代碼:

// Light 8 LED (water light)

// Designed By Smokingfish @ www.51FPGA.com zhiyuh@163.com

module exp3(LED,CLK,reset);

output[7:0] LED;

input CLK,reset;

reg [7:0] LED;

reg [24:0] counter;

//initial

//LED=8'b11111111;

always@(posedge CLK) //

begin

counter<=counter+1; //

if(counter==25'b1_0111_1101_0111_1000_0100_0000) //25M

// 1_0111_1101_0111_1000_0100_0000

begin

LED<=LED<<1;

counter<=0;

if(LED==8'b0000000)

LED<=8'b11111111;

end

end

endmodule

這裡我們運用了“<<“這個移位運算符,至於這個運算符的用法,你可以參看夏老師的書31頁,有比較詳細的說明。當然,你也可以採用case語句,方法不一樣,只要實現的功能一致就行——你可以比較一下兩種方法代碼的長度以及編譯后佔用的資源情況,看看有什麼不一樣的地方。在這裡我就不多講語法了,我著重講的是實踐。

中間有兩行註釋,這個是周立功那本書里寫的(我參考了他的設計,呵呵)。我認為這兩句是不能綜合的,只能用於測試模塊,相關的說明可以參看Verilog HDL的語法說明。所以我認為他書里寫錯了,於是我向夏老師求證,他也認同了我的看法。所以有時候還是不能盡信書。一般情況下,如果需要對寄存器進行初始化,需要加入reset信號。如果一定不能用 reset信號,對FPGA來說綜合后的電路應該上電就能複位。

4. 實驗步驟

(1)打開Quartus II軟體,進入集成開發環境,點擊File->New project wizard..新建工程項目exp3,直接點擊Finish。

(2)點擊File->New..在該項目下新建Verilog HDL源程序文件exp3.v,輸入上面的源程序代碼並保存。

(3)選擇所用的FPGA器件----EP1C3T144C8,以及進行一些配置。

選擇配置器件,如果要下載程序到EPCS1的話。

選擇不需要使用的IO功能。選擇As inputs,tri-stated。

點擊兩次ok,回到主界面。

(4)為工程項目鎖定引腳:(這裡教大家一個新的辦法,比較方便快捷)

首先建立一個TCL Script文件:點File->New…選擇Other Files選項卡裡面的Tcl Script File,如下圖:

點擊ok,輸入下面的代碼:

程序代碼:

#Pin_Setup.tcl

# Setup pin setting

set_global_assignment -name RESERVE_ALL_UNUSED_PINS "AS INPUT TRI-STATED"

set_global_assignment -name ENABLE_INIT_DONE_OUTPUT ON

set_location_assignment PIN_16 -to CLK

set_location_assignment PIN_97 -to LED\[0\]

set_location_assignment PIN_94 -to LED\[1\]

set_location_assignment PIN_91 -to LED\[2\]

set_location_assignment PIN_84 -to LED\[3\]

set_location_assignment PIN_82 -to LED\[4\]

set_location_assignment PIN_78 -to LED\[5\]

set_location_assignment PIN_76 -to LED\[6\]

set_location_assignment PIN_74 -to LED\[7\]

比較簡單的代碼,簡單的講解一下,第一行和第二行是註釋,第四行的意思是設置不用的引腳為三態輸入(這個前面其實我們已經做過了),第五行的意思是打開INIT_DONE輸出。後面的幾行分別是鎖定CLK和8個LED的引腳。(如果想應用更多的東東,可以自己查閱一下相關的文檔,我這裡就是讓你知道有這麼一個東西,會用了就行,至於提高就是自己的事情咯,呵呵)。

保存這個文檔(Pin_Setup.tcl),軟體會自動把你加到項目裡面(但是你關閉項目之後第二次打開又會沒有,我也不知道是為什麼,奇怪)。

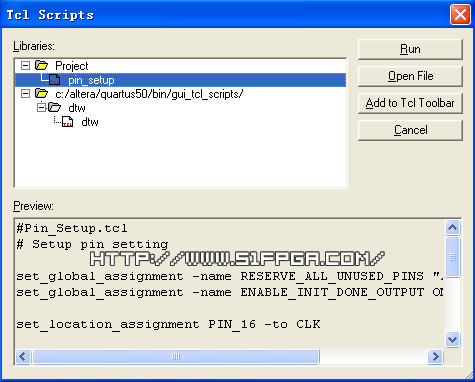

然後點Tools->TCL Scripts…,出現下面這個界面:

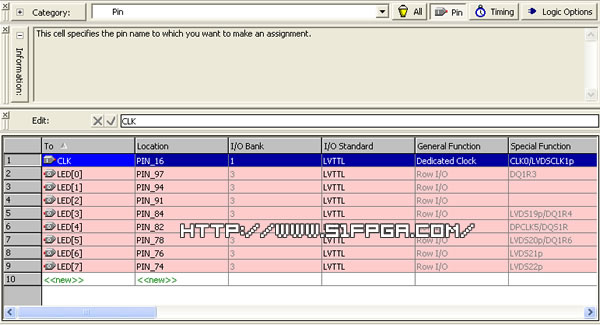

選中你剛才建好的Tcl文件,點擊Run。這個時候你可以在Quartus II軟體下方的Message框裡面看到這麼一個信息:Info: Successfully loaded and ran Tcl Script File "F:\VerilogHDL Exp\exp3\pin_setup.tcl""。你也可以確認一下是否正確分配了,分配的情況如下圖:

怎麼樣,是不是快多了,不用點那麼多次滑鼠(滑鼠的壽命又可以增加一點了,哈哈)。這個文件你可以適當修改用於別的項目,如果引腳一樣也可以直接在別的項目中加入這個文件然後執行,可以省很多事情。如果只有幾個引腳,一個一個鎖定還就罷了,要是一個工程用到上百個引腳,那就要死人了。

其實Tcl腳本文件不僅僅是可以鎖定引腳,還有其他很多的功能,比如(抄的是Quartus的使用手冊):

工程與分配功能

器件功能

高級器件功能

流程功能

時序功能

高級時序功能

Simulator 功能

報告功能

時序報告功能

反標功能

LogicLock 功能

Chip Editor 功能

其它功能

其他的功能我就不一一講了,你可以參考以下的文檔:

Quartus II Help 中的“Overview: Using Tcl Scripting” 和“API Functions for Tcl”以及Altera的Quartus II Handbook 第2 卷“Tcl Scripting”:http://www.altera.com.cn/literature/hb/qts/qts_qii52003.pdf,還有就是Quartus II Scripting Reference Manual:http://www.altera.com.cn/literatur ... #083;criptRefMnl.pdf

(5)編譯工程項目:點擊Processing->Start Compilation。

(6)模擬: 自己建立模擬文件檢查自己的設計是否正確。

(7)下載目標文件到板子上:點擊Tools->Programmer,選中Jtag模式,並且選中目標文件,然後點Start。

很快就完成了第三個實驗,是不是覺得有所收穫?沒有?——那我就太失敗咯。

你也可以試著別的花樣來點亮LED,比如,只有一個燈亮的流水燈,亮過去之後又亮回來等等,就看你的想象力了,通過自己寫程序更能有成就感,而且還能把書本的知識用到實際中,何樂而不為呢?是吧?

[admin via 研發互助社區 ] FPGA/CPLD實驗教程三(流水燈)已經有11710次圍觀

http://cocdig.com/docs/show-post-43361.html