在現代數字系統中,FPGA(現場可編程門陣列)以計算機為開發平台,經過設計輸入、模擬、測試和校驗,直至達到預期結果。本文使用MathWorks公司的MATLAB軟體和Altera公司的FPGA開發軟體Quartus II進行FIR濾波器的設計模擬,並給出了設計的一般步驟。該方法能夠直觀地檢驗濾波器的設計效果,提高設計效率,縮短設計周期。

1 FIR濾波器原理

1.1 FIR濾波器基本結構

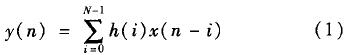

FIR濾波器的數學表達式為 :

式中:N為FIR濾波器的抽頭數;x(n)為第n時刻的輸入樣本;h(i)為FIR濾波器第i級抽頭係數。

普通的直接型FIR濾波器結構如圖1所示。

在自適應處理、數據通信等領域中往往要求信號在傳輸過程中不能有明顯的相位失真,FIR濾波器可以做到線性相位滿足此要求。FIR濾波器實質上是一個分節的延遲線,把每一節的輸出加權累加,得到濾波器的輸出。對於FIR濾波器的單位脈衝響應h(i)只要滿足以下2個條件之一,則為線性相位濾波器。

線性相位的FIR濾波器具有中心對稱的特性,其對稱中心在N/2處。

1.2 窗函數設計方法

FIR濾波器的設計方法有窗函數法、頻率取樣法和最優化設計法。其中窗函數法是設計FIR濾波器最簡單有效的方法,也是最常用的方法。在本設計中,所用到的濾波器的係數都是藉助於窗函數法完成的。窗函數設計法是一種通過截短和計權的方法使無限長非因果序列成為有限長脈衝響應序列的設計方法。利用加窗函數進行截斷和平滑,以實現一個物理可實現且具有線性相位的FIR濾波器的設計目的。

FIR濾波器的窗函數法設計過程為:

式中:Hd(ejΩ)為逼近的理想濾波器頻率響應;hd(k)為理想濾波器的單位脈衝響應,是無限長序列。

為獲取實際應用的FIR濾波,需將hd(k)截斷,用有限長的h(k)近似表示,用窗函數可以避免吉布斯現象h(k)=hd(k)ω(k),最後得到實際FIR濾波的頻率響應H(ejΩ)。

設計常用的窗函數有矩形窗、漢寧窗、海明窗、凱撒窗等。凱撒窗是一種適應性較強的窗,可同時調整主瓣寬度和旁瓣電平,所以本設計選擇凱撒窗實現。

1.3 FPGA設計中的流水線原則

在FPGA設計中,為提高系統的運行速度,而將指令分為幾個子操作,每個子操作由不同的單元完成,這樣,每一級的電路結構得到簡化,從而減少輸入到輸出間的電路延時,在較小的時鐘周期內就能夠完成這一級的電路功能。在下一個時鐘周期到來時,將前一級的結果鎖存為該級電路的輸人,這樣逐級鎖存,由最後一級完成最終結果的輸出。也就是說,流水線技術是將待處理的任務分解為相互有關而又相互獨立、可以順序執行的子任務來逐步實現。本設計在處理加法器時,利用對稱和流水線技術來提高濾波器的性能。

2 基於計算機輔助的FIR濾波器設計流程

隨著DSP技術在FPGA上的應用越來越廣泛,FPGA製造商相繼推出了一些可以快速簡單進行DSP設計的輔助性軟體,利用這些軟體的結合可以簡化FIR濾波器設計。本設計將常用的MATLAB軟體和FPGA的設計軟體Quartus II結合起來模擬。其設計流程的步驟如下。

1)在MATLAB中進行模擬設計和修改

設計指標為:採樣頻率1000 Hz,f1=314 Hz,f2=417 Hz,阻帶衰減40 dB。通過參數指標確定所需的階數和參數值,部分程序如下:

wp=0.2*pi; //通帶截止頻率

W8=0.3*pi; //阻帶截止頻率

As=40; //最小阻帶衰減

tr_width=ws-wp; //帶寬

M=ceil((As-7.95)/(14.36*tr-width); //按凱撒窗計算濾波器長度

disp(['order',num2str(M)]);

n=[0:1:M-1];

%beta=0.1102*(As-8.7); //計算beta值(As>50)

beta=0.5842*(A8-21)^0.4+0.07886*(As-21); //(21

<As<50),beta=3.3953

求出窗函數:

w_kai=(kaiser(M,beta))';//求凱撒窗函數

求理想和實際脈衝響應:

hd=ideal_lp(wc,M); //理想脈衝

h=hd.*w_kai; //凱撒窗下實際脈衝

由圖2、圖3驗證技術指標。

如果不滿足,則要改變帶寬,或改變窗形狀重新計算。現在由圖可見,滿足設計要求。

2)利用Simulink檢驗濾波效果

Simulink是MATLAB中一個專門用於對動態系統進行建模、模擬和分析的軟體包。通過調用模塊,可以構成模擬數字濾波器特性的結構框圖。輸人低頻10 Hz和高頻600 Hz的兩個信號,利用所設計的濾波器進行濾波。建立模擬電路結構,導入前面所設計的FIR濾波器,如圖4所示。

通過輸入(圖5(a))、輸出波形(圖5(b))的比較可看出,該FIR濾波器可以將高頻部分有效的濾除。

3)Quartus II設計及模擬

對MATLAB信號處理工具箱產生的濾波器模型及係數,用Quartus II進行設計模擬。Quartus II軟體是Altera公司主推的FPGA設計軟體,是集設計輸入、編譯、綜合、模擬、布線、下載於一體的設計軟體。由於MATLAB產生的濾波器係數是小數,將其轉換為12位二進位係數使用。限於篇幅,採用採樣頻率 =5 MHz,截止頻率fc=1.5 MHz,階數15,凱撒窗的設計指標。首先建一個block diagram文件通過功能模塊的搭建進行濾波器的設計,通過編譯綜合功能對生成的文件進行編譯和綜合,然後生成的頂層模塊,見圖6。

由MATLAB產生的FIR數字濾波器的係數如下:

h[0]=h[15]=0.039907834316444589

h[0]=h[15]=81D=000001010001=51H

h[1]=h[14]=-0.014451669844537473

h[1]=h[14]= -29 D = -000000011101=FE3H

h[2]=h[13]=-0.045307614673700439

h[2]=h[13]=-92 D = -000001011100=FA4H

h[3]=h[12]=0.05598422134210561

h[3]=h[12]=114 D =000001110010=72H

h[4]=h[11]=0.027733961872000723

h[4]=h[11]=56 D =000000111000=38H

h[5]=h[10]=-0.12646776014151861

h[5]=h[10]=-259 D = -000100000011=EFDH

h[6]=h[9]=0.065416521018384063

h[6]=h[9]=133 D =000010000101=85H

h[7]=h[8]=0.51489745091333106

h[7]=h[8]=1054 D =010000011110=41EH

在設計中採用流水線來提高有效的乘法器速度,該部分的VHDL代碼如下:

t1<=tap(0)+tap(15);

t2<=tap(1)+tap(14);

……

t8<=tap(7)+tap(8);

t9< = -t2:

t10< = -t3:

……

y<=t1+t9+……+t8

通過Quanus II的波形模擬功能,對輸入輸出進行波形模擬,對其結果進行定量分析。通過時序分析和功能分析結果,對設計進行進一步的完善,在模擬中,x為輸入信號,依次為1,2,4,10,12,得到的輸出結果如圖7所示。經驗證,模擬結果與實際運算結果一致。

3 結束語

本文綜合介紹了基於FPGA軟體Quartus II和MATLAB的FIR濾波器的設計模擬,將兩大軟體綜合運用后大大縮減了設計研發的時間,在演算法結構上利用了流水線等優化方式。在實際應用中,可以通過對濾波器參數的修改,很容易地實現其他各種濾波器的設計,具有一定的工程設計參考價值。

[admin via 研發互助社區 ] 基於MATLAB和Quartus II的FIR濾波器設計與模擬已經有4487次圍觀

http://cocdig.com/docs/show-post-43045.html