在視頻處理電路中使用Philips公司提供的可編程視頻輸入處理晶元SAA7111,大大降低了視頻輸入處理部分的設計難度,減小了電路板的製作尺寸,因此,它被廣泛應用於視頻桌面系統、圖像多媒體、數字電視、圖像處理和視頻電話等領域。而使用SAA7111的前提是首先實現對SAA7111的初始化,利用DSP或者單片機對SAA7111進行初始化已有報道。本文在簡單介紹I2C匯流排和SAA7111晶元的基礎上,重點介紹使用FPGA(現場可編程門陣列)模擬I2C(Inter-Integrated Circuit)匯流排介面對SAA7111進行初始化。

1 I2C匯流排技術簡介

I2C匯流排是一種由SDA(串列數據線)和SCL(串列時鐘線)組成的串列匯流排,它利用這兩根匯流排在MCU(微控制單元)與被控IC之間進行雙向數據傳送,各種被控電路均並聯在這條匯流排上。當匯流排備用時,兩根線都是高電平,只有當匯流排關閉時,SCL才轉變為低電平。在標準模式下,I2C匯流排的數據傳輸速度可達100 kbit/s,在高速模式下則可達400 kbit/s。由於在I2C匯流排上每傳輸一位數據都有1個時鐘脈衝相對應,所以,I2C匯流排的時鐘周期一般在2.5 s~10 s之間。

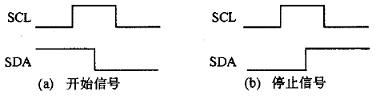

I2C匯流排為同步傳輸匯流排,其中與數據傳輸有關的信號有開始信號、停止信號、應答信號和位傳輸等4種類型。開始信號是在SCL為高電平期間,SDA出現由高電平向低電平的變化,由此啟動I2C匯流排,如圖1(a)所示。停止信號是在SCL為高電平期間,SDA出現由低電平向高電平的變化,它意味著即將停止I2C匯流排的數據傳輸,如圖1(b)所示。應答信號是指接收數據的IC在接收到發送方發送的8 bit數據后,應向發送數據的IC發出特定的低電平脈衝,表示已經完成本次數據的接收。數據位傳輸是在I2C匯流排啟動后或應答信號后的第1~8個時鐘脈衝對應於1個位元組的8個bit位的數據傳輸。SCL在高電平期間,數據串列傳輸;SCL在低電平期間,容許SDA上的電平發生轉換,為數據發送做準備。

圖1 I2C匯流排開始信號和停止信號

I2C匯流排在進行數據傳輸時,每一幀數據均為1個位元組,並且按照由高到低的順序發送1個位元組的8個bit。對於每個bit數據的傳輸,要求在時鐘信號為高電平期間,數據線上的數據必須保持穩定的邏輯電平狀態。只有在時鐘線為低電平時,才允許數據線上的電平狀態發生變化。另外,在啟動I2C匯流排后,傳輸的位元組數沒有限制,只要求每傳輸一個位元組,對方回應一個應答信號。

I2C匯流排的工作方式分為多主工作方式和單主工作方式。其中,在單主方式下,I2C匯流排上只有1個主器件成為主節點,該節點會永遠佔用I2C匯流排,而不會出現匯流排競爭的現象。在這種情況下,主器件若沒有I2C匯流排介面,就可以利用其IO來模擬I2C匯流排介面。在視頻採集系統中,採用的就是單主工作方式,FPGA為I2C匯流排的主節點。

2 SAA7111晶元簡介

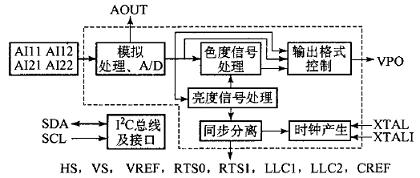

SAA7111是一款功能強大的模擬前端和數字視頻解碼器,常應用在嵌入式視頻應用的高度集成的電路中。內部包含兩路模擬處理通道,能實現視頻源的選擇、抗混疊濾波、A/D轉換、自動嵌位、自動增益控制、時鐘產生、多制式解碼以及亮度、對比度和飽和度的控制,從而將PAL、NTSC等不同制式的模擬複合視頻數據解碼成亮度、色度和相關同步的數字信號,而這些功能是依靠外部控制器對它內部寄存器的設置來實現的,本系統中就是利用FPGA實現對它內部寄存器的設置。SAA7111原理框圖如圖2所示。

圖2 SAA7111功能方框圖

工作時,模擬視頻圖像從SAA7111的4個輸入埠(AI11,AI12,AI21,AI22)中的一個埠輸入,經模擬處理后,一路通過緩衝器從模擬輸出端(AOUT)輸出用於監視,另一路經A/D后產生數字色度信號、亮度信號,分別進行亮度信號處理、色度信號處理。亮度信號處理的結果,一路送到色度信號處理器進行綜合處理,產生Y、U、V信號,經格式化后從VPO輸出,輸出的信號格式有422YUV或CCIR-656(8位)等;另一路進入同步分離器,經數字PLL,產生相應的行、場同步信號HS、VS及像素時鐘信號LLC和LLC2等信號,這些信號是實現視頻數據採集的依據。

3 SAA7111初始化的FPGA設計

在視頻處理系統中,SAA7111是視頻的輸入處理部分,主要實現模擬輸入視頻信號的數字化;但在它工作之前,FPGA應通過SAA7111的I2C匯流排介面對其進行初始化。在SAA7111正常工作后,FPGA再根據SAA7111輸出的行、場信號和像素時鐘信號,實現視頻的數字採集,並將採集的數據傳輸到後續的處理晶元中。關於SAA7111和外圍器件的詳細連接可參考SAA7111的晶元資料。SAA7111和FPGA的連接圖如圖3所示。

圖3 SAA7111和FPGA的連接

FPGA對SAA7111進行初始化,必須解決以下幾個問題:首先是產生I2C匯流排的時鐘信號;其次是實現I2C匯流排的開始信號、停止信號、位傳輸信號和判斷應答信號;再次是要確定SAA7111不同寄存器的設置數據。

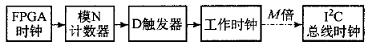

3.1 I2C匯流排時鐘的產生

一般情況下,FPGA的時鐘頻率較高,常為幾十MHz,而I2C匯流排的時鐘頻率為幾百kHz,用圖4的方式可藉助於FPGA的時鐘獲得I2C匯流排的時鐘。需要說明的是,圖中工作時鐘的頻率應為I2C匯流排時鐘頻率的M倍。這是因為系統中的任何一個I2C匯流排上的信號都是用M個工作時鐘的周期來完成,而D觸發器則是為了確保工作時鐘的占空比為50%而設計的。

圖4 12C匯流排時鐘產生圖

假設FPGA時鐘為50 MHz,I2C匯流排時鐘為200 kHz,M為8,則工作時鐘為1.6 MHz,再考慮到D觸發器相當於2分頻,則

N= 50MHz/(200 kHz×8×2) = 16

3.2 關鍵信號的產生和傳輸

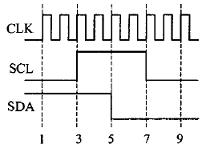

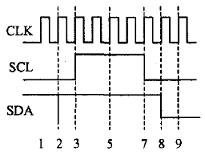

根據前面對I2C匯流排開始信號的討論,再結合3.1節的設計將利用8個工作時鐘產生一個I2C匯流排信號,很容易設計出I2C匯流排的開始信號。即規定:第1個脈衝上升沿到第3個脈衝上升沿之間,SCL為低、SDA為高;第3個脈衝上升沿到第5個脈衝上升沿之間,SCL為高、SDA為高;第5個脈衝上升沿到第7個脈衝上升沿之間,SCL為高、SDA為低;第7個脈衝上升沿到第9個脈衝上升沿之間,SCL為低、SDA為低。這樣經過8個脈衝周期,就可產生一個開始信號。具體如圖5所示。

圖5 I2C匯流排開始信號設計時序

相應的VHDL源程序代碼如下(假設為S1狀態)

if clk'event and clk='1' then

case cnt is

when 0|1 scl<='0';sda<='1';cnt:=cnt+1;

when 2|3 scl<='1';sda<='1';cnt:=cnt+1;

when 4|5 scl<='1';sda<='0';cnt:=cnt+1;

when 6 scl<='0';sda<='0';ent:=ent+1;

when 7 cnt:=0;tempstate<=S2;

when others=>tmpstate<=S0;

end case;

end if;

其中:cnt為工作時鐘clk的計數器變數,初始值為0;S2為啟動I2C匯流排后的下一個的狀態;tmpstate為狀態變數。停止信號也很容易照此設計,在此不再累贅。

而對於數據bit位的傳輸,根據I2C匯流排規範要求,在數據位的傳輸過程中,SDA信號在SCL信號為高電平期間不容許發生跳變,可用SCL高電平期間的前、后各1個脈衝來作為數據的建立時間和保持時間。由此得到如圖6所示的數據bit的傳輸設計。

圖6 I2C匯流排數據位reg的設計時序

傳輸‘reg'(代表“0”或“1”)的源程序代碼如下(假設為S4狀態):

if clk'event and clk='1' then

case cnt is

when 0 scl<='0';sda<='1';cnt:=cnt+1;

when 1 scl<='0';sda<=reg;cnt:=cnt+1;

when 2|3|4 scl<='1';cnt:=cnt+1;

when 5 scl<='0';cnt:=cnt+1;

when 6 sda<='1';cnt:=cnt+1;

when 7 cnt:=0;bitnum:=bitnum+1;tempstate<=S3;

when others=>tmpstate<=S0;

end case;

end if;

其中:reg為信號寄存器,可以直接與SDA線相連;bitnum為表示正在傳輸位元組的第幾個bit數據。這樣,在一個bit位數據傳輸的基礎上,使用一個8 bit的寄存器存儲要傳輸的位元組,很容易實現1位元組數據的傳輸。比如,在類型為std_logic_vector(7 downto 0)的寄存器ByteReg中存放著待發的數據,則傳輸1位元組數據相應的源程序代碼如下(假設為S3狀態):

if clk'event and clk='1'then

if bitnum>7 then

bitnum:=0;sendnum:=sendnum+1;

tmpstate<=S5;

else

ent:=0;reg<=ByteReg(bitnum);

tmpstate<=S4;

end if;

end if;

其中,S5用來等待來自SAA7111的應答信號。需要注意的是,在程序中要將SDA設置成inout類型的埠,在發送數據時是輸出埠,而在檢查SAA7111的ACK信號時,又是輸入埠。至於發送完一個位元組的數據后,要等待SAA7111返回的ACK信號,就是檢查來自SDA上的邏輯狀態是否為低電平信號“0”,在此不再累贅。

3.3 SAA7111寄存器的設置

對SAA7111進行初始化本質上是對SAA7111內部的每個寄存器的每一位寫入相應的數值,SAA7111的32個寄存器(00H~1FH)中有22個是可編程的,有些是可讀寄存器,保存著晶元和廠商的標識等信息,真正需要編程的只有19個,其中每個寄存器都有一個子地址。在對多個連續的寄存器進行操作時,寄存器地址有自動加1功能,所以確定第1個子地址后,可以不考慮地址的變化,順序寫入各寄存器的數值即可實現寄存器的連續設置。另外,在對SAA7111初始化時,還需要確定從地址,而從地址由硬體連接圖決定,當晶元引腳IICSA信號是低電平時,表示SAA7111的寫地址為48H。晶元的各個寄存器的意義可以參考SAA7111的文檔資料。

系統若設置為自動增益控制、625行50 Hz、PAL制式、YUV422的16位數字視頻信號輸出,則寄存器初始化值如表1所列。

| SubAddress | Data | SubAddress | Data |

| 00H | 00H | 01H | 00H |

| 02H | C1H | 03H | 33H |

| 04H | 00H | 05H | 00H |

| 06H | EBH | 07H | E0H |

| 08H | 88H | 09H | 01H |

| 0AH | 80H | 0BH | 47H |

| 0CH | 40H | 0DH | 00H |

| 0EH | 01H | 0FH | 00H |

| 10H | 40H | 11H | 1CH |

| 12H | 03H |

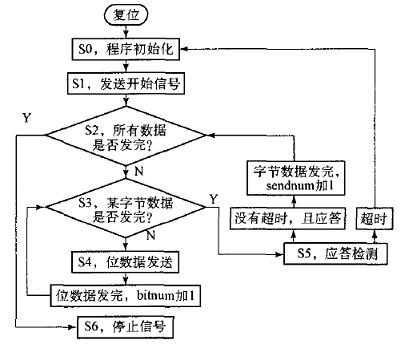

4 SAA7111初始化的實現

SAA7111的工作模式、輸入埠選擇、色彩控制等圖像採集的控制參數都是由其內部的寄存器決定,FPGA可通過SAA7111的I2C匯流排介面對其內部寄存器進行讀寫操作,具體的寫時序如圖7所示。

| Start Slave | address W | ACK-s | SubAddress W | ACK-s | Data(Nbytes) | ACK-s | Pause |

5 結束語

本方案引入SAA7111視頻輸入處理晶元,簡化了系統的硬體設計,通過FPGA對12C匯流排兩條傳輸線的時序模擬,完成了對視頻輸入處理晶元的控制,正確實現了對SAA7111的初始化。實驗結果表明該方案靈活、方便、可行,也很穩定。需要指出的是:由於FP.GA時鐘頻率過高,可利用分頻技術,使得I2C匯流排時鐘頻率在規範要求的範圍內,同時,在開發過程中要嚴格按照I2C匯流排的時序要求編寫相關代碼。

[admin via 研發互助社區 ] SAA7111初始化的FPGA設計已經有2025次圍觀

http://cocdig.com/docs/show-post-42990.html