1、 模擬的目的:

在軟體環境下,驗證電路的行為和設想中的是否一致。

2、 模擬的分類:

a) 功能模擬:在RTL層進行的模擬,其特點是不考慮構成電路的邏輯和門的時間延遲,著重考慮電路在理想環境下的行為和設計構想的一致性;

b) 時序模擬:又稱為後模擬,是在電路已經映射到特定的工藝環境后,將電路的路徑延遲和門延遲考慮進對電路行為的影響后,來比較電路的行為是否還能夠在一定條件下滿足設計構想。

3、 功能模擬的目的:

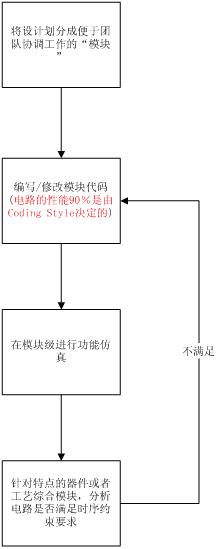

a) 設計出能工作的電路:因此功能模擬不是一個孤立的過程,其和綜合、時序分析等形成一個反饋工作過程,只有這個過程收斂,各個環節才有意義。而孤立的功能模擬通過是沒有意義的,如果在時序分析過程中發現時序不滿足需要更改代碼,則功能模擬必須從新進行。因此正確的工作流程是:

b)代碼排錯:功能模擬是代碼排錯的最重要的手段之一。

4、 modelsim的高級功能:Code Coverage

a) 代碼覆蓋率是驗證激勵是否完備,檢驗代碼質量的一個重要手段。測試激勵的代碼覆蓋率至少要達到95%以上,才能基本認為代碼在邏輯上是通過質量控制的,才能進入綜合步驟;

b) 代碼覆蓋率是保證高質量代碼的必要條件,但卻不是充分條件。即便代碼行覆蓋和分支覆蓋都能夠達到100%,也不能肯定的說代碼已經得到100%的驗證。除非所有的分支覆蓋都能夠進行組合遍歷。

c) 在大的設計中,如果想通過一個激勵就驗證完一個設計或者模塊是不現實的。一方面是從邏輯功能上很難做到;另外一方面是因為如果在一個激勵中包括了各種情況,整個模擬過程的速度會隨著計算機內存的消耗而成線性下降,效率低下。

d) 通常的做法是每一個激勵只驗證電路功能的某個方面。整個電路的功能驗證由數個激勵共同完成。在這種驗證方法中代碼覆蓋率更顯重要,因為可以通過代碼覆蓋率來控制激勵對功能的覆蓋程度。

e) modelsim的Code coverage不但能記錄各個激勵對代碼的“行覆蓋”和“分支覆蓋”,而且能夠將各個激勵的覆蓋記錄進行合併,做到對覆蓋率的全面監測。

f) 演示。。。。。。。。。。。。。。。。。。。。。。。。

5、 Debussy:模擬輔助調試工具:

a) 看模擬波形無疑是代碼排錯的主要手段,在Modelsim中的波形窗口在大的模擬中有如下缺陷:a、只能顯示出在模擬前設置好的信號波形,如果在模擬完成後想觀察其他的信號,唯一的辦法就是添加需要觀察的信號從新開始模擬。b、波形只是簡單顯示,和代碼沒有對應和關聯關係,不能藉助波形直觀的調試代碼;c、如果觀察的信號太多,由於其是實時全信號顯示,在模擬時間較長后,模擬速度明顯減慢,屏幕的刷新速度也明顯減慢。

b) 這些缺點不單Modelsim有,其他的優秀模擬工具也有,而且歷史由來以久,因此很早人們就提出了“先轉儲后觀察調試”方法,在verilog語言中以$dumpXXX開頭的系統函數就是做波形轉儲用的。就是先將波形先存在文件中,等模擬結束后在調出來顯示觀察和調試。

c) 這種觀察功能很多EDA工具都有,並不足為奇;但Debussy的獨特之處在於,它不但能顯示波形,而且還能非常智能化的將波形中的任何一個變化和引起這個變化的RTL代碼聯繫起來,使代碼排錯的效率大幅度提高。在原來IC所的一個大型項目中,由於引進了Debussy,使調試效率至少提高了3倍。

d) 先介紹verilog語言中的轉儲系統函數。其實轉儲函數就是一種典型的文件操作函數,最為常用的為一下幾種:

i. $dumpfile(“filename.vcd”):打開一個文件準備轉儲波形數據;

ii. $dumpall:轉儲所有信號的波形數據;

iii. $dumpvars:轉儲層次信號;

iv. $dumpon:開始轉儲;

v. $dumooff:停止轉儲;

e) 演示Modelsim轉儲功能

f) 演示Debussy工具中的輔助調試功能;

6、 SDF反標註

a) SDF是一種標準延時格式文件,用於記錄綜合布線后電路的線延遲和門延遲信息。如果在模擬輸出的波形上疊加上這些信息,將使波形更接近實際。

b) 演示。。。。。。。。。。。。。。。。。。。。。。。。。。

c) 但是由於電路已經被綜合布線過,原來的RTL代碼的邏輯層次和代碼命名都已經發生變化,即便看到波形也很難直接對應到RTL代碼上,因此後模擬來確定電路是否符合要求的方法已經逐漸被新的方法所代替。另外還有后模擬速度緩慢也是一個主要原因。新的方法是:時序分析、靜態時序分析、形式驗證。

7、 一個重要的觀念:電路的性能取決於電路構思和Coding Style:

a) 經常有人說“不要用寫軟體的方法去寫硬體”,或者說“要用樸實無華的語言風格來寫代碼”,這些說法只是描述了事務的表明現象,並沒有真正指出問題的真正癥結所在;

b) RTL描述語言,雖然是一種語言,但它是描述RTL的語言,所以其著眼點是電路實現而非邏輯推理;RTL就是電路在寄存器層的一種表現,雖然已經不像門級那樣具體,但也沒有抽象到邏輯層。

c) 因此寫代碼的真正正確的方法是:在大腦中構思出電路的結構,然後用代碼把它點滴不漏的表現出來,而不是先寫一些只是邏輯上行得通的代碼等待工具幫你綜合成能實現的電路。工具永遠只能做繁重而低級的工作,至少要比人的工作低級,這是未來幾百年內不會改變的公理。因此如果你的電路性能不好,說明你對如何實現電路還沒有清晰的思路。

d) 不要只使像通過提高器件的速度等級來使你的電路達到要求,恰恰相反,正確的方法是:如果你的電路在第一次綜合后已經有80%的路徑滿足時間要求了,那麼就不要想著用更快的器件,而應該考慮改變你的電路拓撲結構和設計構架,來使另外的20%逐漸達到要求。

[admin via 研發互助社區 ] EDA模擬已經有2286次圍觀

http://cocdig.com/docs/show-post-42976.html