1) 打開一個工程文件。

2) 打開Settings設置欄,選擇EDA Tools Settings下的Simulation欄。在右邊出現的設置欄中將“Tool name”的下拉菜單選擇“ModelSim(Verilog)”(如果工程用VHDL語言實現,則可以選擇“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的專用版本,則可以選擇“ModelSim-Altera(Verilog)”或“ModelSim-Altera(VHDL)”)。

另外在設置欄中還有其他的核選框。

3) 點擊

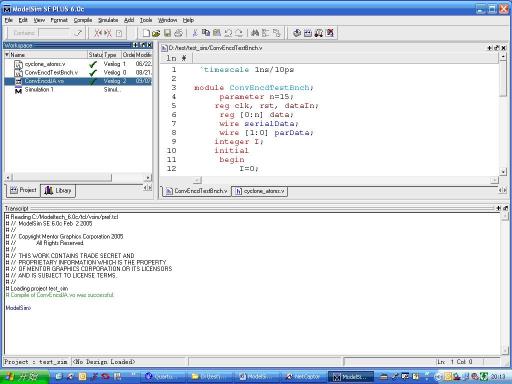

4) 打開ModelSim軟體(或者在Quartus下“Settings->EDA Tools Setting->Simulation”出現的設置欄中選中“Run this tool automatically after compilation”,直接從Quartus下調用ModelSim軟體),可以在當前工程目錄下新建一個Project。在Project標籤欄內點擊右鍵,出現在快捷菜單中選擇“Add to Project->Existing File…”。加入當前工程目錄的“\Simulation\ModelSim\”路徑下的.vo文件、TestBench文件和對應當前工程所選擇器件的網表文件。

比如:當前工程選擇的器件是Cyclone系列,Quartus安裝目錄在“C:\altera”路徑下。因此需要在“C:\altera\quartus50\eda\sim_lib”路徑下找到“cyclone_atom.v”的網表文件導入到ModelSim下的Project。如果是其他器件亦是如此,只要在此目錄下找到對應有“_atom”後綴的.v文件。當然整個大前提是ModelSim SE版本已經加入了Alterta的模擬庫,不過ModelSim-Altera版本就不會存在這樣的問題。

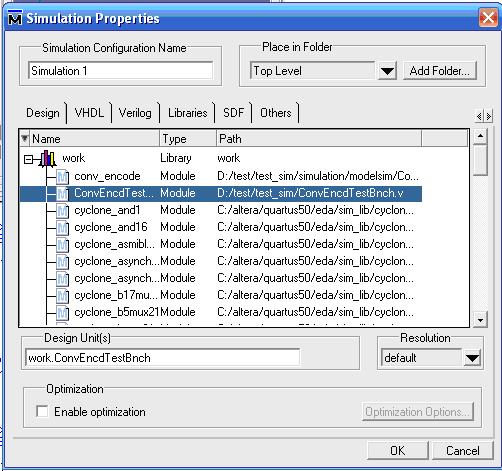

5) 在出現的Project標籤欄的快捷菜單中選擇“Add to Project->Simulation Configuration”,會出現如上圖所示的名為“Simulation1”的模擬配置。右鍵點擊選擇“Properties”,彈出的“Simulation Properties”對話框中有幾個標籤欄。

在“Design”標籤欄內需要選擇模擬的文件,也就是TestBench文件。

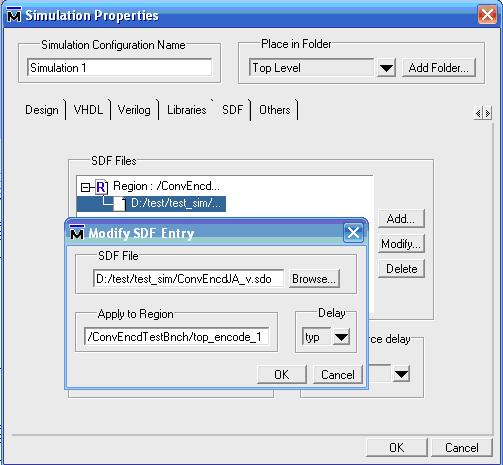

在“SDF”標籤欄內需要選擇包含延遲信息的文件,即Quartus下生成的.sdo文件。這裡建議將.sdo文件與ModelSim的工程文件(.mpf文件)放在同一個目錄下,不然ModelSim會報類似無法讀取.sdo文件的錯誤。當加入.sdo文件時,需要在如下圖所示的“Apply to Region”的編輯框內填寫延遲信息文件作用的區域。

舉個例子來說明:

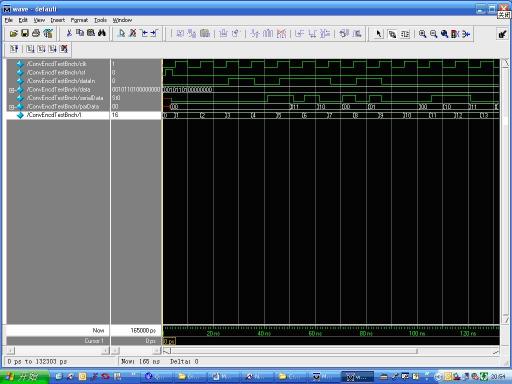

6) 右鍵點擊名為“Simulation1”的模擬配置,快捷菜單中選擇“Execute”命令,執行模擬。

7) 指定延時文件sdo 路徑時,特別注意“域”的指定,否則用戶會在timing 模擬中報load error “can’t find instance file”. 指定的域可以從sim標籤頁查看sim 的top 層,或要模擬的對象。另外,時序模擬時,一定要記住要把頂層top.v 用 top.vo 替換。同時要確保預編譯的庫中每個庫的名字必需遵循altera的要求,比如:cylcone 的device 庫必需命名為cycclone, maxii 的device命名為maxii, flex10Ke 和acex1K 都命名為flex10Ke,詳細查看文檔附件。Simulation.pdf

8) 提供一個testbench 的模板。

利用ModelSim SE6.0C實現功能模擬

功能模擬流程比較簡單,一般不會出現什麼問題,這裡不再多述。

[admin via 研發互助社區 ] 利用ModelSim SE6.0C實現時序模擬已經有4643次圍觀

http://cocdig.com/docs/show-post-43248.html