DS1302中文資料

DS1302 是美國DALLAS公司推出的一種高性能、低功耗、帶RAM的實時時鐘電路,它可以對年、月、日、周日、時、分、秒進行計時,具有閏年補償功能,工作電壓為2.5V~5.5V。採用三線介面與CPU進行同步通信,並可採用突發方式一次傳送多個位元組的時鐘信號或RAM數據。DS1302內部有一個31×8的用於臨時性存放數據的RAM寄存器。DS1302是DS1202的升級產品,與DS1202兼容,但增加了主電源/後背電源雙電源引腳,同時提供了對後背電源進行涓細電流充電的能力。

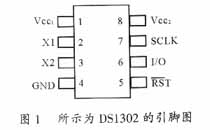

2.1 引腳功能及結構

圖1示出DS1302的引腳排列,其中Vcc1為後備電源,VCC2為主電源。在主電源關閉的情況下,也能保持時鐘的連續運行。DS1302由Vcc1或Vcc2兩者中的較大者供電。當Vcc2大於Vcc1+0.2V時,Vcc2給DS1302供電。當Vcc2小於Vcc1時,DS1302由Vcc1供電。X1和X2是振蕩源,外接32.768kHz晶振。RST是複位/片選線,通過把RST輸入驅動置高電平來啟動所有的數據傳送。RST輸入有兩種功能:首先,RST接通控制邏輯,允許地址/命令序列送入移位寄存器;其次,RST提供終止單位元組或多位元組數據的傳送手段。當RST為高電平時,所有的數據傳送被初始化,允許對DS1302進行操作。如果在傳送過程中RST置為低電平,則會終止此次數據傳送,I/O引腳變為高阻態。上電運行時,在Vcc≥2.5V之前,RST必須保持低電平。只有在SCLK為低電平時,才能將RST置為高電平。I/O為串列數據輸入輸出端(雙向),後面有詳細說明。SCLK始終是輸入端。

2.2 DS1302的控制位元組

DS1302 的控制字如圖2所示。控制位元組的最高有效位(位7)必須是邏輯1,如果它為0,則不能把數據寫入DS1302中,位6如果為0,則表示存取日曆時鐘數據,為1表示存取RAM數據;位5至位1指示操作單元的地址;最低有效位(位0)如為0表示要進行寫操作,為1表示進行讀操作,控制位元組總是從最低位開始輸出。

2.3 數據輸入輸出(I/O)

在控制指令字輸入后的下一個SCLK時鐘的上升沿時,數據被寫入DS1302,數據輸入從低位即位0開始。同樣,在緊跟8位的控制指令字后的下一個SCLK脈衝的下降沿讀出DS1302的數據,讀出數據時從低位0位到高位7。

2.4 DS1302的寄存器

DS1302有12個寄存器,其中有7個寄存器與日曆、時鐘相關,存放的數據位為BCD碼形式,其日曆、時間寄存器及其控制字見表1。

此外,DS1302 還有年份寄存器、控制寄存器、充電寄存器、時鐘突發寄存器及與RAM相關的寄存器等。時鐘突發寄存器可一次性順序讀寫除充電寄存器外的所有寄存器內容。 DS1302與RAM相關的寄存器分為兩類:一類是單個RAM單元,共31個,每個單元組態為一個8位的位元組,其命令控制字為C0H~FDH,其中奇數為讀操作,偶數為寫操作;另一類為突發方式下的RAM寄存器,此方式下可一次性讀寫所有的RAM的31個位元組,命令控制字為FEH(寫)、FFH(讀)。

3 DS1302實時顯示時間的軟硬體

DS1302與CPU的連接需要三條線,即SCLK(7)、I/O(6)、RST(5)。圖3示出DS1302與89C2051的連接圖,其中,時鐘的顯示用LCD。

3.1 DS1302與CPU的連接

實際上,在調試程序時可以不加電容器,只加一個32.768kHz 的晶振即可。只是選擇晶振時,不同的晶振,誤差也較大。另外,還可以在上面的電路中加入DS18B20,同時顯示實時溫度。只要佔用CPU一個口線即可。 LCD還可以換成LED,還可以使用北京衛信傑科技發展有限公司生產的10位多功能8段液晶顯示模塊LCM101,內含看門狗(WDT)/時鐘發生器及兩種頻率的蜂鳴器驅動電路,並有內置顯示RAM,可顯示任意欄位筆劃,具有3-4線串列介面,可與任何單片機、IC介面。功耗低,顯示狀態時電流為2μA (典型值),省電模式時小於1μA,工作電壓為2.4V~3.3V,顯示清晰。

[admin via 研發互助社區 ] 實時時鐘晶元DS1302中文資已經有3315次圍觀

http://cocdig.com/docs/show-post-38913.html