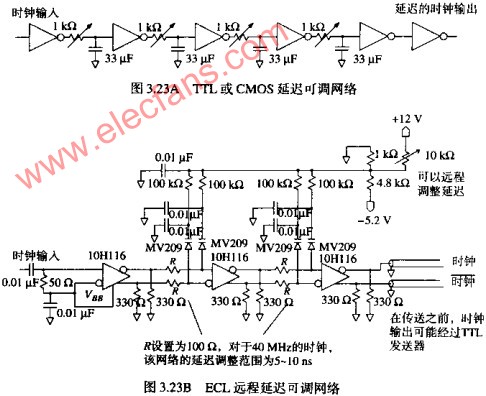

| 圖3.23所示的電路,是一個16進位的反相器,用於產生30~160NS的延遲。每一級的延遲時間是5~35NS,具體數值由可變電阻的值決定。每一級的延遲時間不應該超過時鐘周期的12%,以保重穩定工作。

通過調整延遲級數(2或4)並平均地調整每級電路的電阻(最好用排電阻),可以調整電路的占空比,使之到達一個最小值。在信號重新進入到系統之前,在電路的末端最好至少用一個反相器來對信號進行整形。

圖3.23A所示電路的缺點是信號必須經過電位器。對於調整系統,這意味著電位器必須非常小,並且在物理位置上離電路很近。圖3.23B所示的電路通過使用變容二極體的方法,解決了這個問題。變容二極體指的是其電容會隨著偏置電壓的變化而變化。圖3.23B所示電路的工作頻率遠遠高於圖3.23A所示的電路。

圖3.23B所示電路的每一級電路延遲時間都在2.5~5NS之間。該電路通過變容二極體MV209組成RC網路來調整相移。電路的級聯使得延遲時間的可調範圍擴大。圖3.23B是兩級電路,基延遲時間是5~10NS。

這個電路的設計頻率是40MHZ,如果工作在其他頻率,可以重新選擇R值:

為保征更高的穩定性,應該給這個可變延遲電路提供獨立的穩壓電源,並使電源的溫度保持恆定。

採用兩個電路中的任何一個,兩路信號都應取自同一個時鐘源,其中一路信號(時鐘A)通過可調延遲網路,另一路信號(時鐘B)通過固定長度的同軸電纜直接連接到匯流排。所用同軸電纜的阻貳要與匯流排原來的阻貳匹配。選擇同軸電纜的長度,使得可調延遲調整到中間值時,輸出的兩路時鐘信號的時序相匹配。 |