介紹有關數字電路設計盲點的內容,將分別針對Tinning、數據傳輸、消耗電流、HDL編寫等項目,輔以實例進行現象、原因分析以及對策探討。首先要介紹的是二進位計數器(Binary Counter)的設計。

有關Tinning的設計盲點

【二進位計數器】

二進位計數器經常被用來作外部輸入脈衝的同步化,此外計數器的輸出可負載(Load)到計數器本身,如果某種原因使得同步信號消失,可因為二進位計數器持續維持輸出Tinning,直到同步信號恢復正常再度取得同步為止,而且二進位計數器具有抗噪訊特性,所以是種廣被使用的電路Block。

※現象

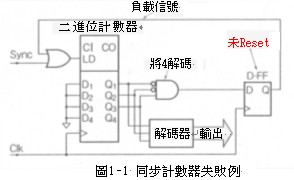

圖1-1是典型的二進位計數器電路,該電路是將0~5計數(Count),將6 Counter,不過由於某種原因使得同步信號與計數器(Counter)的輸出Tinning產生偏差,就會像產生如圖1-2所示的電路輸出持續偏差現象。

※原因分析

Flip Flop可keep已負載於二進位計數器LD的信號,因此若是忘記將「Flip Flop」Reset就會發生上述現象。為了符合設計規格因此利用圖1-3的二進位計數器輸出,不過由於圖1-1的電路,負載之前已將Tinning解碼(Decoder),並用D Flip Flop將該信號延遲一位(Bit)作成Load Tinning,因此某種原因使得同步信號與後段Flip Flop判定(Assert)Tinning延遲一位時,Tinning就會持續維持輸出偏差狀態。

※對策

根據電路Block的動作特性進行延遲計算,通常設計上不會有任何問題,因此採用如圖1-4所示的對策,如果因為負載信號的傳輸延遲造成延遲(delay),?需在圖1-4後面的D Flip Flop作Load就可解決上述問題。

圖1-1的電路原先是與圖1-3的電路相同,不過可能是進行Bread Board評鑒測試時發生解碼錯誤(miss),或者是負載信號傳輸的Line Delay無法滿足Set Up與Hold Tinning,因此插入D Flip Flop作Careless Miss對策。

【夾雜延遲無法提高Clock頻率】

※現象

這是經常發生的典型失敗設計實例,主要原因是計數器的Illegal State對策不當造成Clock頻率無法提高。在理論合成階段理論壓縮的PLD,有許多情況雖然不致構成障礙,然而實際上卻潛伏許多無法釐清盲點。圖2-1是十進位計數器設計實例,圖中的3至8 Line Decoder相當於74137的TTL Micro。

※原因分析

如上所述Clock頻率無法提高,主要原因是不當的Illegal State對策所造成。由於Illegal State對策上因為某種因,使得必要的Counter以外的值插入State,為了順利回復原正常狀態因此設置Illegal State,不過該對策卻會壓迫動作性能,造成本末倒置的反效果。

※對策

將Illegal State對策降至最小範圍,根據State Machine的情況充分檢討,設法使Clock數能回復原正常狀態,且不會產生其它問題。尤其是二進位計數器(Binary Counter),可以應用過去Disc Lead IC設計手法,簡化Illegal Sta te的Decoder。圖2-2是根據上述方式設計的電路圖,如圖所示Illegal State(此時為Ah以上)的Decoder是由負載條件決定,並刻意使Flip Flop的輸出變成1,再使負載條件能完全成立進行Decoder(此時為Bh,Dh,Fh),進而使電路恢復正常狀態。

【計數器切換造成分佈不均】

※現象

為製作時間分析儀因此在輸入端分別設置可儲存檢測中的數據的計數器,以及可將數據記憶至Memory的計數器(Counter),不過由於計數器產生分佈不均現象,所以無法正確檢測。時間分析儀又稱為「Multi Channel Analyzer」,它的主要功能是將時間分割作信號分類。圖3-1是2頻時間分析儀的Counter Channel切換電路,圖中的InO Switch是用來作初期化,圖中的下半段是產生頻道切換時間的電路,本電路圖是美國Beige Bag Software公司設計的 Spice A-D 2000 Versi on3.0.2。Sig主要用意是希望用時間分析儀檢測的脈衝,Out1是區分成Counter U6脈衝,它是用信號Sel進行區分,當Sel為「H」時利用計數器(Count er)U4計數(Count),若是「L」時則利用計數器(Counter)U6計數(Count)。此外脈衝在區分成U4時會讀取U6的數據,脈衝在區分成U6(Out3)時會讀取U4(Out2)的數據(點陣圖標)。U9與U10在切換計數器(Counter)時會將U4與U6清除(Clear)。此外從計數器讀取數據後會作清除動作,因此利用U13、U16、U14產生Tinning信號。

※原因分析

輸入至Counter Clock的Selector作非同步切換,造成選擇(Selector)切換與Coun ter的頻率特性同時出現,如圖3-2所示更惡劣的情況是通過切換時的切換脈衝被分斷成Out 1與Out2,形成雙重計數(Double Count)現象,即使使用正確的時間選擇(Selector)做切換,都無法解決上述雙重計數的問題。

圖3-2 圖3-1電路的Time Chart

※對策

由於上述電路是以Selector作切換,所以沒有簡易的對策可供參考,必需將被測信號與系列Clock同步化(圖3-3),同時Counter也需使用同步Type,並將Counter改成一個,使頻道(Channel)切換時前頻道的計數數據(Count Data)能被Latch同時還能清除Counter。由圖3-3可知它是利用Master Clock的Mck使U3、U4、U12、U14同步動作,並利用U3、U4、U12、U14輸出的的結果,使得Mck也作能同步動作。在被測Sig的脈衝,U2的Q一旦變成H時,與Mck同步化的Out 0就成為H,在此同時U3對Out 0反轉,利用輸出Q將U2清除,其結果使得Out 0對Sig的站立發生反應,輸出脈衝信號Out 0,信號與Mck同步化而且可使Clock成為H,如此便可在Mast er Clock獲得同步的被測信號Out 0,因此用U4將信號Out 0 Counter,進而獲得輸出Out 2,隨著時間切換,利用脈衝Sel可以獲得時間內的計數結果,同時還可清除(Clear)U,,並開始下個檢測動作。不過必需注意的是Clear若有Out 0時會將它作1的初期化。雖然檢測脈衝在同步化后,?檢測站立部分並將它計數(Coun t),然而實際上並非?是單純的同步化,而是藉由Flip Flop的Clock的輸入,使得幅寬狹窄的脈衝也無法遺漏,不過作業上存有Dead Time,因此若是連續性的幅寬狹窄脈衝不斷出現時,上述方法就不適用,換句話說被測信號的脈衝幅寬必需是Master Clock的兩倍以上。

如圖3-4所示的Tinning,切換時的Data Latch與Clear是利用Mast Clock Mck下降執行,所以不會影響檢測動作。Tinning除了Counter之外還具有Latch成份,因此會在下個頻道檢測中記錄(Memory)上個頻道的數據並列入計算範圍,如此一來理論上頻道之間就無任何不協調,此外由於可檢測的頻率受到限制,因此可以進行正確的量測動作。

[admin via 研發互助社區 ] 數字電路設計盲點實例與對策已經有2658次圍觀

http://cocdig.com/docs/show-post-43095.html