1 引言

FIFO(First IN First Out)先進先出電路是一種實現數據先進先出的存儲器件,普遍用作數據緩衝器。FIFO的基本單元是寄存器,作為存儲器件,FIFO的存儲能力是由其內部定義的存儲寄存器的數量決定。

FIFO通常是雙埠的存儲器,其中一個埠用於寫入數據,而另一個埠用於讀出數據。可以同時對存儲器字存儲單元進行寫入和讀出操作。它的數據吞吐率是普通RAM的兩倍。FIFO型的存儲器不需要由地址來存取數據。需要由另外的信號線(或標誌)來指明存儲器的內容狀態。

在現代數字系統設計中,FPGA(現場可編程門陣列)器件憑藉其靈活、方便、資源豐富的優勢在很多領域得到了廣泛應用。隨著其片內存儲資源的增加,把FIFO器件集成到其中是一種方便地代替專用晶元的實現方法。根據非同步邏輯的設計方法,引入乒乓操作的設計技巧,給出了一種新穎的非同步FIFO設計方案,解決FPGA多時鐘系統中不同時鐘域傳輸數據的問題。

2 非同步FIFO的設計與實現

2.1 通用非同步FIFO的基本結構

在現代的集成電路晶元中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘。多時鐘域帶來的一個問題就是,如何設計非同步時鐘之間的介面電路。非同步FIFO是解決這個問題一種簡便、快捷的解決方案。使用非同步FIFO可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據。在網路介面、圖像處理等方面,非同步FIFO得到了廣泛的應用。

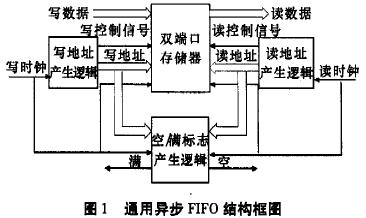

非同步FIFO常用於存儲、緩衝在兩個非同步時鐘之間的數據傳輸。在非同步電路中,由於時鐘之間周期和相位完全獨立,因而數據的丟失概率不為零。如何設計一個高可靠性、高速的非同步FIFO電路便成為一個難點。下面將介紹解決這一問題的一種方法,其結構框圖如圖1所示。

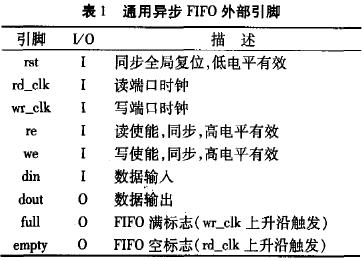

本系統FPGA內部FIFO的存儲介質是一塊雙埠的RAM,具有兩個獨立的讀寫時鐘,整個系統也分為兩個完全獨立的時鐘域——讀時鐘域和寫時間域。FIFO的控制邏輯執行所有的讀寫指針管理,產生各種狀態標誌。在寫時鐘域部分,由寫地址產生邏輯產生寫控制信號和寫地址;讀時鐘域部分由讀地址產生邏輯產生讀控制信號和讀地址。在空/滿標誌產生部分,由讀寫地址相互比較產生空/滿標誌。本設計的外部引腳如表1所示。

這種FIFO設計當中有兩個難點:一是如何正確地設計空、滿信號的控制電路;二是如何同步非同步信號,使觸發器不產生亞穩態。下一小節將具體闡述解決方法。

2.2 FIFO的讀寫控制

空/滿標誌的產生是FIFO的核心部分,如何正確設計這部分邏輯,直接影響到FIFO的性能。空/滿標誌產生的原則是:寫滿不溢出,讀空不多讀。即無論在什麼時候,都不應出現讀寫地址同時對一個存儲器地址操作的情況。在讀寫地址相等或相差一個或多個地址的時候,滿標誌應該有效,表示此時FIFO已滿。在滿信號有效時若繼續向FIFO寫數據,應根據設計的要求對數據作保持或拋棄重發處理,空標誌的產生也是如此。

最直接的做法是,採用讀寫地址相比較來產生空滿標誌。當讀寫地址的差值等於一個預設值的時候,空/滿信號被置位。這種實現方法邏輯簡單,但它是減法器形成的一個比較大的組合邏輯,因而限制了FIFO的速度。所以,一般只採用相等不相等的比較邏輯,避免使用減法器。即:

空標誌<=(|寫地址-讀地址|<=預定值)AND(寫地址超前讀地址)

滿標誌<=(|寫地址-讀地址|<=預定值)AND(讀地址超前寫地址)

另一種方法是,比較器只對讀寫地址比較是否相等。在讀寫地址相等的時候有兩種情況:滿或者空。所以,附加了一個并行的區間判斷邏輯來指示是空還是滿。這個區間判斷邏輯將整個地址空間分為幾個部分,以指示讀寫地址的相對位置。這種做法提高了整個電路的速度,但是也有其缺點。主要是直接採用讀寫地址等於不等於的比較邏輯來進行空/滿標誌的判斷,可以帶來誤判。

將讀寫指針位寬分別定義為:rp[aw:0]和wp[aw:0],其中rp[aw]和wp[aw]為最高位進位位,rp[aw-1:0]和wp[aw-1:0]分別表示讀寫指針定址的地址。當讀寫指針每次從初始地址處讀寫到最後一位地址位時,均需向最高位rp[aw]和wp[aw]進位。因為先有寫才能有讀,所以當wp[aw-1:0]=rp[aw-1:0]時,只要判斷wp[aw]與rp[aw]是否相等就可以知道是寫指針追趕上讀指針寫滿了(wp[aw]!=rp[aw]),還是讀指針追趕上寫指針讀空了(wp[aw]=rp[aw])。rp_pl1和wp_pl1分別定義為讀寫指針的下一個地址,而且為了在判斷空滿標誌時對讀寫指針進行同步比較,設計中定義了與rd_clk同步的寫指針wp_s以及與wr_clk同步的讀指針rp_s,這兩個信號可以通過同步邏輯來實現。

2.3 跨時鐘域設計帶來的亞穩態問題

亞穩態(Metastability)是指觸發器信號和時鐘不滿足建立時間/保持時間(setup/hold)的基本要求,觸發器的輸出端將會達到一個不確定的狀態。當一個觸發器進入亞穩態時,既無法預測它的輸出電平,也無法預測其輸出何時才能穩定在某個正確的電平上。在這期間,觸發器輸出一些中間級電平,或者可能處于振盪狀態,並且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。當一個信號跨越某個時鐘域時,接收該信號的電路需要對其進行同步,用以防止前級存儲單元(觸發器)的亞穩態在新的時鐘域里傳播蔓延。

在本系統中內部工作時鐘有兩個互相非同步的不同頻率時鐘,並且在兩個時鐘域的邏輯模塊之間有許多控制信號需要傳遞,亞穩態是不可避免的,但是下面的設計可以將其發生的概率降低到一個可以接受的程度。

①對寫地址/讀地址採用格雷碼。由實踐可知,同步多個非同步輸入信號出現亞穩態的概率遠遠大於同步一個非同步信號的概率。對多個觸發器的輸出所組成的寫地址/讀地址可以採用格雷碼。由於格雷碼每次只變化一位,採用格雷碼可以有效地減少亞穩態的產生。

②採用兩極觸發器來同步非同步輸入信號。信號同步的目的是防止新時鐘域中第一級觸發器的亞穩態信號對下級邏輯造成影響。兩級寄存器的同步化處理單元由兩個觸發器串聯而成,中問沒有其它組合電路。這種設計可以保證後面的觸發器獲得前一個觸發器輸出時,前一個觸發器已退出了亞穩態,並且輸出已穩定。但是,這種方法同時帶來了對輸入信號的一級延時,需要在設計時鐘的時候加以注意。

雖然亞穩態是不可避免地,但是採用格雷碼可以有效地減少亞穩態的產生。由前面的分析可以看出,由地址直接相減和將地址相互比較產生空/滿標誌都不可取。如何簡單地進行直接比較,又不提高邏輯的複雜程度呢?對地址加延時可以做到這一點。

設讀地址為rp_bin,用讀地址產生讀地址格雷碼rp_grap_next,將rp_grap_next延一拍得到rp_grap,再將rp_grap延一拍得到rp_grap_x。在絕對時間上,rp_grap_next、rp_grap、rp_grap_x先後從大到小,相差一個地址,如圖2所示。寫地址也與此類似,即:wp_grap_next、wp_grap、wp_grap_x。利用這6個地址進行比較,同時加上讀寫使能,就能方便而靈活的產生空/滿標誌。

以空標誌empty產生為例,當讀寫格雷碼地址相等或者FIFO還剩下一個深度的字,並且正在不空的情況下執行讀操作,這時empty標誌設置為有效。即:empty<=(rp_gray==wp_gray)and(re== 1)或empty<=(rp_gray_next==wp_gray)and(we==1),同理可類推滿標誌的產生邏輯。

3 Verilog實現與模擬

本設計完成了一個完整的規格為256×8雙時鐘通用非同步FIFO的Verilog建模,並對該設計的編寫測試向量進行行為級模擬,模擬工具採用ModelSimSE6.0。圖3給出了整個電路的模擬時序圖。分析上面讀寫時序圖中各狀態變化和數據的傳輸情況,驗證各狀態信號時序正確,邏輯正確,功能模擬結果正確,整個的工作波形也符合設計要求。

圖3 雙口非同步FIFO讀寫模擬波形

最後,用Synplify7.6 Pro軟體進行綜合,器件為Altera的EP1C6Q240C8。一般標誌產生電路(用減法器,設閾值)和基於格雷碼的標誌產生電路,設計結果性能指標對照表如表2所示。

由表2可知,帶區間指示邏輯設計的雙時鐘通用FIFO的特點是直接對讀寫指針地址進行比較,並通過輔助的區間指示來判斷FIFO的讀空與寫滿。這種方法正如前面所說的,因為避免了地址的減法比較,所以減少了邏輯的複雜度,提高了系統的速度,但是也容易出現一定的誤判斷現象,而且由於雙時鐘FIFO出現非同步的情況,容易產生亞穩態現象,這種方法亦不能很好地解決。我們可以通過設計格雷碼雙時鐘通用FIFO來較好地處理亞穩態的問題,提高了系統的穩定性。但是不可避免地,較之一般方式的FIFO來說,需要有更多的邏輯單元,需要用更長的數據傳輸時間。

4 總結

本文提出了一種新穎的用FPGA實現非同步FIFO並作為非同步時鐘域數據傳輸的介面電路的方法,特別詳述了空、滿信號的產生。按此方案設計的非同步FIFO的軟體模擬和硬體實現都已經通過了驗證,並應用到實際的電路。實踐證明用此方案設計的非同步FIFO具有性能穩定、空滿狀態標誌可靠等特點。

[admin via 研發互助社區 ] 一種基於格雷碼的非同步FIFO設計與實現已經有12717次圍觀

http://cocdig.com/docs/show-post-43091.html