一、配置Modelsim ISE的Xilinx的模擬庫

1、編譯模擬庫:

A、先將Modelsim安裝目錄C=Modeltech_6.2b下面的modelsim.ini改成存檔格式(取消只讀模式);

B、在DOS環境中,進入Xilinx的根目錄,然後依次進入bin,nt目錄;

C、運行compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。

注意:需要根據你安裝的modelsim目錄更改C:Modeltech_6.2b

然後就Ok了,就可以的ISE中啟動Modelsim進行所有的模擬了。

2、如何在Xilinx ISE中使用Modelsim ISE,Synplify進行綜合和模擬:

A、打開Xilinx ISE,新建一個Project;

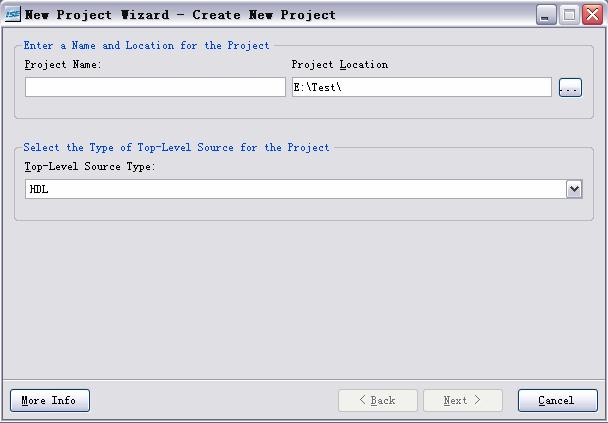

①、在菜單File中選擇“New Project”,彈出如下的對話框:

②、輸入Project名稱,並選擇好Project保存的路徑,然後下一步:

按照上邊的參數進行設置(針對於Spatan 3E的開發板),然後單擊下一步,進入到後面的界面:

③、單擊“New Source”按鈕,並按照下面的設置來操作:

④、參照下面的參數,進行設置,然後一直選擇默認選項,一直到完成。

最後生成的項目界面如下圖所示:

B、輸入代碼,然後用Synplify綜合:

①、參考代碼:

entity Count iS

Port(CLK :in STD_LOGIC;

RESET :in STD_LOGIC;

LOAD :in STD_LOGIC;

DATA IN:in STD_LOGIC_VECTOR(3 downto 0);

Qout :out STD_LOGIC_VECTOR(3 downto 0));

end Count;

architecture Behavioral of Count is

signal tmpCount:STD_LOGIC_VECTOR(3 downto 0);

begin

process(CLK,RESET,LOAD)

begin

if RESET='1' then

tmpCount<="0000";

else

if LOAD='1' then

tmpCount<=DATA_IN;

elsif CLK'event and CLK='1' then

tmpCount<=tmpCount+1;

end if;

end if;

end process;

Qout<=tmpCount:

end Behavioral;

②、雙擊Processes窗口裡面的“Synthesize-Synplify”進行綜合

③、在“Transcript”窗口中的可以看到綜合的信息。

C、時序模擬:

①、從菜單“Project”中選擇“New source”。按照下圖所示輸入,然後選擇下一步

②、在“Associate source”選擇需要進行時序模擬的HDL代碼,然後選擇下一步

③、在彈出的窗口“Initial Timing and Clock Wizard-Initialize Timing”中選擇默認的配置

④、當出現如下的界面后,你就可以進行時序模擬了^_^

⑤、在Sources選擇Behavioral Simulation,在Processes的ModelSim Simulator中雙擊下面的任何一個都可以進行模擬。區別就是一個在Xilinx ISE中進行,一個則在ModelSim界面中。

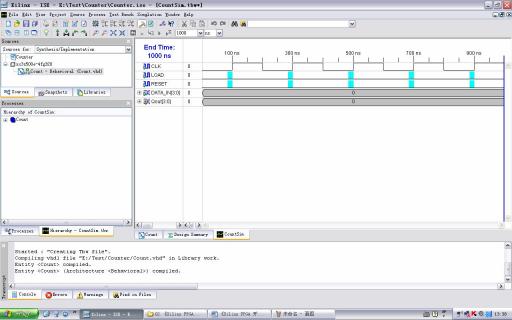

⑥、下圖是雙擊“Generate Expected Simulation Results”的效果

⑦、下圖是雙擊“Simulate Behavioral Model”的效果

⑧、接下來大家就可以寫代碼,然後模擬驗證了,^_^

[admin via 研發互助社區 ] Xilinx FPGA開發環境的配置已經有2637次圍觀

http://cocdig.com/docs/show-post-43068.html