電阻抗成像(Electrical Impedance Tomography,EIT)技術是一種廉價的無損傷探測技術,不使用放射源,對人體無害,可作為對患者進行長期、連續監護的醫學監護設備.

在醫學領域,考慮到患者的安全,激勵信號源的電流應小於5 mA;不同人體組織的阻抗隨頻率變化的特性不同,因此要求激勵信號源可以工作在單頻、多頻或掃頻模式下,頻率範圍為10 kHz~1MHz。激勵信號的波動應小於ADC(Analog to Digital Convertor)的1LSB(Least significant bit,最低有效位),即當數據採集系統採用12 bit ADC時,激勵信號源DAC(Digital to Analog Covertor)的精度應高於12 bit。目前,EIT硬體系統常採用兩種方法來構造正弦信號發生器。

(1)選擇具有片內波形表ROM 和DAC的DDS(Direct Digital Synthesizer,直接數字合成)集成晶元,通過相位累加器的輸出對存儲在ROM中正弦波的幅度值做查表運算,得到的數字量由DAC產生正弦波。DDS技術具有頻率、幅度和相位調節方便,輸出頻率範圍寬的特點。如AD7008,具有32 bit相位累加器、SIN/COS查找表和10 bitDAC,其信噪比為50 dB。

(2)組合電路或小規模的CPLD/FPGA結合外部DAC實現DDS的功能。其波形表可以修改,因而能產生任意波形的信號。

ROM 的容量限制了採樣點數,制約了信號源精度提高.本文採用先查表,並用泰勒級數對正弦波插值的方法,使輸出的幅度值不再局限於ROM 中存儲的數據,可有效的提高信號源精度。

1 系統設計

1.1 泰勒級數插值的原理

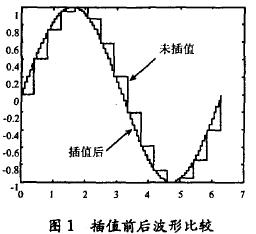

目前,FPGA晶元除了豐富的可編程邏輯資源外,還擴充了ASIC型乘法器等特殊功能模塊。泰勒級數插值正是利用了FPGA內的乘法器資源,採用先查表然後用泰勒級數插值的方法,通過流水線式運算在每個時鐘都得到一個插值數據,從而輸出的數據不再局限于波形表中的存儲的數據,使正弦波更加光滑,其原理如圖1。

ROM 中存儲了一個周期內N個等間隔的θi幅值sin(θi),對未存儲在ROM 中的θ,由泰勒級數插值得到,如式(1)所示。

sin(θ)≈ sin(θi)+ cos(θi)·(θ-θi)-1/2sin(θi)·(θ-θi)2 (1)

在FPGA中,通過流水線式的查表、乘加運算進行泰勒級數插值,各級運算互不影響,數據可隨時輸出。

1.2 硬體結構

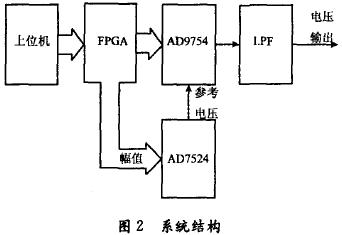

基於FPGA的信號源主要由三部分構成:FPGA,14 bit高速DAC AD9754及用於控制幅值的8bit DAC AD7524,如圖2所示。

上位機通過串口將信號的頻率、初始相位和幅值信息送至FPGA。FPGA輸出數字量由高速DAC轉換為正弦波;同時,通過輔助DAC控制幅值。輸出波形再經濾波電路濾除諧波分量,獲得需要的波形。

1.2.1 基於FPGA的DDS模塊

泰勒級數插值需要大量乘法運算,小規模CPLD/FPGA往往不提供專門的乘法器模塊.作者選擇的Xilinx公司XC3S200 FPGA晶元有12個ASIC型嵌入式18×18 bit二進位乘法器模塊。結構上,每個乘法器配備一個Block RAM,保證了數據處理的效率,可以實現18位有符號數的高速乘法運算。

DDS模塊採用Xilinx公司的IP核(Intellectual Property Core,知識產權核)在FPGA 內構造。IP核根據Xilinx的FPGA器件特點和結構設計,直接用Xilinx底層硬體原語描述,可充分發揮FPGA的功能,保證速度和可靠性。該DDS模塊最多支持16通道,各通道的頻率和初始相位可通過相位增量(PINC)或相位偏移量(POFF)分別控制;WE為高時,由DATA分別寫入POFF和PINC控制字。POFF和PINC與初始相位、輸出頻率的關係分別為(相位累加器為32位),

SINE和COSINE端分別輸出正弦和餘弦波。單通道DDS的ModelSim 6.0模擬波形如圖3所示。圖中,SINE與COSINE的相位相差90°,頻率可由WE和DATA寫入PINC控制。

1.2.2 數模轉換電路

人體電阻抗成像系統激勵信號源的頻率動態範圍較大,要求數模轉換電路有較高的無雜散動態範圍(SNFR)。系統選擇了14位的AD9754,其時鐘頻率為125 MHz,波形建立時間35 ns。當輸出頻率為5 MHz時,AD9754的SNFR為83 dBc。

激勵信號源應具有幅值調節功能。本文中,AD9754的參考電壓Vref由8位的輔助DAC(AD7524)提供,如圖4示。AD9754滿幅輸出電流為IOUTFS=32×Vref/Rset,其中Rset為定值限流電阻。通過AD7524可以做到激勵電流幅值256級可調,適應不同的測量對象和激勵方式。

為了使系統穩定的工作,可靠的時鐘是非常關鍵的。FPGA對時鐘進行倍頻/分頻、消抖后再提供給DAC,可以保證DAC的時鐘占空比為50%且不存在相位偏移。

1.3 多頻率成分信號源

IP核技術的本質特徵是功能模塊的可復用性。因此,不改動外部電路,即可產生多種頻率成分的波形。本文實現了具有三種頻率成分的信號源。在FPGA內把三個不同頻率DDS模塊的輸出相加,再進行數模轉換,即可得到具有三種頻率成分的波形。三個頻率分別為100 kHz,400 kHz和1 MHz,ModelSim模擬的波形如圖5所示。

1.4 上位機介面

本系統中,FPGA通過RS232介面與PC機通信,用VHDL語言編程在FPGA內實現UART(通用非同步收發器)模塊;UART通過MAX3232晶元轉換成RS232介面的電平標準與PC機通信。使用時,由上位機發送頻率、初始相位和幅值的控制字給FPGA,單頻信號源的頻率、初始相位和幅值分別用8位控制。這樣可用頻率數為256個;最低有效位可設定,當為6 kHz時,可用頻率為6×NkHz(N=0,1,……255);最高頻率為1530 kHz。DDS的初始相位由8位控制,可以為M×1.41°(M=0,1,……255);同樣,通過8位控制字實現幅值的256級可調。

2 結果

按以上方法設計的激勵信號源達到了預期的性能指標。將其特徵和相關性能與AD7008進行了比較,見表1。

| 項目 | 本信號源 | AD7008 |

| 時鐘 | 0-125MHz | 20或50MHz |

| DDS精度 | 20位 | 10位 |

| DAC精度 | 14位 | 10位 |

| 數據產生方式 | 先查表再插值 | 簡單查表 |

| 信噪比 | 78dB | 50dB |

| 可否多頻率 | 是 | 否 |

3 結論

綜上所述,本文設計並實現了一種基於FPGA的14位高精度激勵信號源,信噪比為78 dB;不需改動外圍電路,即可工作在單頻、多頻和掃頻模式下;頻率、初始相位及幅值調節方便,可以滿足不同激勵模式下人體電阻抗成像系統的需要。

[admin via 研發互助社區 ] 基於FPGA的電阻抗成像系統激勵信號源已經有2955次圍觀

http://cocdig.com/docs/show-post-43065.html